BATTERY PROTECTION IC FOR 3-SERIAL- OR 4-SERIAL-CELL PACK

Rev.5.0_01

S-8254A Series

Seiko Instruments Inc.

5

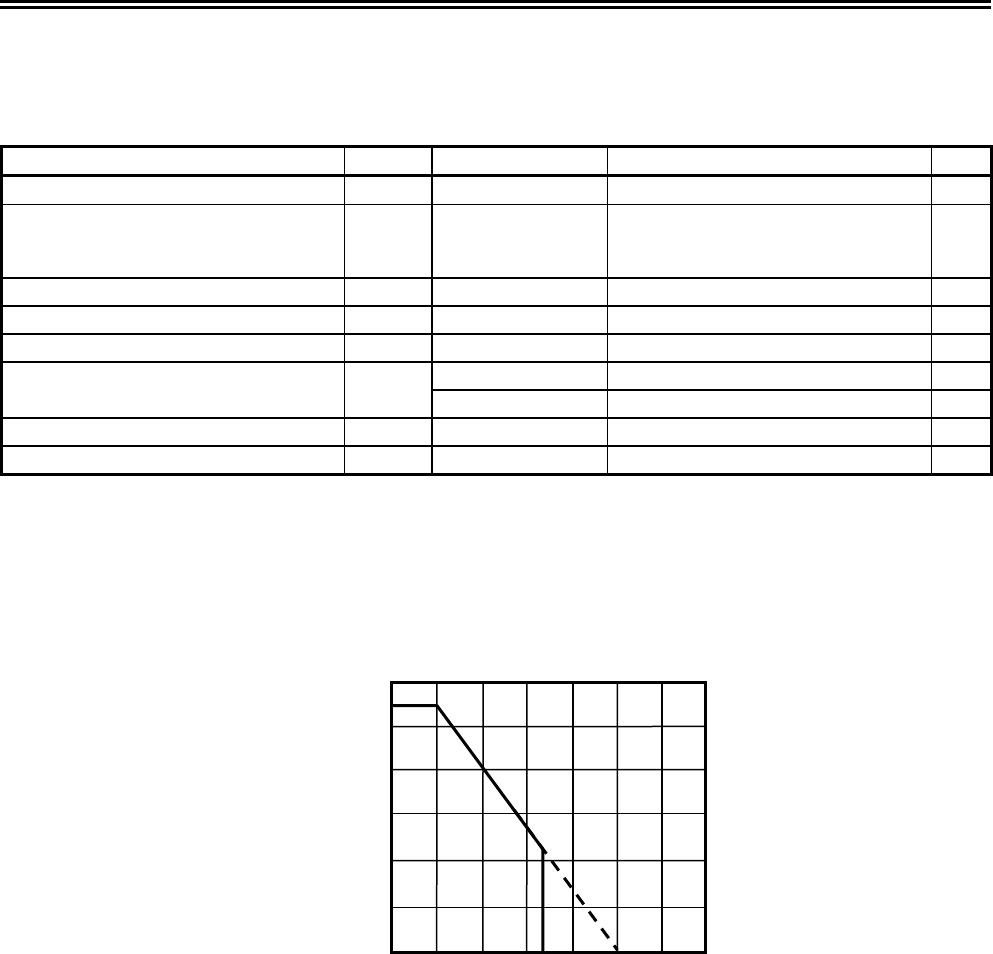

Pin Configuration

16-Pin TSSOP

Top view

8

7

6

5

3

2

4

1

11

16

9

10

12

14

15

13

COP

VMP

DOP

VINI

CDT

CCT

VSS

NC

VDD

VC1

VC2

VC3

VC4

CTL

SEL

NC

Figure 2

Table 2

Pin No. Symbol Description

1 COP FET gate connection pin for charge control (Nch open drain output)

2 VMP

Pin for voltage detection between VC1 and VMP (Pin for overcurrent 3

detection)

3 DOP FET gate connection pin for discharge control FET (CMOS output)

4 VINI

Pin for voltage detection between VSS and VINI (Pin for overcurrent detection

1,2)

5 CDT

Capacitor connection pin for delay for overdischarge detection, delay for

overcurrent detection 1

6 CCT Capacitor connection pin for delay for overcharge current

7 VSS

Input pin for negative power supply,

Connection pin for battery 4’s negative voltage

8 NC

*1

No connection

9 NC

*1

No connection

10 SEL

Pin for switching 3-series or 4-series cell

V

SS

level: 3-series cell, V

DD

level : 4-series cell

11 CTL Control of charge FET and discharge FET

12 VC4

Connection pin for battery 3’s negative voltage,

Connection pin for battery 4’s positive voltage

13 VC3

Connection pin for battery 2’s negative voltage,

Connection pin for battery 3’s positive voltage

14 VC2

Connection pin for battery 1’s negative voltage,

Connection pin for battery 2’s positive voltage

15 VC1 Connection pin for battery 1’s positive voltage

16 VDD

Input pin for positive power supply,

Connection pin for battery 1’s positive voltage

*1. The NC pin is electrically open. The NC pin can be connected to VDD or VSS.