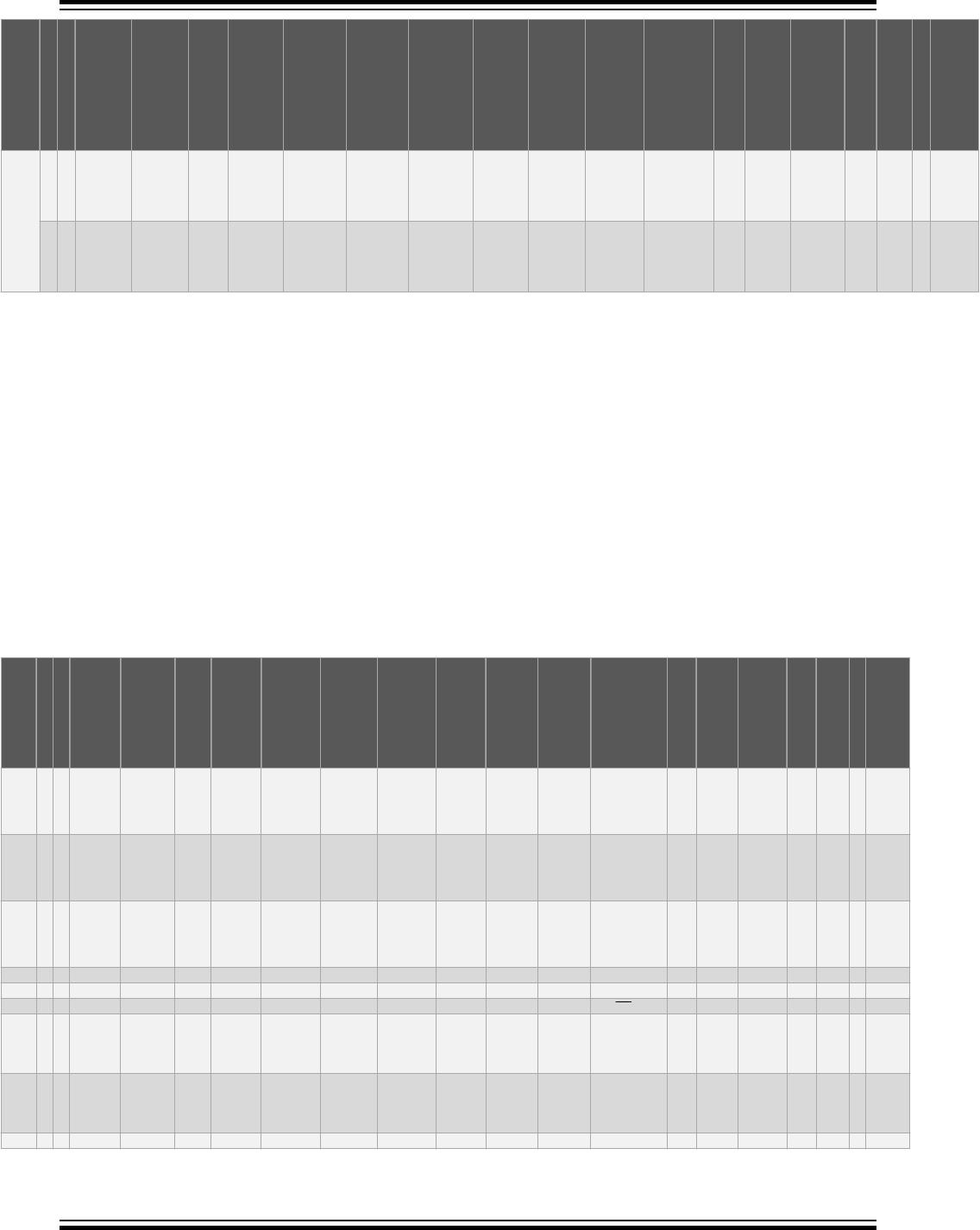

I/O

20-pin PDIP/SOIC/TSSOP

20-pin UQFN

ADC

Reference

Comparator

NCO

DAC

DSM

Timers

CCP

PWM

CWG

MSSP

ZCD

EUSART

CLC

CLKR

Interrupts

Pull-up

Basic

— — — — — — — — — CCP3OUT —

CWG1C

CWG2C

SCL1

(3)

SCL2

(3)

— TX1 CLC3OUT — — — —

— — — — — — — — — CCP4OUT —

CWG1D

CWG2D

SDA1

(3)

SDA2

(3)

— — CLC4OUT — — — —

Note:

1. This is a PPS re-mappable input signal. The input function may be moved from the default location

shown to one of several other PORTx pins.

2. All digital output signals shown in these rows are PPS re-mappable. These signals may be mapped to

output onto one of several PORTx pin options.

3. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the

same pin in both the PPS input and PPS output registers.

4. These pins are configured for I

2

C logic levels. PPS assignments to the other pins will operate, but input

logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I

2

C specific or

SMBUS input buffer thresholds.

5. MSSP2 is not available on the PIC16(L)F18424 or PIC16(L)F18444 devices.

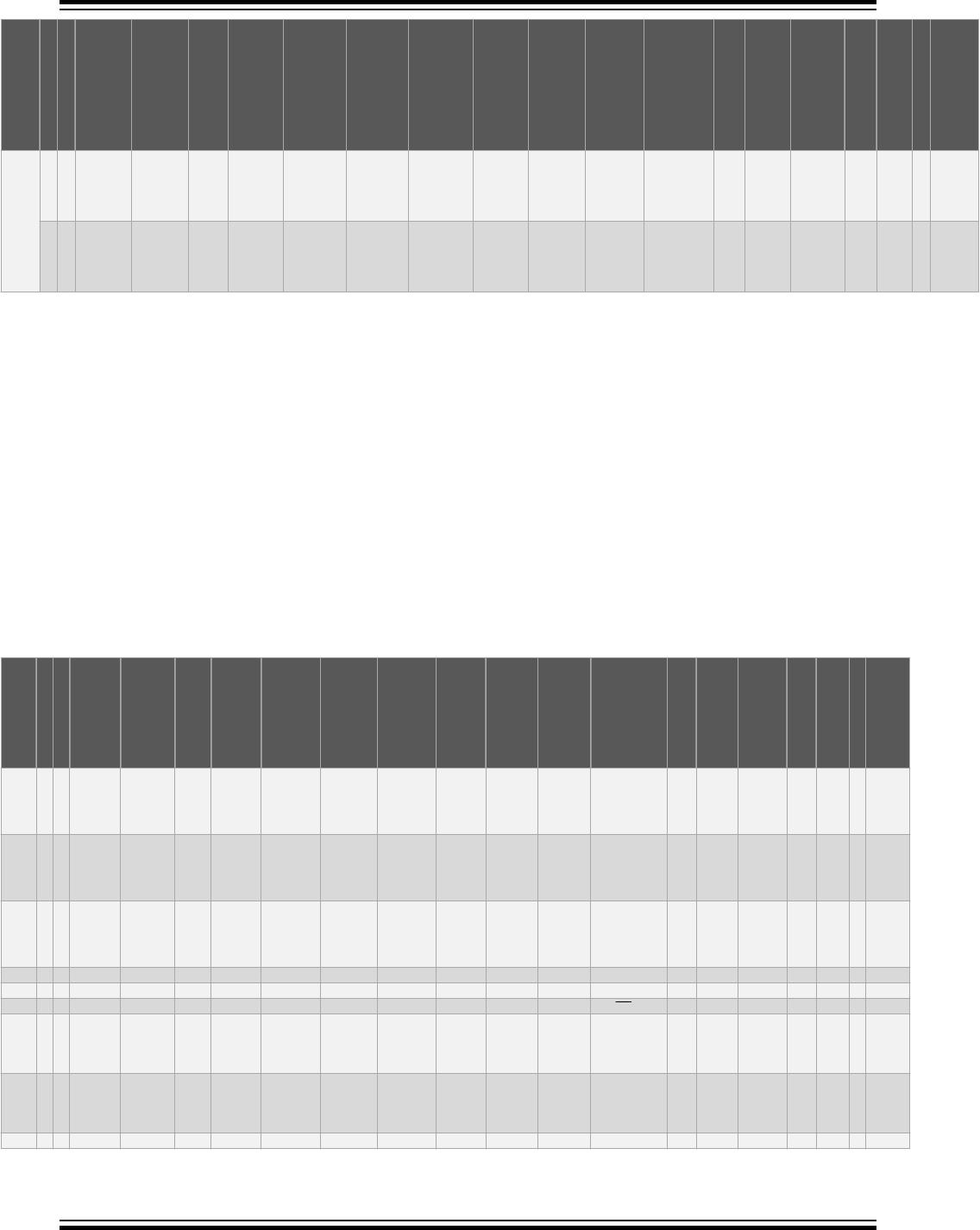

3 28-Pin Allocation Table

I/O

28-pin PDIP/SOIC/TSSOP

28-pin UQFN

ADC

Reference

Comparator

NCO

DAC

DSM

Timers

CCP

PWM

CWG

MSSP

ZCD

EUSART

CLC

CLKR

Interrupts

Pull-up

Basic

RA0 2 27 ANA0 —

C1IN0-

C2IN0-

— — — — — — — — — — CLCIN0

(1)

— IOCA0 Y —

RA1 3 28 ANA1 —

C1IN1-

C2IN1-

— — — — — — — — — — CLCIN1

(1)

— IOCA1 Y —

RA2 4 1 ANA2 ADCVREF-

C1IN0+

C2IN0+

—

DAC1VREF-

DAC1OUT1

— — — — — — — — — — IOCA2 Y —

RA3 5 2 ANA3 ADCVREF+ C1IN1+ — DAC1VREF+ MDCARL

(1)

— — — — — — — — — IOCA3 Y —

RA4 6 3 ANA4 — — — — MDCARH

(1)

T0CKI

(1)

CCP5IN

(1)

— — — — — — — IOCA4 Y —

RA5 7 4 ANA5 — — — — MDSRC

(1)

— — — — SS1

(1)

— — — — IOCA5 Y —

RA6 10 7 ANA6 — — — — — — — — — — — — — — IOCA6 Y

OSC2

CLKOUT

RA7 9 6 ANA7 — — — — — — — — — — — — — — IOCA7 Y

OSC1

CLKIN

RB0 21 18 ANB0 — C2IN1+ — — — — CCP4IN

(1)

— CWG1IN

(1)

— ZCD1 — — — IOCB0 Y INT0

(1)

PIC16(L)F184XX

© 2017 Microchip Technology Inc.

Product Brief

DS40001894B-page 12