Document Number: 001-98295 Rev. *L Page 10 of 19

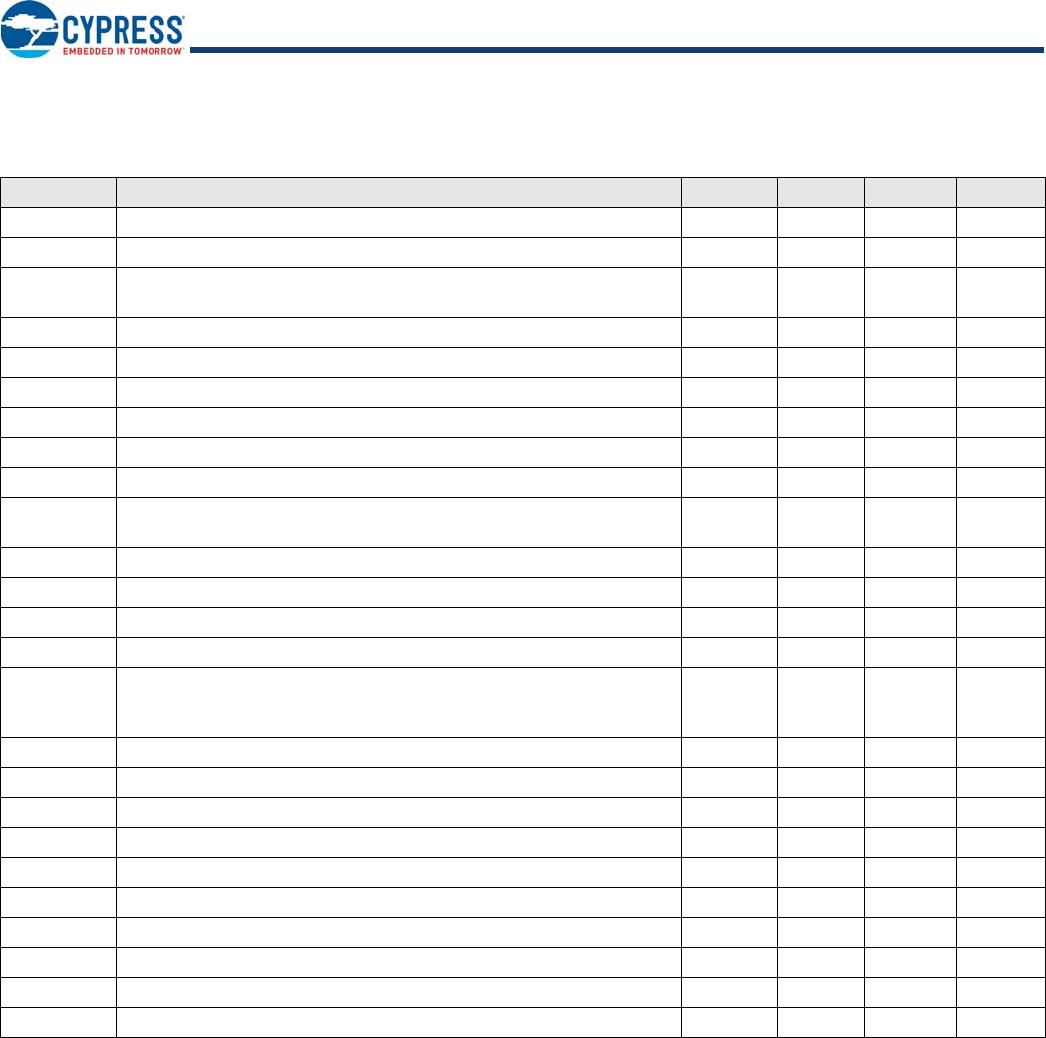

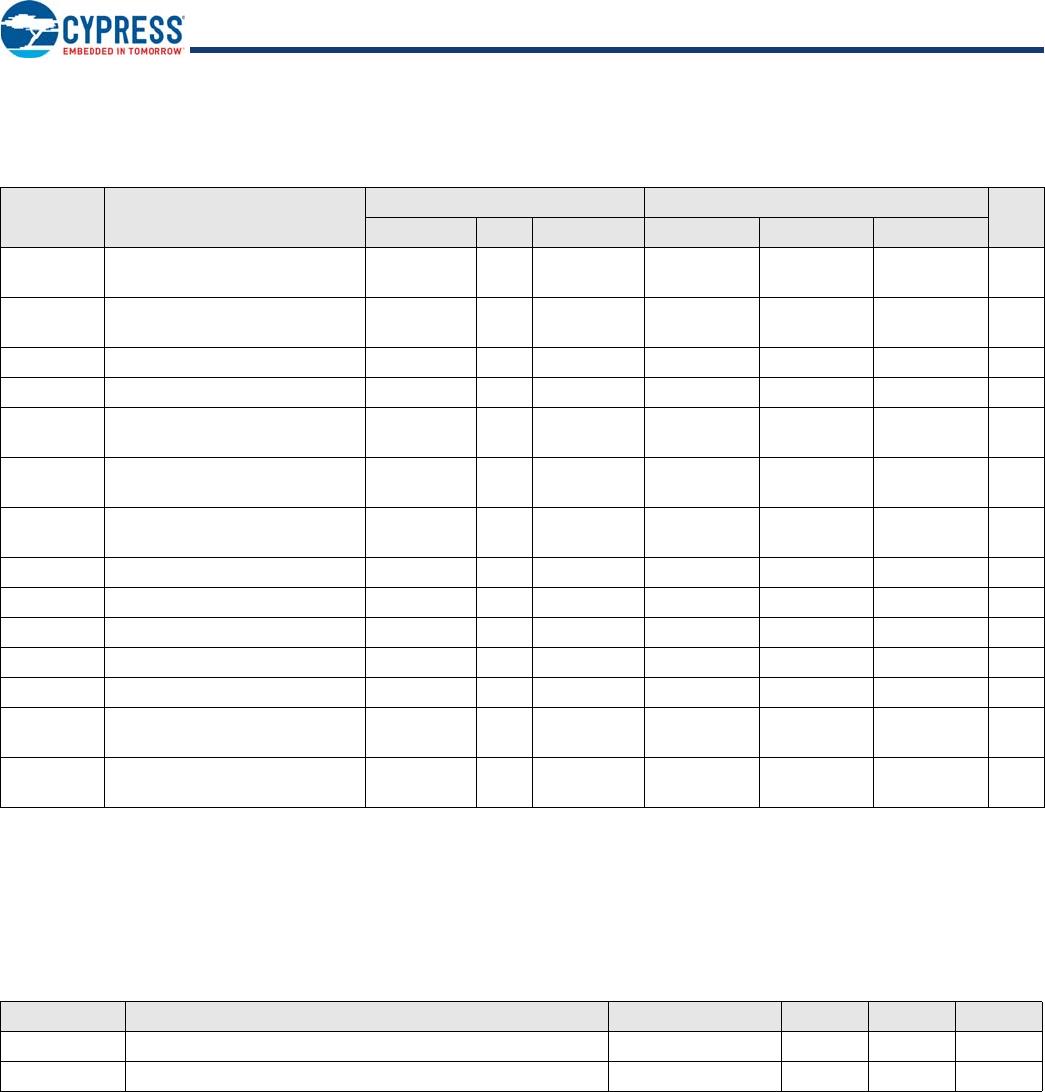

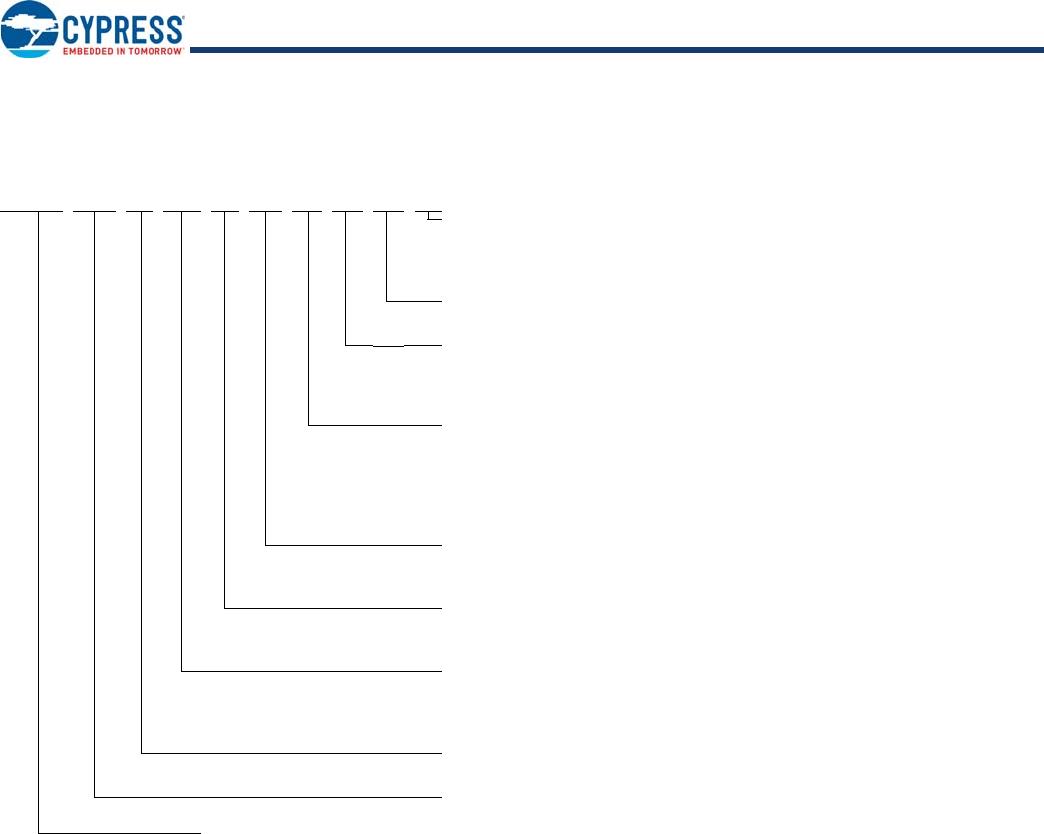

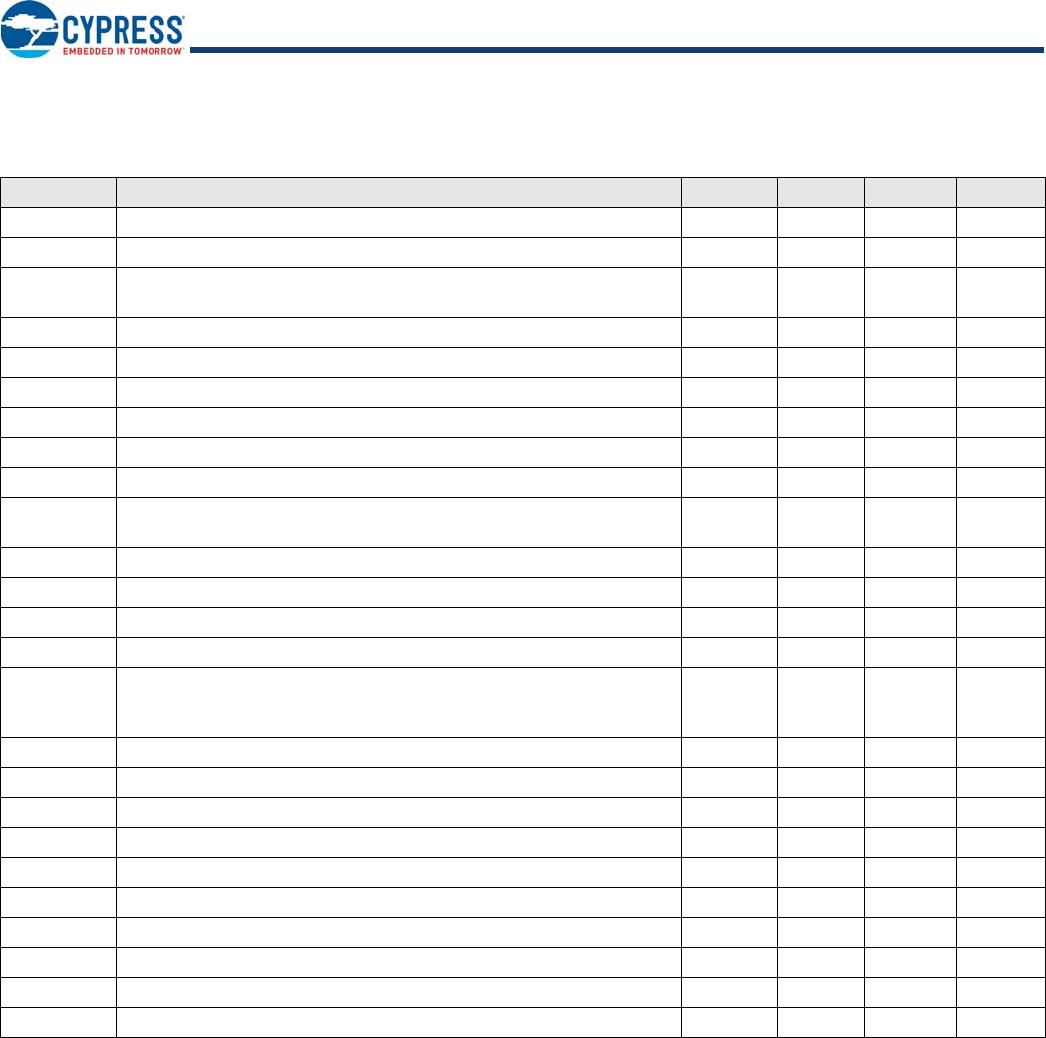

10. SDR AC Characteristics

Notes:

1. Only applicable as a constraint for WRR instruction when SRWD is set to a 1.

2. Full V

CC

range (2.7 - 3.6V) and CL = 30 pF.

3. Regulated V

CC

range (3.0 - 3.6V) and CL = 30 pF.

4. Regulated V

CC

range (3.0 - 3.6V) and CL = 15 pF.

5. ±10% duty cycle is supported for frequencies

50 MHz.

6. Maximum value only applies during Program/Erase Suspend/Resume commands.

7. When switching between die, a minimum time of t

CS

must be kept between the rising edge of one chip select and the falling edge of the other for operations and data

to be valid.

Table 6. SDR AC Characteristics (Single Die Package, V

CC

= 2.7V to 3.6V)

Symbol Parameter Min Typ Max Unit

F

SCK, R

SCK Clock Frequency for READ and 4READ instructions DC 50 MHz

F

SCK, C

SCK Clock Frequency for single commands (4) DC 133 MHz

F

SCK, C

SCK Clock Frequency for the following dual and quad commands:

DOR, 4DOR, QOR, 4QOR, DIOR, 4DIOR, QIOR, 4QIOR

DC

104 MHz

F

SCK, QPP

SCK Clock Frequency for the QPP, 4QPP commands DC 80 MHz

P

SCK

SCK Clock Period 1/ F

SCK

t

WH

, t

CH

Clock High Time (5) 45% P

SCK

ns

t

WL

, t

CL

Clock Low Time (5) 45% P

SCK

ns

t

CRT

, t

CLCH

Clock Rise Time (slew rate) 0.1 V/ns

t

CFT

, t

CHCL

Clock Fall Time (slew rate) 0.1 V/ns

t

CS

(7)

CS# High Time (Read Instructions)

CS# High Time (Program/Erase)

10

50

ns

t

CSS

CS# Active Setup Time (relative to SCK) 3 ns

t

CSH

CS# Active Hold Time (relative to SCK) 3 3000 (6) ns

t

SU

Data in Setup Time 1.5 ns

t

HD

Data in Hold Time 2 ns

t

V

Clock Low to Output Valid

8.0 (2)

7.65 (3)

6.5 (4)

ns

t

HO

Output Hold Time 2 ns

t

DIS

Output Disable Time 0 8 ns

t

WPS

WP# Setup Time 20 (1) ns

t

WPH

WP# Hold Time 100 (1) ns

t

HLCH

HOLD# Active Setup Time (relative to SCK) 3 ns

t

CHHH

HOLD# Active Hold Time (relative to SCK) 3 ns

t

HHCH

HOLD# Non-Active Setup Time (relative to SCK) 3 ns

t

CHHL

HOLD# Non-Active Hold Time (relative to SCK) 3 ns

t

HZ

HOLD# Enable to Output Invalid 8 ns

t

LZ

HOLD# Disable to Output Valid 8 ns