Chapter 3: DC and Switching Characteristics for MAX V Devices 3–25

Timing Model and Specifications

May 2011 Altera Corporation MAX V Device Handbook

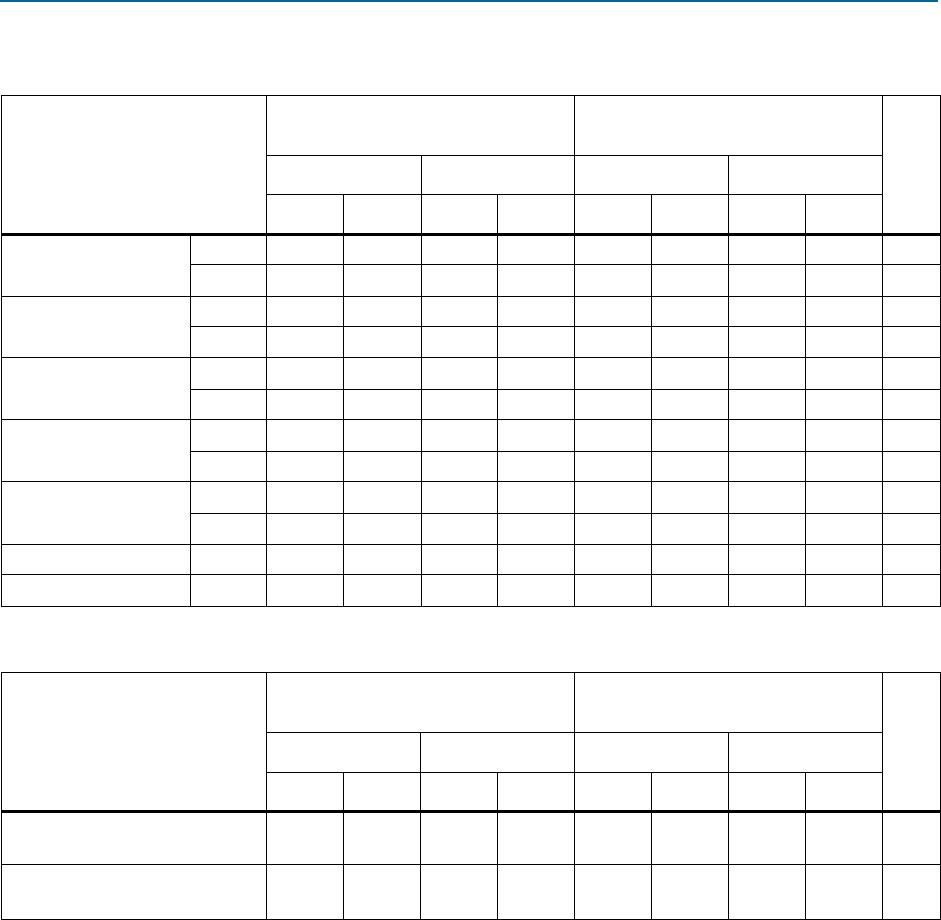

Table 3–35. External Timing Output Delay and t

OD

Adders for Slow Slew Rate for MAX V Devices

I/O Standard

5M40Z/ 5M80Z/ 5M160Z/

5M240Z/ 5M570Z

5M1270Z/ 5M2210Z

Unit

C4 C5, I5 C4 C5, I5

Min Max Min Max Min Max Min Max

3.3-V LVTTL

16 mA — 5,913 — 6,043 — 6,612 — 6,293 ps

8 mA — 6,488 — 6,645 — 7,313 — 6,994 ps

3.3-V LVCMOS

8 mA — 5,913 — 6,043 — 6,612 — 6,293 ps

4 mA — 6,488 — 6,645 — 7,313 — 6,994 ps

2.5-V LVTTL / LVCMOS

14 mA — 9,088 — 9,222 — 10,021 — 9,702 ps

7 mA — 9,808 — 9,962 — 10,881 — 10,562 ps

1.8-V LVTTL / LVCMOS

6 mA — 21,758 — 21,782 — 21,134 — 20,815 ps

3 mA — 23,028 — 23,032 — 22,399 — 22,080 ps

1.5-V LVCMOS

4 mA — 39,068 — 39,032 — 34,499 — 34,180 ps

2 mA — 40,578 — 40,542 — 36,281 — 35,962 ps

1.2-V LVCMOS 3 mA — 69,332 — 70,257 — 55,796 — 55,477 ps

3.3-V PCI 20 mA — 6,488 — 6,645 — 339 — 418 ps

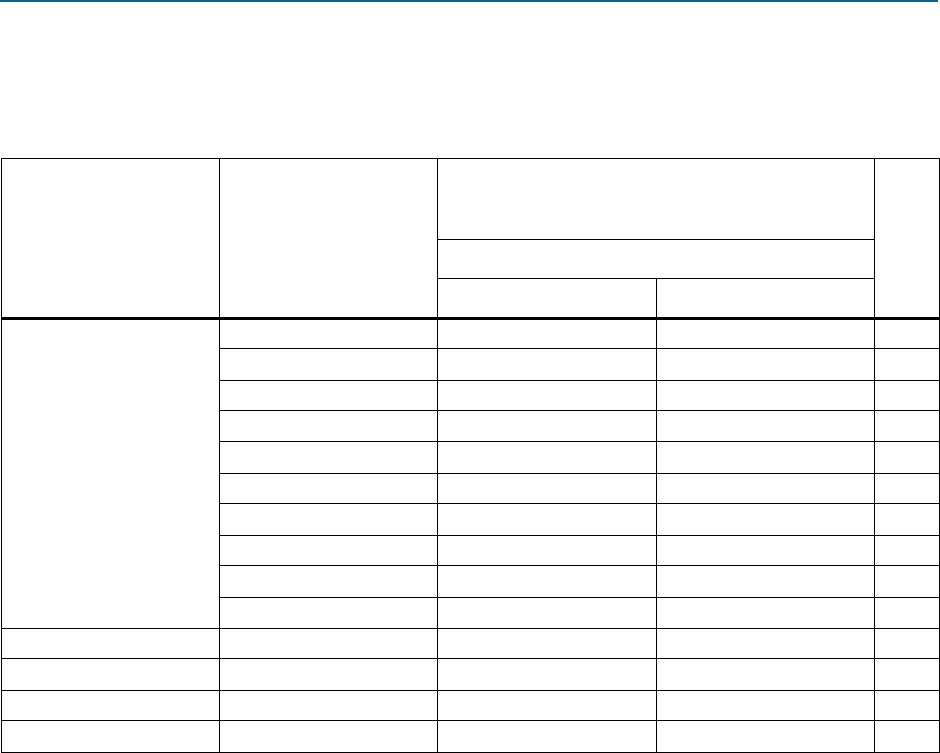

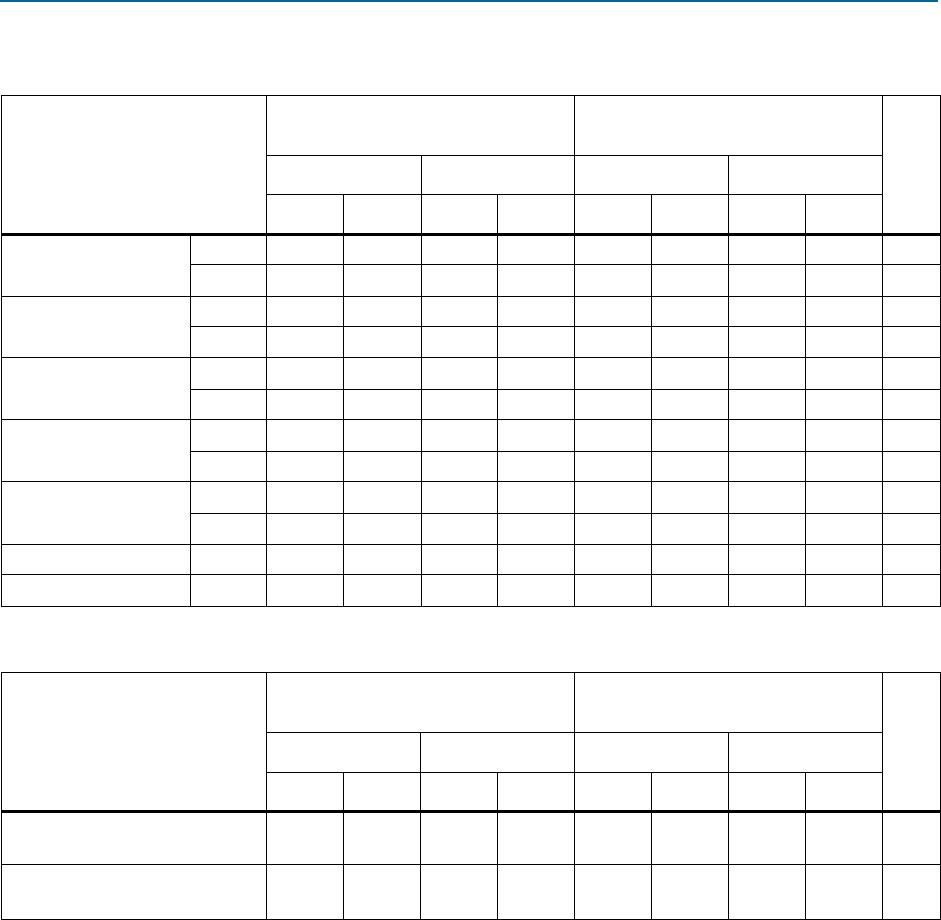

Table 3–36. IOE Programmable Delays for MAX V Devices

Parameter

5M40Z/ 5M80Z/ 5M160Z/

5M240Z/ 5M570Z

5M1270Z/ 5M2210Z

Unit

C4 C5, I5 C4 C5, I5

Min Max Min Max Min Max Min Max

Input Delay from Pin to Internal

Cells = 1

— 1,858 — 2,214 — 1,592 — 1,960 ps

Input Delay from Pin to Internal

Cells = 0

— 569 — 616 — 115 — 142 ps