Dual Digital Demodulators Copyright © 2015 by Silicon Laboratories 10.29.2015

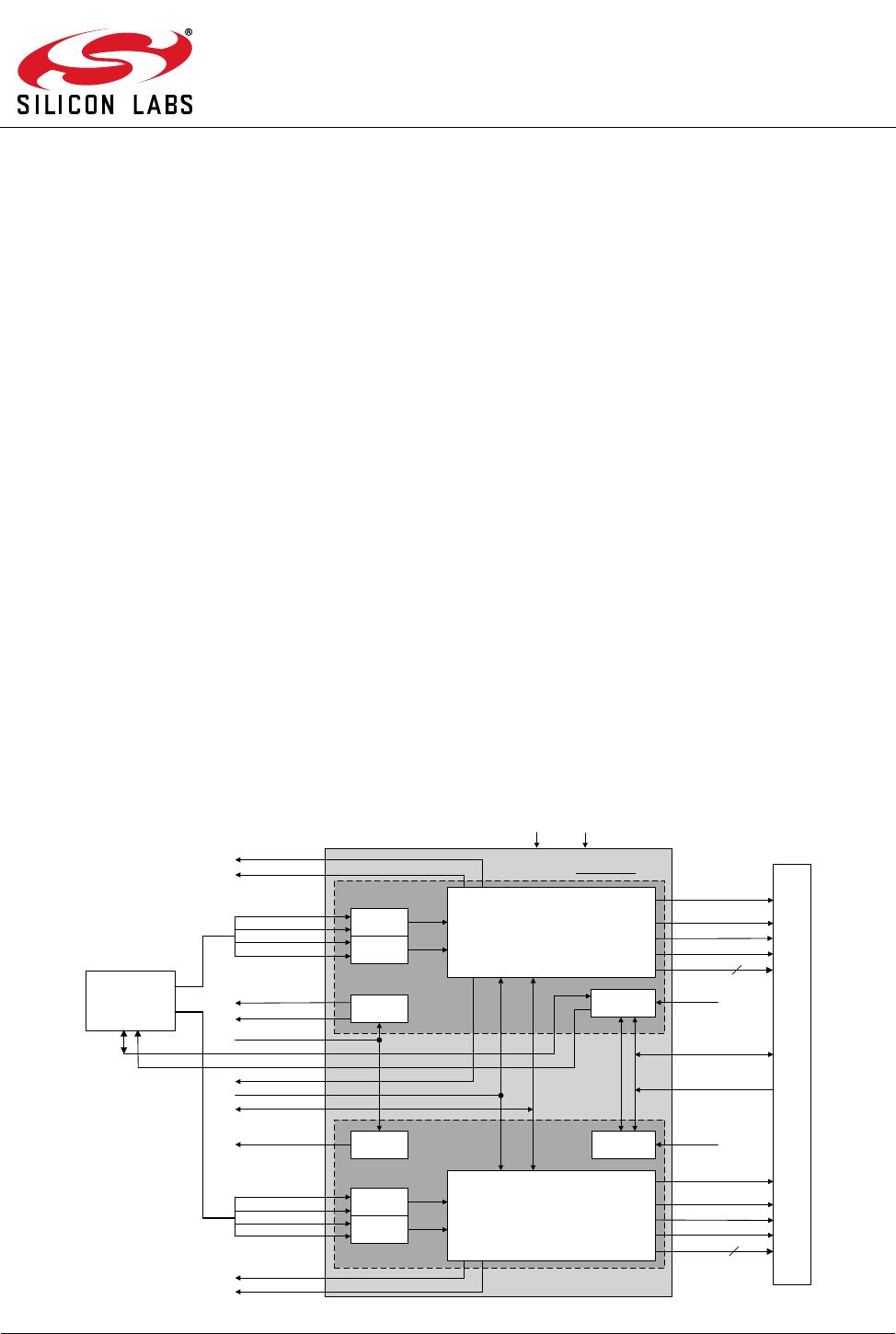

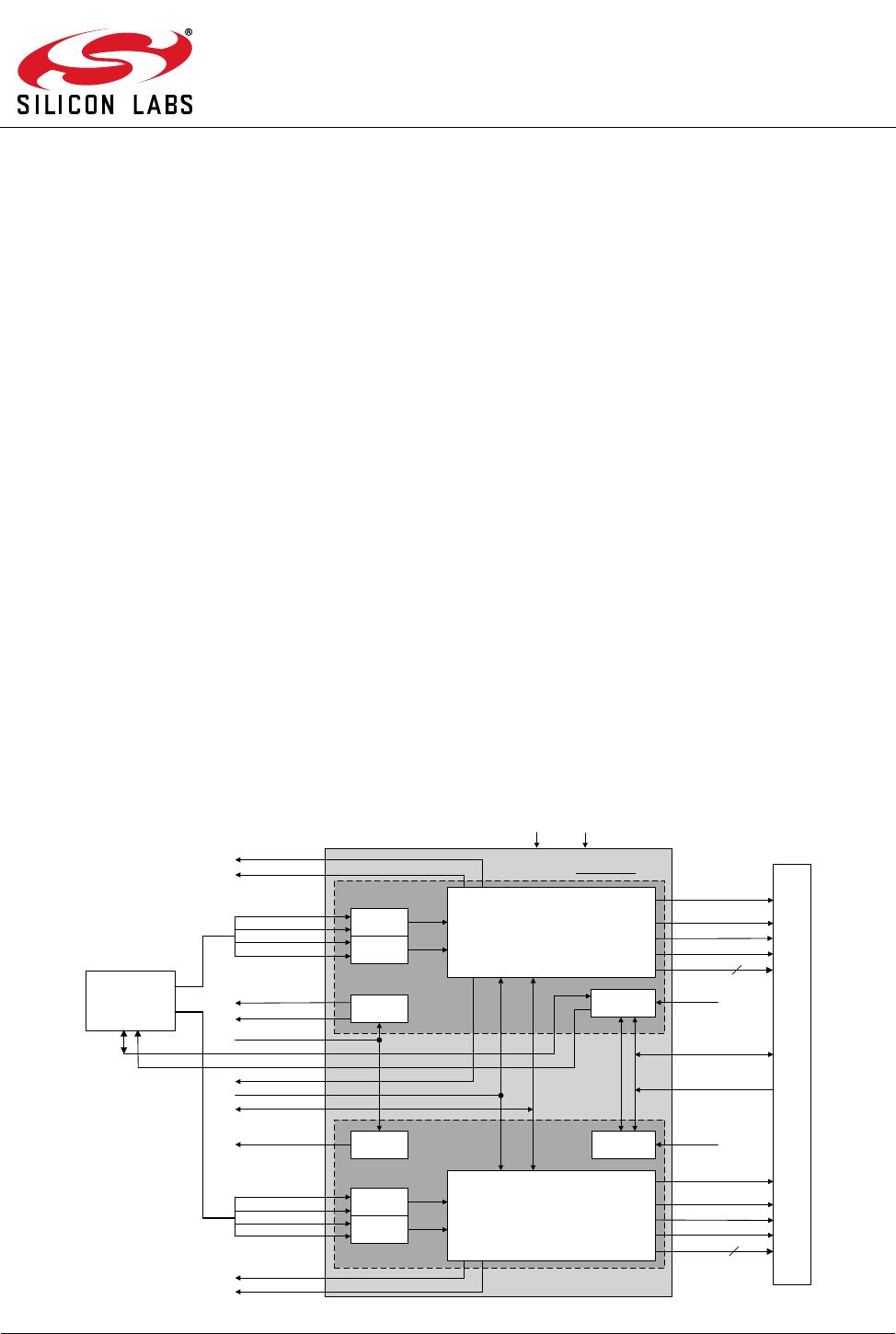

DEMODULATOR_A CORE

DiSEqC_A

ADC_A

ADC_A

HDTV MPEG S.o.C.

Si21662B

SCL_HOST

SDA_HOST

RESETB1.2, 3.3V

GPIO1/TS_ERR_A

TS_SYNC_A

TS_VAL_A

8

TS_CLK_A

TS_DATA_A

DiSEqC_IN_A_B

SDA_MAST

SCL_MAST

XO

XTAL_I/CLK_IN

CLK_IN/OUT

DEMODULATOR_B CORE

DiSEqC_B

ADC_B

ADC_B

DiSEqC_OUT_A

DiSEqC_CMD

S_ADC_IN_A

S_ADC_IP_A

S_ADC_QN_A

S_ADC_QP_A

Dual Satellite

Tuner

S_ADC_QP_B

S_ADC_QN_B

S_ADC_IP_B

S_ADC_IN_B

DiSEqC_OUT_B

MP_C_A

MP_A_A

MP_B_B

MP_D_B

GPIO0/TS_ERR_B

TS_SYNC_B

TS_VAL_B

8

TS_CLK_B

TS_DATA_B

ADDR_A

ADDR_B

I2C Block_A

I2C Block_B

Si21662-B22

Dual DVB-S/S2 Digital TV Demodulator

Description

The Si21662-B integrates two separate high performance

DVB-S, DVB-S2 and DSS digital demodulators into a single

compact package for satellite TV standards. Leveraging

Silicon Labs' proven digital demodulation architecture, each

embedded demodulator achieves excellent reception

performance for each standard while significantly minimizing

front-end design complexity and cost. Connecting the

Si21662-B to a dual satellite tuner, results in a

high-performance and cost optimized TV front-end solution.

The satellite demodulation functionality allows demodulating

w

i

dely deployed DVB-S, DIRECTV™ (DSS) legacy

standards, and DVB-S2 (AMC compliant) satellite broadcasts.

A zero-IF interface allows for a seamless connection to

market proven satellite silicon tuners.

Constant Coding Modulation (CCM), QPSK/8PSK

d

emodu

lation schemes and broadcast profile are the main

specifications of the DVB-S2 demodulator. Silicon Labs'

innovative LDPC and BCH decoding architecture delivers

best-in-class reception while exhibiting low power dissipation.

The Si21662-B offers an on-chip blind scanning algorithm for

D

V

B-S/S2 standards. It also integrates two DiSEqC™ 2.0

LNB interfaces for satellite dish control and, for each satellite

demodulator, an equalizer to compensate for echoes in long

cable feeds from the LNB to the satellite tuner RF input.

The Si21662-B embeds two independent programmable

tr

an

sport stream interfaces which provide a flexible range of

output modes and are fully compatible with all MPEG

decoders or conditional access modules to support any

customer application.

Features

- DVB-S2 (ETSI EN 302 307 and TR102-376)

-

QPSK/8PSK demodulator and FEC decoder

-

Broadcast profile CCM, 64800 bits frame, single TS

-

1 to 45 MSymbol/s

-

DIRECTV

TM

AMC compatible

- DVB-S (ETSI EN 300 421) and DSS supported

- QPSK demodulator and enhanced FEC decoder

- 1 to 45 MSymbol/s

- Dual DiSEqC™ 2.x interface, Unicable support

- I

2

C serial bus interfaces (master and host)

- Dual independent differential ZIF I/Q inputs

- GPIOs and multi-purpose ports (two per demodulator)

- Firmware control for upgradeability

- Separate flexible TS interfaces with serial or parallel

outputs

- Fast lock times for all standards

- Only two power supplies: 1.2 and 3.3 V

- 8x8 mm, QFN-68 pin package, Pb-free/RoHS compliant

- Pin-to-pin compatible with all dual demodulator family:

Si216x2

- API compatible with all single and dual demodulator

families

Applications

- Multi-receiver iDTV: on-board or in a NIM

- Advanced multimedia PVR STBs

- PC-TV accessories

- PVR, DVD, and Blu-Ray disc recorders