ZL30363 Short Form Data Sheet

2

Microsemi Corporation

Detailed Features

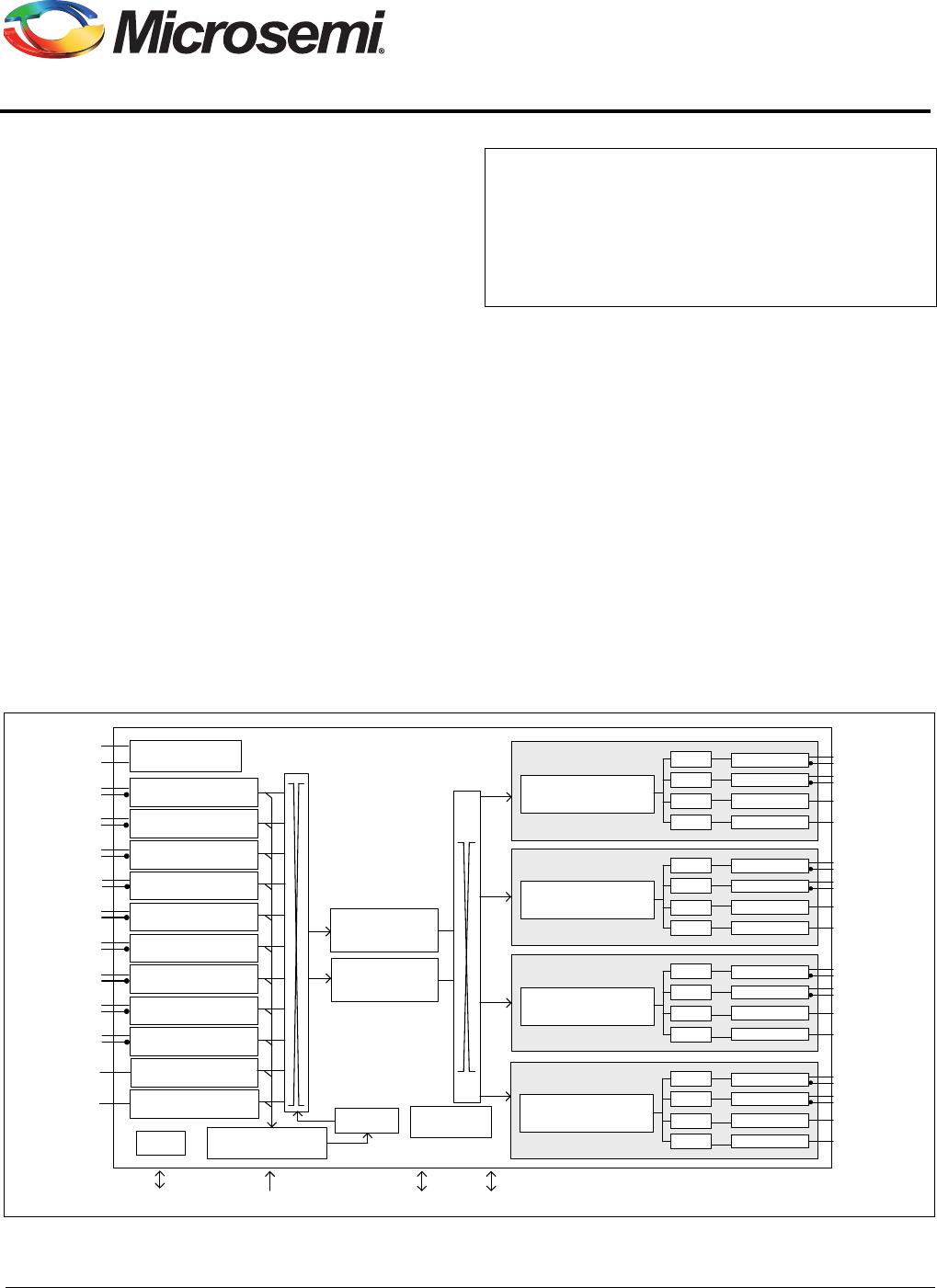

General

• Two independent clock channels

• Operates from a single crystal resonator or clock oscillator

• Configurable via its SPI/I

2

C interface

Time Synchronization Algorithm

• External algorithm controls software digital PLL to adjust frequency and phase alignment

• Frequency, Phase and Time Synchronization over IP, MPLS and Ethernet Packet Networks

• Frequency accuracy performance for WCDMA-FDD, GSM, LTE-FDD and femtocell applications, with target

performance less than ± 15 ppb.

• Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT EEC,

PNT PEC and CES interface specifications.

• Phase Synchronization performance for WCDMA-TDD, Mobile WiMAX, TD-SCDMA and CDMA2000

applications with target performance less than ± 1 s phase alignment.

• Time Synchronization for UTC-traceability and GPS replacement.

• Client reference switching between multiple Servers

• Client holdover when Server packet connectivity is lost

Electrical Clock Inputs

• Nine input references configurable as single ended or differential and two single ended input references

• Synchronize to any clock rate from 1 Hz to 750 MHz on differential inputs

• Synchronize to any clock rate from 1 Hz to 177.75 MHz on singled-ended inputs

• Any input reference can be fed with sync (frame pulse) or clock.

• Synchronize to sync pulse and sync pulse/clock pair.

• Flexible input reference monitoring automatically disqualifies references based on frequency and phase

irregularities

•LOS

• Single cycle monitor

• Precise frequency monitor

• Coarse frequency monitor

• Guard soak timer

• Per input clock delay compensation

Electrical Clock Engine

• Digital PLLs filter jitter from 0.1 mHz up to 1 kHz

• Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

• Internal state machine automatically controls mode of operation (free-run, locked, holdover)

• Automatic hitless reference switching and digital holdover on reference fail

• Physical-to-physical reference switching