AD7621

Rev. 0 | Page 9 of 32

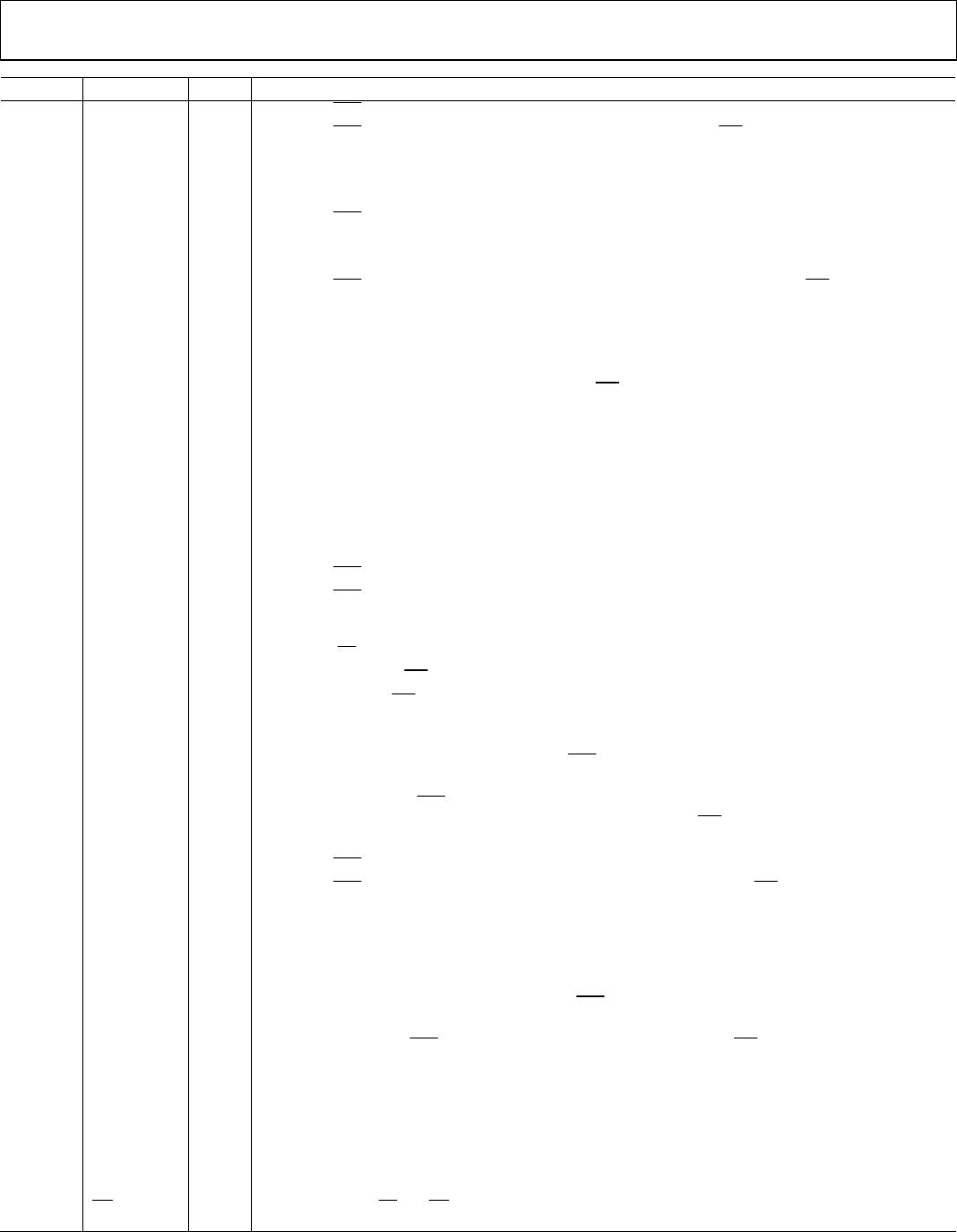

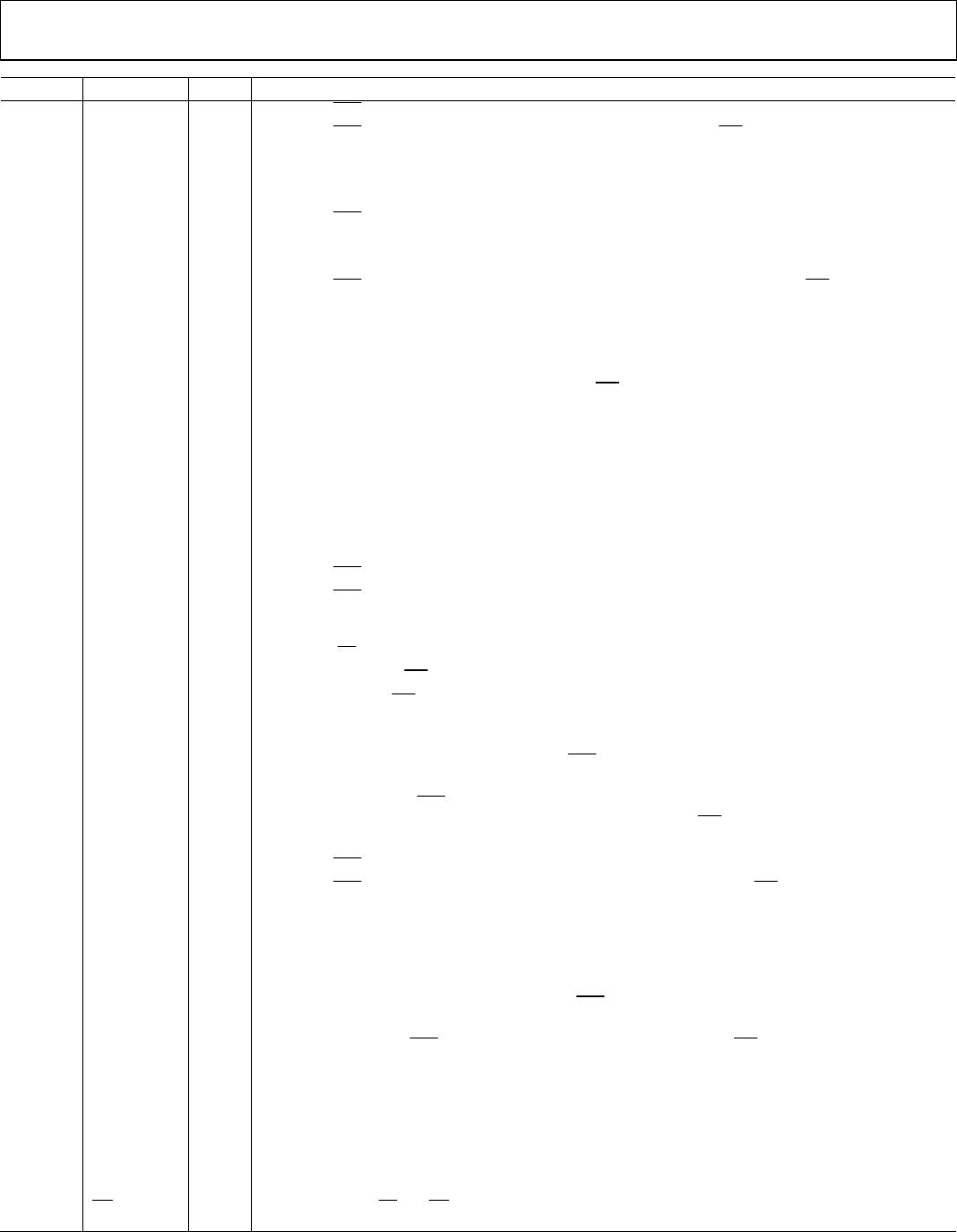

Pin No. Mnemonic Type

1

Description

14 D5 DI/O

When SER/

PAR = low this output is used as Bit 5 of the parallel port data output bus.

or INVSYNC

When SER/

PAR = high, invert sync select. In serial master mode (EXT/INT = low), this input is used to

select the active state of the SYNC signal.

When INVSYNC = low, SYNC is active high.

When INVSYNC = high, SYNC is active low.

15 D6 DI/O

When SER/

PAR

= low this output is used as Bit 6 of the parallel port data output bus.

or INVSCLK Invert SCLK Select. In all serial modes, this input is used to invert the SCLK signal.

16 D7 DI/O Bit 7 of the Parallel Port Data Output Bus.

or RDC

When SER/

PAR = high, read during convert. When using Serial Master mode (EXT/INT = low), RDC is

used to select the read mode.

When RDC = high, the previous conversion result is read during current conversion and the period of

SCLK changes (see the

Master Serial Interface section).

When RDC = low (read after convert), the current result is read after conversion.

or SDIN

Serial Data In. When using serial slave mode, (EXT/

INT = high), SDIN could be used as a data input to

daisy-chain the conversion results from two or more ADCs onto a single SDOUT line. The digital data

level on SDIN is output on SDOUT with a delay of 16 SCLK periods after the initiation of the read

sequence.

17 OGND P Input/Output Interface Digital Power Ground.

18 OVDD P

Input/Output Interface Digital Power. Nominally at the same supply as the supply of the host interface

(2.5 V or 3 V).

19 DVDD P Digital Power. Nominally at 2.5 V.

20 DGND P Digital Power Ground.

21 D8 DO

When SER/

PAR = low this output is used as Bit 8 of the parallel port data output bus.

or SDOUT

When SER/

PAR = high, serial data output. In serial mode, this pin is used as the serial data output

synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7621 provides the

conversion result, MSB first, from its internal shift register. The data format is determined by the logic

level of OB/2C.

In master mode (EXT/

INT = low). SDOUT is valid on both edges of SCLK.

In slave mode (EXT/

INT = high):

When INVSCLK = low, SDOUT is updated on SCLK rising edge and valid on the next falling edge.

When INVSCLK = high, SDOUT is updated on SCLK falling edge and valid on the next rising edge.

22 D9 DI/O

Parallel Port Data Output Bus Bit 9. When SER/

PAR = low, this output is used as Bit 9 of the parallel port

data output bus.

or SCLK

Serial Clock. When SER/

PAR = high, serial clock. In all serial modes, this pin is used as the serial data

clock input or output, dependent upon the logic state of the EXT/

INT pin. The active edge where the

data SDOUT is updated depends upon the logic state of the INVSCLK pin.

23 D10 DO

When SER/

PAR = low, this output is used as Bit 10 of the parallel port data output bus.

or SYNC

When SER/

PAR = high, frame synchronization. In serial master mode (EXT/INT= low), this output is

used as a digital output frame synchronization for use with the internal data clock.

When a read sequence is initiated and INVSYNC = low, SYNC is driven high and remains high while

SDOUT output is valid.

When a read sequence is initiated and INVSYNC = high, SYNC is driven low and remains low while

SDOUT output is valid.

24 D11 DO

Parallel Port Data Output Bus Bit 11. When SER/

PAR = low, this output is used as Bit 11 of the parallel

port data output bus.

or RDERROR

Read Error. When SER/

PAR = high, read error. In serial slave mode (EXT/INT = high), this output is used

as an incomplete read error flag. If a data read is started and not completed when the current

conversion is complete, the current data is lost and RDERROR is pulsed high.

25 to 28 D[12:15] DO Bit 12 to Bit 15 of the Parallel Port Data Output Bus.

29 BUSY DO

Busy Output. Transitions high when a conversion is started, and remains high until the conversion is

complete and the data is latched into the on-chip shift register. The falling edge of BUSY can be used

as a data ready clock signal.

30 DGND P Digital Power Ground.

31

RD

DI

Read Data. When

CS and RD are both low, the interface parallel or serial output bus is enabled.