–8–

Clock Generation

As distinct from the asynchronous VFCs that rely on the

stability of an external capacitor to set their full-scale frequency,

the AD7740 uses an external clock to define the full-scale output

frequency. The result is a more stable transfer function, which

allows the designer to determine the system stability and drift

based upon the selected external clock.

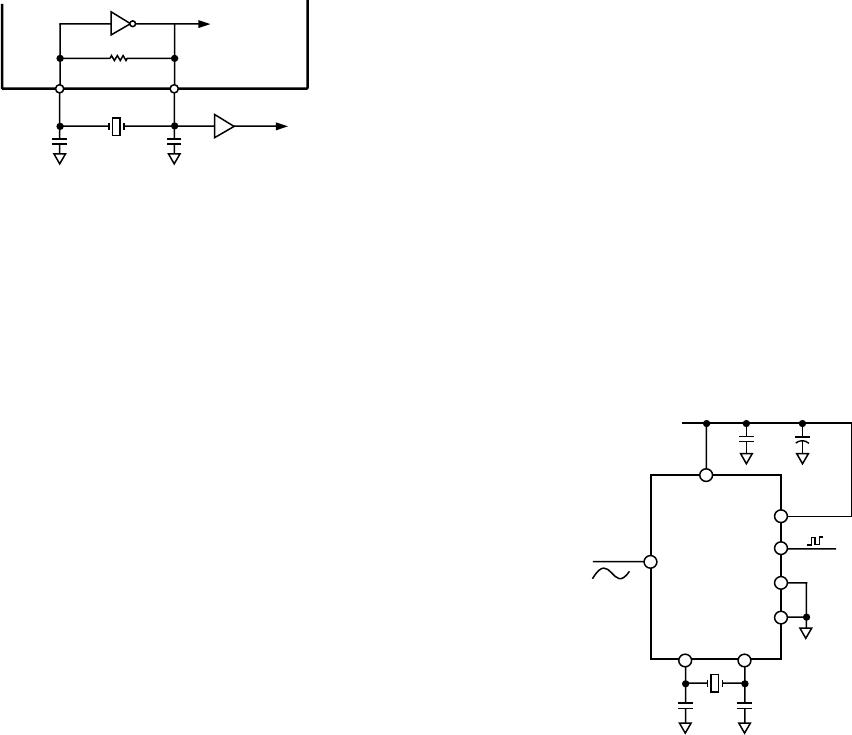

The AD7740 requires a master clock input, which may be an

external CMOS-compatible clock signal applied to the CLKIN

pin (CLKOUT not used). For a frequency of 1 MHz, a crystal

or resonator can be connected between CLKIN and CLKOUT

so that the clock circuit functions as a crystal controlled oscilla-

tor. Figure 7 shows a simple model of this.

CLKIN

CLKOUT

5M

C1

C2

ON-CHIP

CIRCUITRY

OFF-CHIP

CIRCUITRY

Figure 7. On-Chip Oscillator

Using the part with a crystal or ceramic resonator between the

CLKIN and CLKOUT pins generally causes more current to

be drawn from VDD than when the part is clocked from a driven

clock signal at the CLKIN pin. This is because the on-chip

oscillator is active in the case of the crystal or resonator. The

amount of additional current depends on a number of factors.

First, the larger the value of the capacitor on CLKIN and

CLKOUT pins, the larger the current consumption. Typical

values recommended by the crystal and resonator manufacturers

are in the range of 30 pF to 50 pF. Another factor that influ-

ences I

DD

is Effective Series Resistance of the crystal (ESR).

The lower the ESR value, the lower the current taken by the

oscillator circuit.

The on-chip oscillator also has a start-up time associated with it

before it oscillates at its correct frequency and voltage levels. The

typical start-up time is 10 ms with a V

DD

of 5 V and 15 ms with

a V

DD

of 3.3 V (both with a 1 MHz crystal).

The AD7740 master clock appears inverted on the CLKOUT

pin of the device. The maximum recommended load on this pin is

one CMOS load. When using a crystal to generate the AD7740’s

clock it may be desirable to then use this clock as the clock

source for the entire system. In this case, it is recommended that

the CLKOUT signal be buffered with a CMOS buffer before

being applied to the rest of the circuit (as shown in Figure 7).

Reference Input

The AD7740 performs conversions relative to the applied refer-

ence voltage. This reference may be taken from the internal 2.5 V

bandgap reference by leaving REFIN/OUT unconnected. Alterna-

tively an external precision reference may be used. This is

connected to the REFIN/OUT pin, overdriving the internal

reference. Drive capability, initial error, noise, and drift charac-

teristics should be considered when selecting an external refer-

ence. The AD780 and REF192 are suitable choices for external

references.

The internal reference is most suited to applications where

ratiometric operation of the signal source is possible. Using the

internal reference in systems where the signal source varies with

time, temperature, loading, etc., tends to cancel out errors.

Power-Down Mode

When CLKIN is inactive low for 1 ms (typ), the AD7740 auto-

matically enters a power-down mode. In this mode most of the

digital and analog circuitry is shut down and REFOUT floats.

FOUT goes high. This reduces the power consumption to 525 µW

max (5 V) and 360 µW (3.3 V).

APPLICATIONS

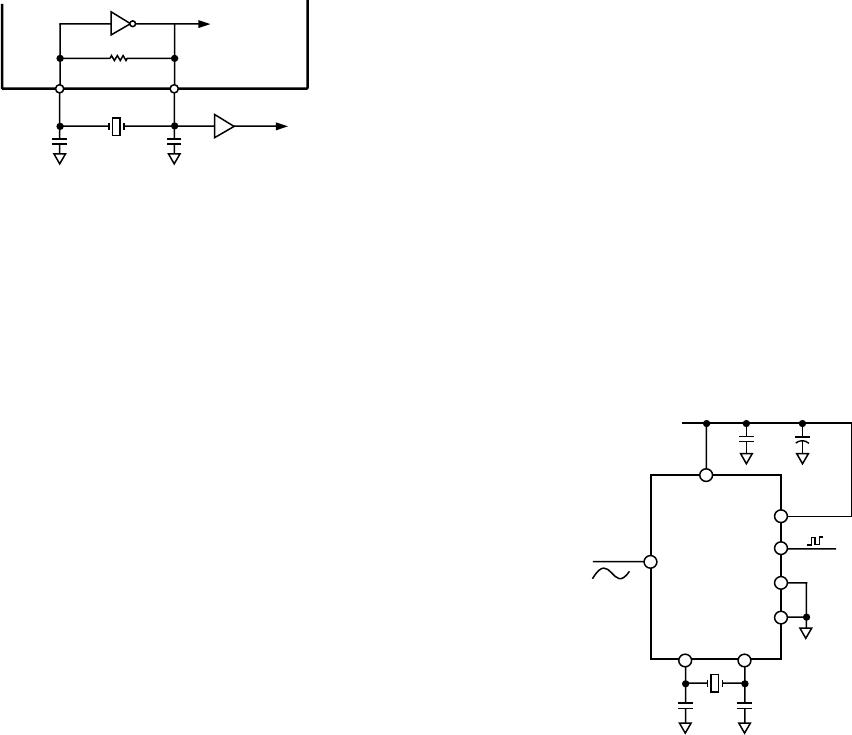

The basic connection diagram for the part is shown in Figure 8.

In the connection diagram shown, the AD7740 is configured in

unbuffered mode. The 5 V power supply is used as a reference to

the AD7740. A quartz crystal provides the master clock source

for the part. It may be necessary to connect capacitors (C1 and

C2 in the diagram) to the crystal to ensure that it does not oscil-

late at overtones of its fundamental operating frequency. The

values of capacitors will vary depending on the manufacturer’s

specifications.

REFIN

AD7740

CLKIN

CLKOUT

C1 C2

FOUT

GND

BUF

0.1F

10F

VIN

VDD

5V

Figure 8. Basic Connection Diagram

AD7740

REV. C