Document #: 38-07291 Rev. *C Page 4 of 9

Description

The CY29973 has an integrated PLL that provides low-skew and

low-jitter clock outputs for high-performance microprocessors.

Three independent banks of four outputs and an independent

PLL feedback output, FB_OUT, provide exceptional flexibility for

possible output configurations. The PLL is ensured stable

operation given that the VCO is configured to run between 200

MHz to 480 MHz. This allows a wide range of output frequencies

up to125 MHz.

The phase detector compares the input reference clock to the

external feedback input. For normal operation, the external

feedback input, FB_IN, is connected to the feedback output,

FB_OUT. The internal VCO is running at multiples of the input

reference clock set by FB_SEL(0:2) and VCO_SEL select inputs,

refer to Table 1 on page 1. The VCO frequency is then divided

down to provide the required output frequencies. These dividers

are set by SELA(0,1), SELB(0,1), SELC(0,1) select inputs, see

Table 2. For situations were the VCO needs to run at relatively

low frequencies and hence might not be stable, assert VCO_SEL

LOW to divide the VCO frequency by 2. This maintains the

desired output relationships, but provides an enhanced PLL lock

range.

The CY29973 is also capable of providing inverted output clocks.

When INV_CLK is asserted high, QC2 and QC3 output clocks

are inverted. These clocks could be used as feedback outputs to

the CY29973 or a second PLL device to generate early or late

clocks for a specific design. This inversion does not affect the

output to output skew.

Zero Delay Buffer

When used as a zero delay buffer the CY29973 is likely to be in

a nested clock tree application. For these applications the

CY29973 offers a low voltage PECL clock input as a PLL

reference. This allows the user to use LVPECL as the primary

clock distribution device to take advantage of its far superior

skew performance. The CY29973 then can lock onto the

LVPECL reference and translate with near zero delay to low

skew outputs.

By using one of the outputs as a feedback to the PLL the propa-

gation delay through the device is eliminated. The PLL works to

align the output edge with the input reference edge thus

producing a near zero delay. The reference frequency affects the

static phase offset of the PLL and thus the relative delay between

the inputs and outputs. Because the static phase offset is a

function of the reference clock the Tpd of the CY29973 is a

function of the configuration used.

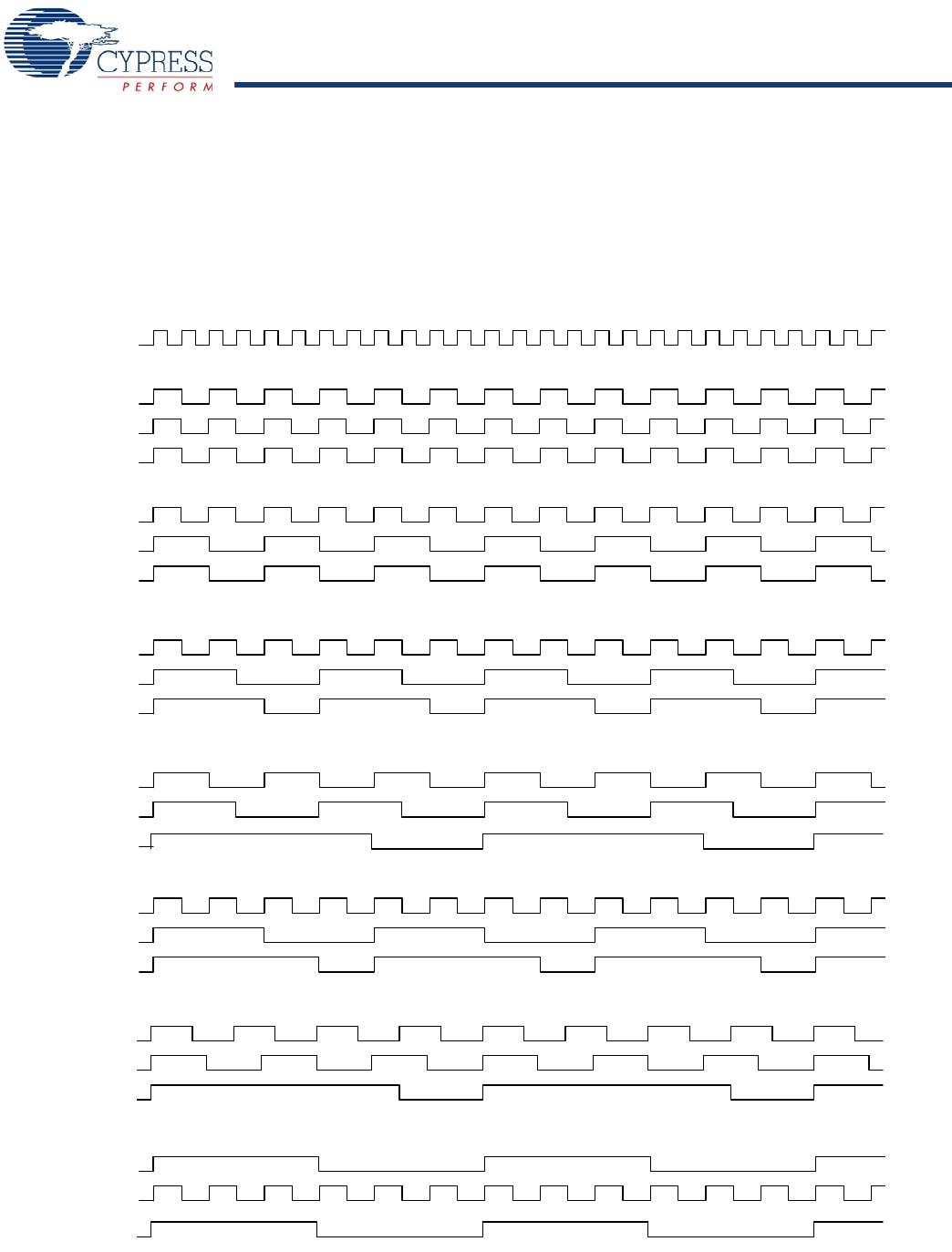

Glitch-Free Output Frequency Transitions

Customarily when output buffers have their internal counter’s

changed “on the fly’ their output clock periods will:

1. Contain short or “runt” clock periods. These are clock cycles

in which the cycle(s) are shorter in period than either the old

or new frequency that is being transitioned to.

2. Contain stretched clock periods. These are clock cycles in

which the cycle(s) are longer in period than either the old or

new frequency that is being transitioned to.

This device specifically includes logic to guarantee that runt and

stretched clock pulses do not occur if the device logic levels of

any or all of the following pins changed “on the fly” while it is

operating: SELA, SELB, SELC, and VCO_SEL.

Table 2. Divider Table

VCO_SEL SELA1 SELA0 QA SELB1 SELB0 QB SELC1 SELC0 QC

0 0 0 VCO/8 0 0 VCO/8 0 0 VCO/4

0 0 1VCO/120 1VCO/120 1 VCO/8

0 1 0VCO/161 0VCO/161 0VCO/12

0 1 1VCO/241 1VCO/201 1VCO/16

1 0 0 VCO/4 0 0 VCO/4 0 0 VCO/2

1 0 1 VCO/6 0 1 VCO/6 0 1 VCO/4

1 1 0 VCO/8 1 0 VCO/8 1 0 VCO/6

1 1 1VCO/121 1VCO/101 1 VCO/8

[+] Feedback