AD8345

Rev. B | Page 13 of 20

BASEBAND I AND Q CHANNEL DRIVE

The I channel and Q channel baseband inputs should be driven

differentially. This is convenient as most modern high-speed

DACs have differential outputs. For optimal performance at

V

S

= 5 V, the drive signal should be a 1.2 V p-p differential

signal with a bias level of 0.7 V; that is, each input should swing

from 0.4 V to 1 V. If the AD8345 is being run on a lower supply

voltage, then the peak-to-peak voltage on the I and Q channel

inputs must be reduced to avoid input clipping. For example, at

a supply voltage of 2.7 V, a 200 mV p-p differential drive is

recommended. This results in a corresponding reduction in

output power (see

Figure 3). The I and Q inputs have a large

input bandwidth of approximately 80 MHz. At lower baseband

input levels, the input bandwidth increases (see

Figure 4).

If the baseband signal has a high peak-to-average ratio (such as

CDMA or WCDMA), then the rms signal strength must be

backed off from this peak level in order to prevent clipping of

the signal peaks.

Clipping of signal peaks tends to increase signal leakage into

adjacent channels. Backing off the I and Q signal strength, in

the manner recommended, reduces the output power by a

corresponding amount. This also applies to multicarrier

applications where the per-carrier output power is lower by

3 dB for each doubling of the number of output carriers.

The I and Q inputs have high input impedances because they

connect directly to the bases of PNP transistors. If a dc-coupled

filter is being used between a DAC and the modulator inputs,

then the filter must be terminated with the appropriate

resistance. If the filter is differential, then the termination

resistor should be connected across the I and Q differential

inputs.

REDUCTION OF LO LEAKAGE

Because the I and Q signals are being effectively multiplied with

the LO, any internal offset voltages on these inputs result in

leakage of the LO. The nominal LO leakage of −42 dBm, which

results from these internal offset voltages, can be reduced further

by applying offset compensation voltages on the I and Q inputs.

(Note that LO feedthrough is reduced by varying the differential

offset voltages on the I and Q inputs, not by varying the nominal

bias level of 0.7 V.) The reduction is easily accomplished by

programming (and then storing) the appropriate DAC offset

code. This does, however, require dc coupling the path from the

DAC to the I and Q inputs. (DC coupling is also advantageous

from the perspective of I and Q input biasing if the DAC is

capable of delivering a bias level of 0.7 V.)

The procedure for reducing the LO feedthrough is simple. In

order to isolate the LO in the output spectrum, a single

sideband configuration is recommended (set I and Q signals to

sine and cosine waves at, for example, 100 kHz; set LO to

F

RF

− 100 kHz). An offset voltage is applied from the I DAC

until the LO leakage reaches a trough. With this offset level

held, an offset voltage is applied to the Q DAC until a (lower)

trough is reached.

LO leakage compensation holds up well over temperature.

Figure 10 shows the effect of temperature on LO leakage after

compensation at ambient.

Compensated LO leakage degrades somewhat as the frequency

is moved away from the frequency at which the compensation

was performed. This is due to the effects of LO to RF output

leakage, which is not a result of offsets on the I and Q inputs.

SINGLE-ENDED I AND Q DRIVE

Where only single-ended I and Q signals are available, a

differential amplifier such as the AD8132 or AD8138 can be

used to generate the required differential drive signal for the

AD8345.

Although most DACs have differential outputs, using a single-

ended, low-pass filter between the dual DAC and the I and Q

inputs can be more desirable from the perspective of

component count and cost. As a result, the output signal from

the filter must be converted back to differential mode and

possibly be rebiased to 0.7 V common mode.

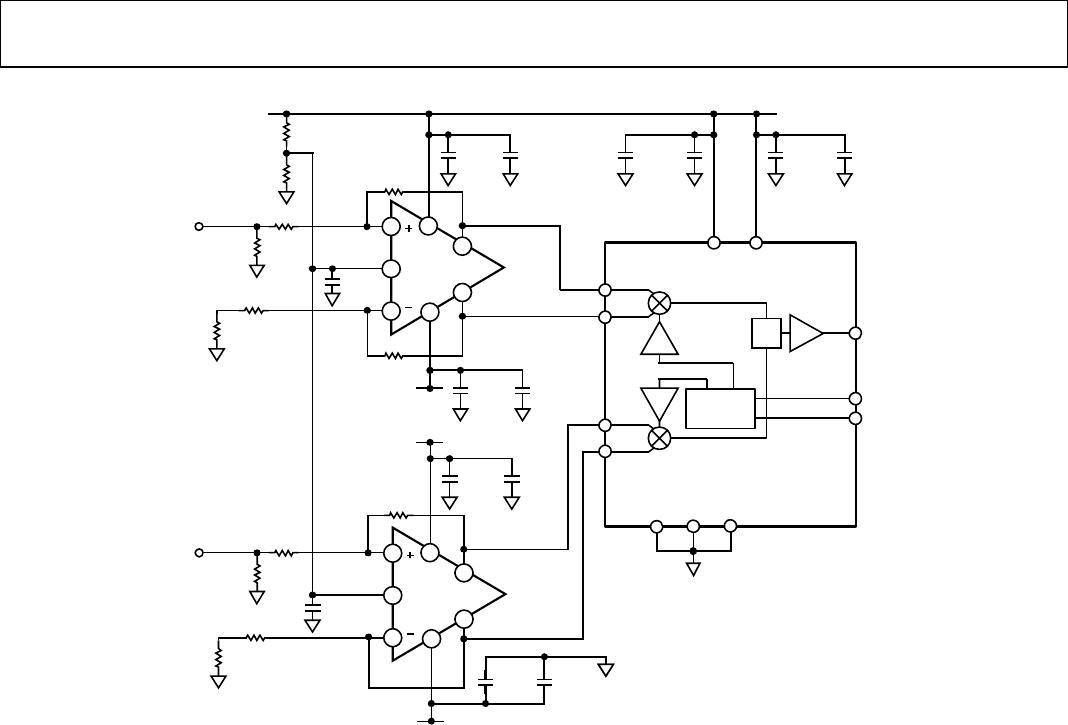

Figure 30 shows a circuit that converts a ground-referenced,

single-ended signal to a differential signal and adds the required

0.7 V bias voltage. Two AD8132 differential op amps configured

for unity gain are used. With a 50 Ω input impedance, this

circuit is configured to accept a signal from a 50 Ω source (for

example, a low-pass filter). The input impedance can be easily

changed by replacing the 49.9 Ω shunt resistor (and the

corresponding 24.9 Ω resistor on the inverting input) with the

appropriate value. The required dc-bias level is conveniently

added to the signal by applying 0.7 V to the V

OCM

pins of the

differential amplifiers.

Differential amplifiers, such as the AD8132 and AD8138, can

also be used to implement active filters. For more information

on this topic, refer to the data sheets of these devices.