PDF: 09005aef80a8e793/Source: 09005aef80a8e767 Micron Technology, Inc., reserves the right to change products or specifications without notice.

dd5c16_32x72h.fm - Rev. F 2/07 EN

11 ©2004 Micron Technology, Inc. All rights reserved.

128MB, 256MB: (x72, ECC, SR) 200-Pin DDR SODIMM

Serial Presence-Detect

Serial Presence-Detect

Notes: 1. To avoid spurious start and stop conditions, a minimum delay is placed between SCL = 1 and

the falling or rising edge of SDA.

2. This parameter is sampled.

3. For a restart condition or following a WRITE cycle.

4. The SPD EEPROM WRITE cycle time (

t

WRC) is the time from a valid stop condition of a write

sequence to the end of the EEPROM internal ERASE/PROGRAM cycle. During the WRITE

cycle, the EEPROM bus interface circuit is disabled, SDA remains HIGH due to pull-up resis-

tance, and the EEPROM does not respond to its slave address.

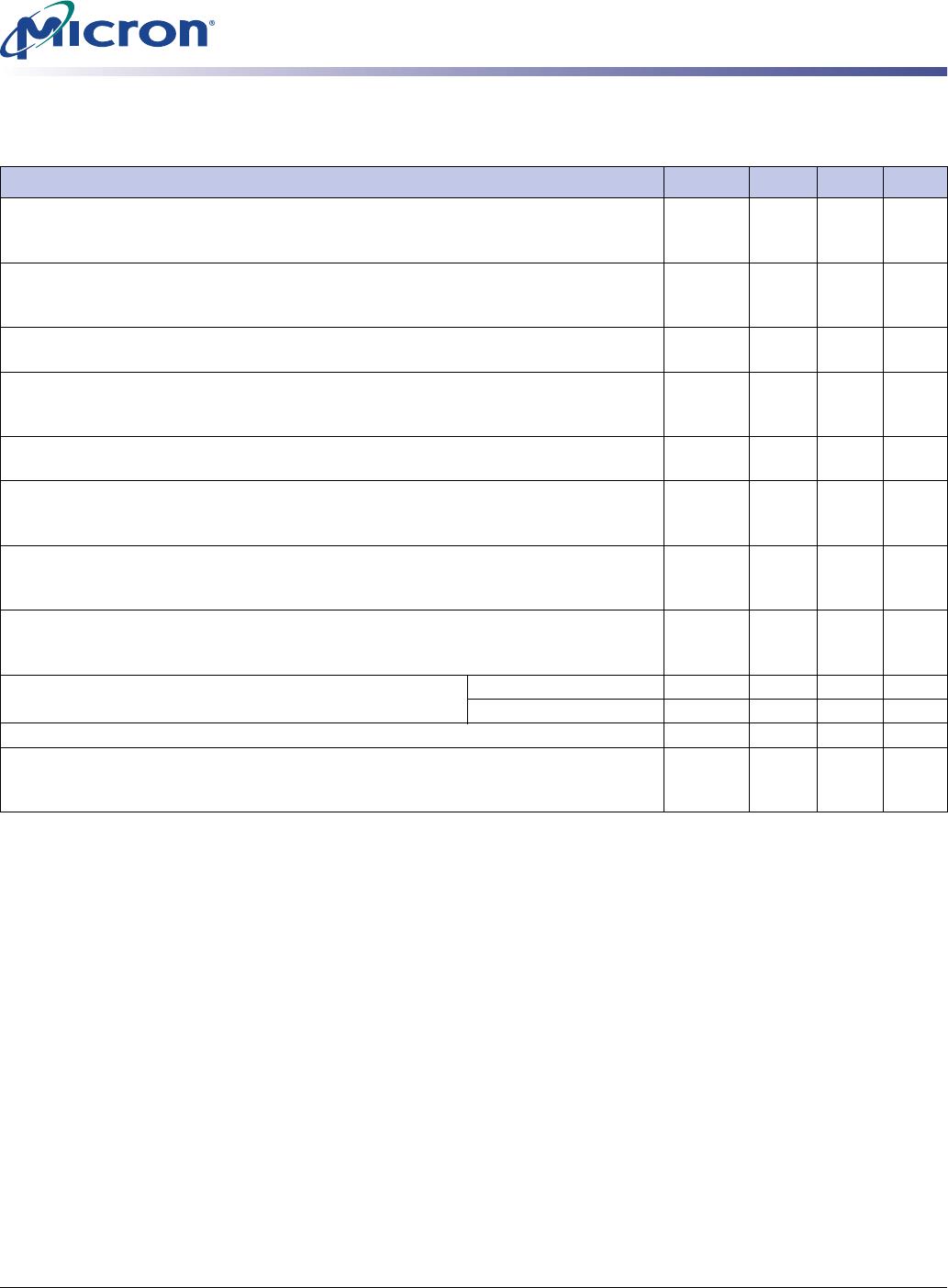

Table 11: Serial Presence-Detect EEPROM DC Operating Conditions

All voltages referenced to VSS; VDDSPD = +2.3V to +3.6V

Parameter/Condition Symbol Min Max Units

Supply voltage

V

DDSPD 2.3 3.6 V

Input high voltage: Logic 1; All inputs

V

IH VDDSPD × 0.7 VDDSPD + 0.5 V

Input low voltage: Logic 0; All inputs

V

IL –1 VDDSPD × 0.3 V

Output low voltage: I

OUT = 3mA

V

OL –0.4V

Input leakage current: V

IN = GND to VDD

ILI –10µA

Output leakage current: V

OUT = GND to VDD

ILO –10µA

Standby current: SCL = SDA = V

DD - 0.3V; All other inputs = VSS or VDD

ISB –30µA

Power supply current: SCL clock frequency = 100 kHz

I

CC –2mA

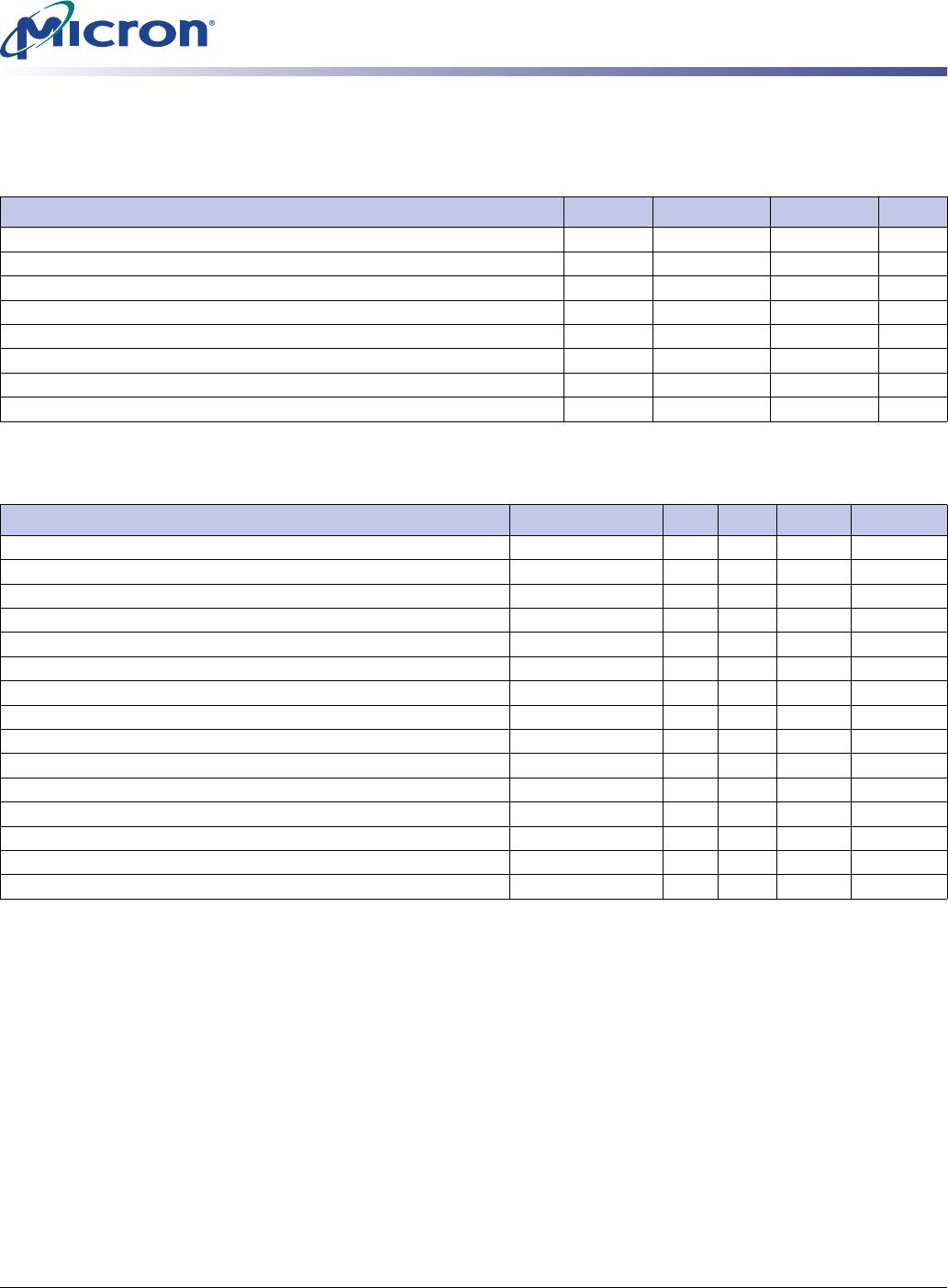

Table 12: Serial Presence-Detect EEPROM AC Operating Conditions

All voltages referenced to VSS; VDDSPD = +2.3V to +3.6V

Parameter/Condition Symbol Min Max Units Notes

SCL LOW to SDA data-out valid

t

AA 0.2 0.9 µs 1

Time the bus must be free before a new transition can start

t

BUF 1.3 – µs

Data-out hold time

t

DH 200 – ns

SDA and SCL fall time

t

F–300ns2

Data-in hold time

t

HD:DAT 0 – µs

Start condition hold time

t

HD:STA 0.6 – µs

Clock HIGH period

t

HIGH 0.6 – µs

Noise suppression time constant at SCL, SDA inputs

t

I–50ns

Clock LOW period

t

LOW 1.3 – µs

SDA and SCL rise time

t

R–0.3µs2

SCL clock frequency

f

SCL – 400 kHz

Data-in setup time

t

SU:DAT 100 – ns

Start condition setup time

t

SU:STA 0.6 – µs 3

Stop condition setup time

t

SU:STO 0.6 – µs

WRITE cycle time

t

WRC – 10 ms 4