Detailed Description

The MAX9370/MAX9371/MAX9372 LVTTL/TTL-to-differ-

ential LVPECL/PECL translators are designed for high-

speed communication signal and clock driver

applications. The MAX9370/MAX9372 are dual LVTTL-

to-LVPECL/PECL translators that operate in excess of

1GHz. The MAX9371 is a single translator. The

MAX9370/MAX9371 operate over a wide 3.0V to 5.25V

supply range, allowing high-performance clock or data

distribution in systems with a nominal 3.3V or 5.0V sup-

ply. The MAX9372 is optimized for 3.0V to 3.6V opera-

tion. These devices feature low 270ps propagation

delay and 40ps peak-to-peak deterministic jitter.

Inputs and Outputs

The MAX9370/MAX9371/MAX9372 inputs accept stan-

dard LVTTL/TTL levels. The input has pullup circuitry that

drives the outputs to a differential high if the inputs are

open. The outputs are differential LVPECL/PECL levels.

Applications Information

Output Termination

Terminate outputs with 50Ω to V

CC

- 2V or use an equiv-

alent Thevenin termination. Use the same terminate on

each output for the lowest output-to-output skew. When a

single-ended signal is taken from a differential output,

terminate both outputs. For example, if Q is used as a

single-ended output, terminate both Q and Q.

MAX9370/MAX9371/MAX9372

LVTTL/TTL-to-Differential LVPECL/PECL

Translators

_______________________________________________________________________________________ 5

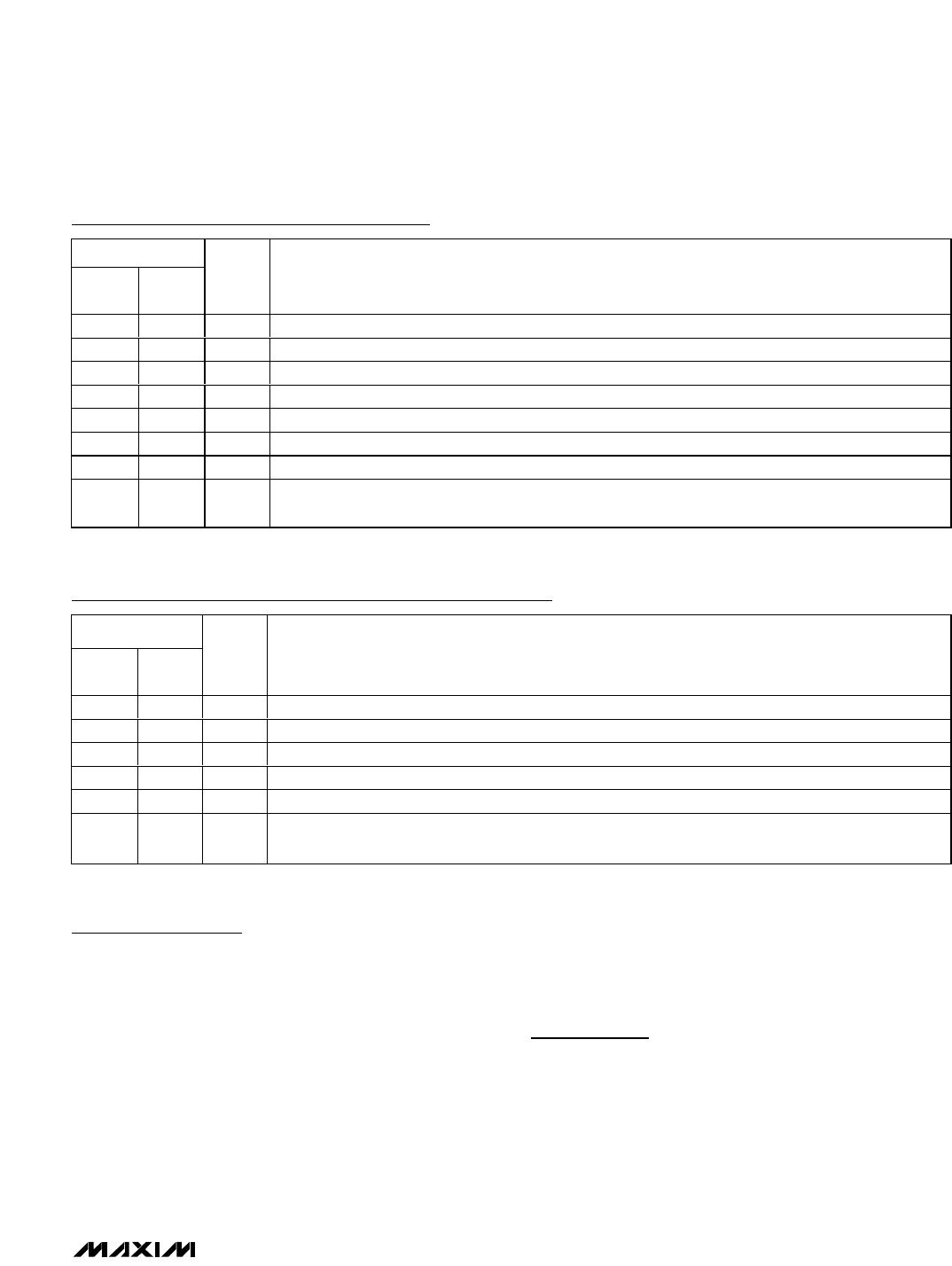

Pin Description for the MAX9370/MAX9372

FUNCTION

1 8 Q0 Noninverting Differential LVPECL/PECL Output 0. Typically terminate with 50Ω resistor to V

CC

- 2V.

27Q0 Inverting Differential LVPECL/PECL Output 0. Typically terminate with 50Ω resistor to V

CC

- 2V.

3 6 Q1 Noninverting Differential LVPECL/PECL Output 1. Typically terminate with 50Ω resistor to V

CC

- 2V.

45Q1 Inverting Differential LVPECL/PECL Output 1. Typically terminate with 50Ω resistor to V

CC

- 2V.

52

Ground. Provide a low-impedance connection to ground plane.

6 4 D1 LVTTL/TTL Input 1. LVTTL/TTL input for translator corresponding to output Q1 and Q1.

7 3 D0 LVTTL/TTL Input 0. LVTTL/TTL input for translator corresponding to output Q0 and Q0.

81V

CC

Positive Supply Voltage. Bypass V

CC

to GND with 0.1µF and 0.01µF ceramic capacitors. Place the

capacitors as close to the device as possible with the smaller value capacitor closest to the device.