PDF: 09005aef8326e5ac / Source: 09005aef8326e59a Micron Technology, Inc., reserves the right to change products or specifications without notice.

152ball_ nand_lpdram_j4xx_omap.fm - Rev. E 4/09 EN

8 ©2008 Micron Technology, Inc. All rights reserved.

152-Ball NAND Flash and Mobile LPDRAM PoP (TI OMAP) MCP

Ball Assignments and Descriptions

Preliminary

Notes: 1. Balls marked RFU may or may not be connected internally. These balls should not be used.

Contact the factory for details.

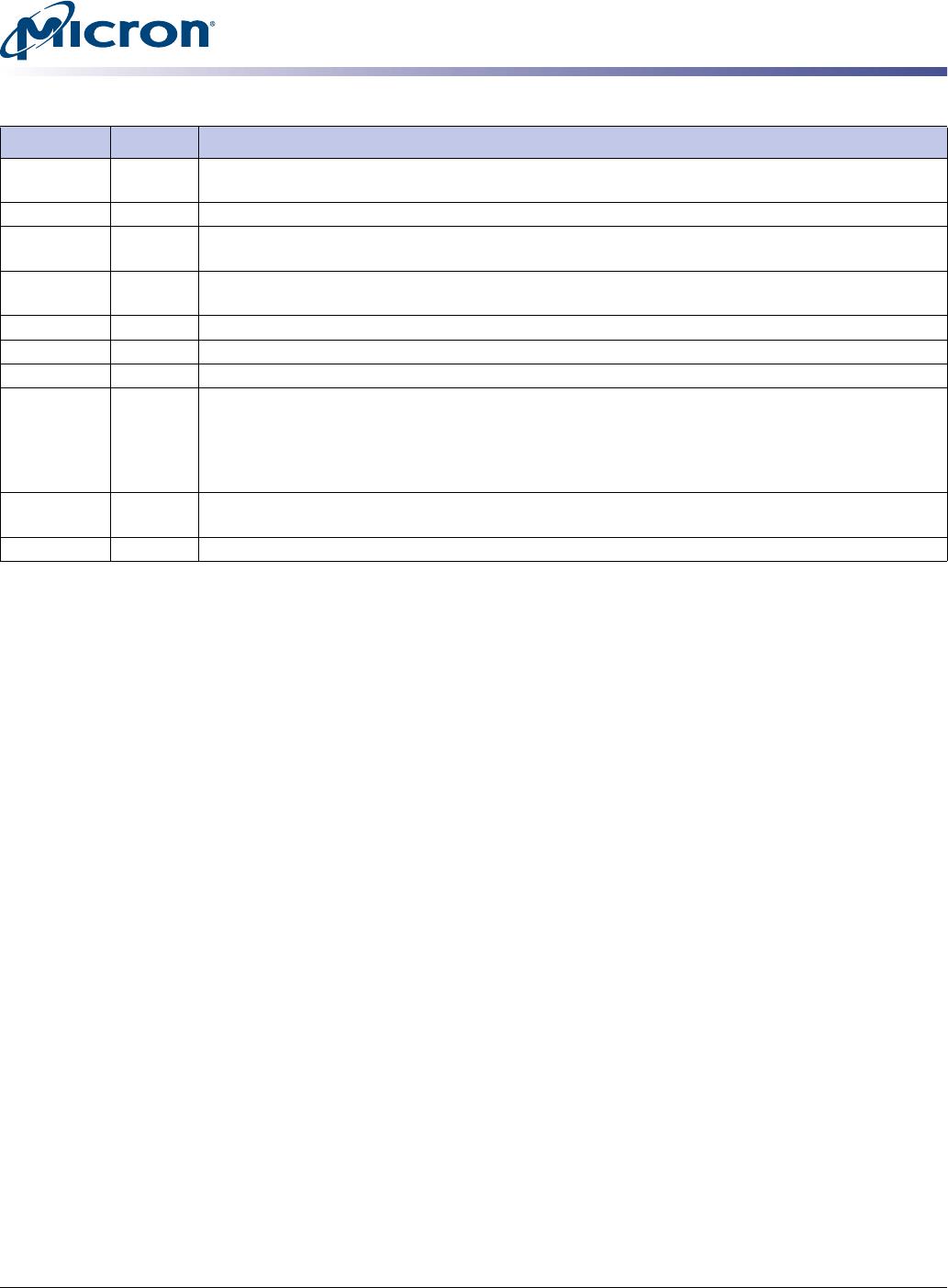

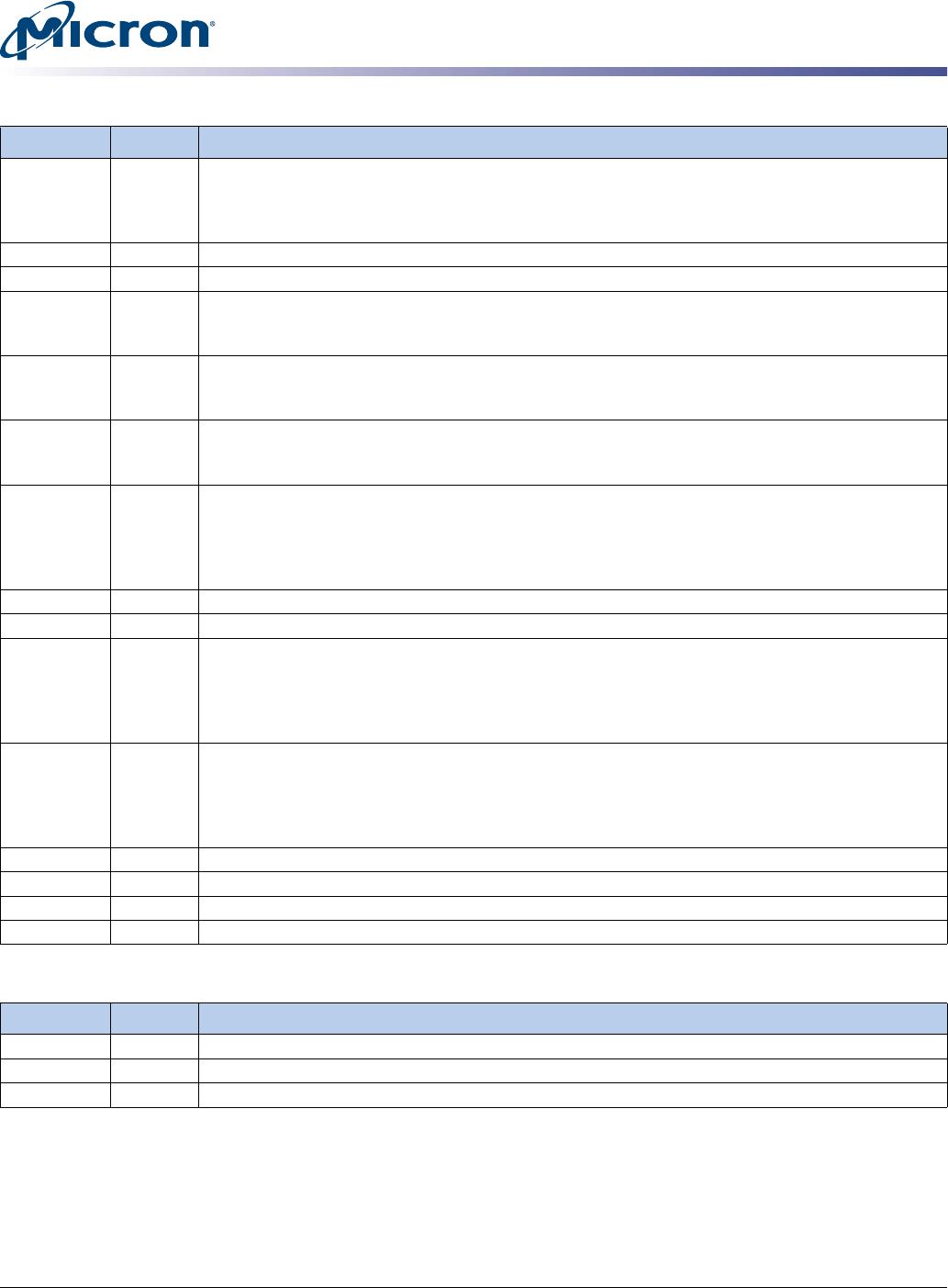

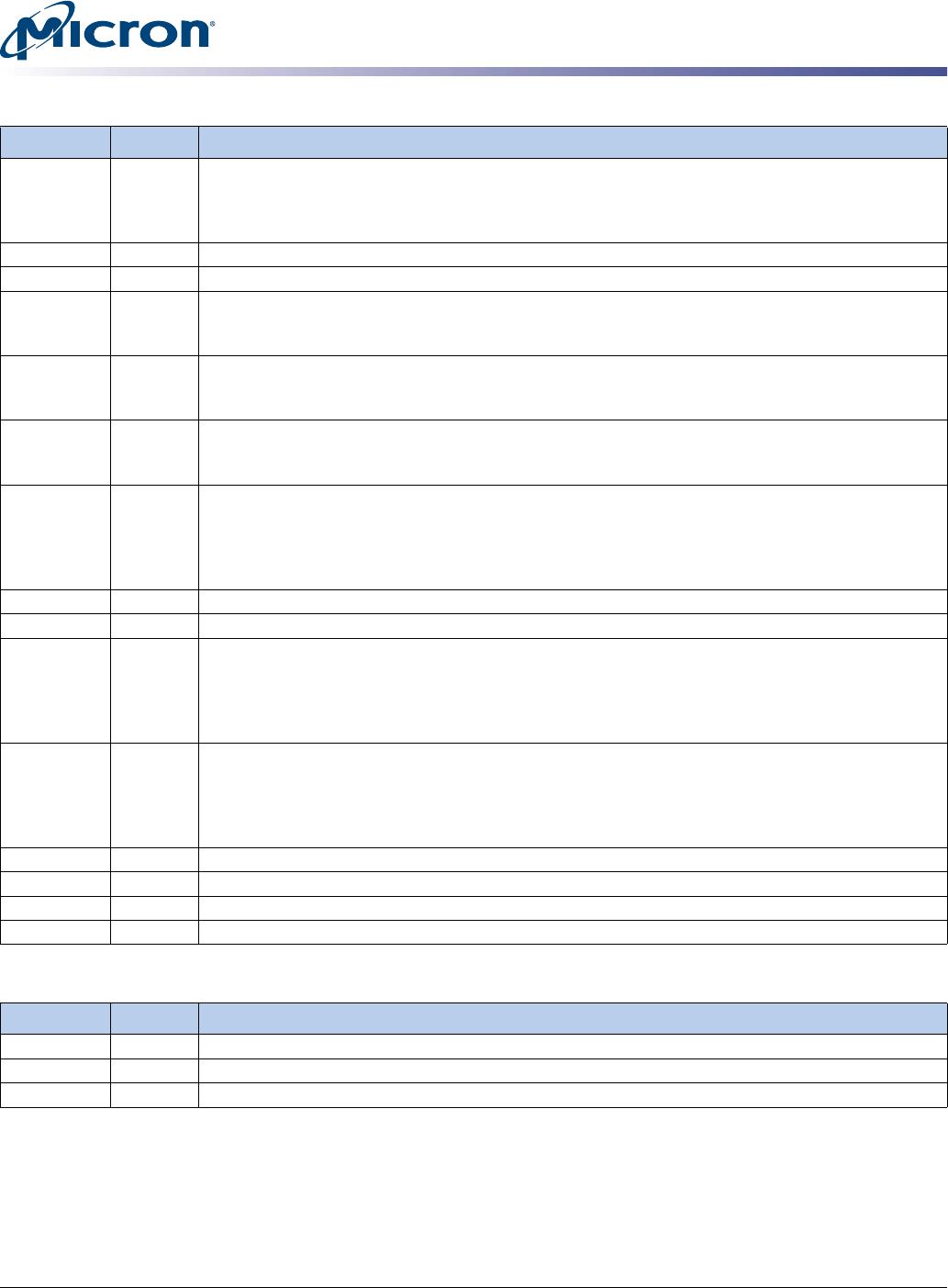

Table 3: x16/x32 LPDDR Ball Descriptions

Symbol Type Description

A[14:0] Input

Address inputs: Specifies the row or column address. Also used to load the mode registers. The

maximum LPDDR address is determined by density and configuration. Consult the LPDDR

product data sheet for the maximum address for a given density and configuration. Unused

address pins become RFU.

BA1, BA0 Input

Bank address inputs: Specifies one of the 4 banks.

CAS# Input

Column select: Specifies the command to execute.

CK, CK# Input

CK is the system clock. CK and CK# are differential clock inputs. All address and control signals

are sampled and referenced on the crossing of the rising edge of CK with the falling edge of

CK#.

CKE0, CKE1 Input

Clock enable:

CKE0 is used for a single LPDDR product.

CKE1 is used for dual LPDDR products.

CS1#, CS0# Input

Chip select:

CS0# is used for a single LPDDR product.

CS1# is used for dual LPDDR products and is considered RFU for single LPDDR MCPs.

LDM, UDM

(x16)

DM[3:0]

(x32)

Input

Data mask: Determines which bytes are written during WRITE operations.

For x16 LPDDR, unused DM balls become RFU.

RAS# Input

Row select: Specifies the command to execute.

WE# Input

Write enable: Specifies the command to execute.

DQ[15:0]

(x16)

DQ[31:0]

(x32)

Input/

output

Data bus: Data inputs/outputs.

DQ[31:16] are RFU for x16 LPDDR devices.

LDQS, UDQS

(x16)

DQS[3:0]

(x32)

Input/

output

Data strobe: Coordinates READ/WRITE transfers of data; one DQS per DQ byte.

For x16 LPDDR, unused DQS balls become RFU.

TQ Output

Temperature sensor output: TQ HIGH when LPDDR T

J

exceeds 85°C.

V

DD

Supply

V

DD

: LPDDR power supply.

V

DDQ

Supply

V

DDQ

: LPDDR I/O power supply.

V

SSQ

Supply

V

SSQ

: LPDDR I/O ground.

Table 4: Non-Device-Specific Ball Descriptions

Symbol Type Description

V

SS

Supply

V

SS

: Shared ground.

NC

–

No connect: Not internally connected.

RFU

1

–

Reserved for future use.