ISL9000A

11

FN6391.3

October 15, 2015

Submit Document Feedback

Functional Description

The ISL9000A contains two high performance LDO’s. High

performance is achieved through a circuit that delivers fast

transient response to varying load conditions. In a quiescent

condition, the ISL9000A adjusts its biasing to achieve the lowest

standby current consumption.

The device also integrates current limit protection, smart thermal

shutdown protection, staged turn-on and soft-start. Smart

thermal shutdown protects the device against overheating.

Staged turn-on and soft-start minimize start-up input current

surges without causing excessive device turn-on time.

Power Control

The ISL9000A has two separate enable pins (EN1 and EN2) to

individually control power to each of the LDO outputs. When both

EN1 and EN2 are LOW, the device is in shutdown mode. During

this condition, all on-chip circuits are OFF, and the device draws

minimum current, typically less than 0.1µA.

When one or both of the enable pins are asserted, the device first

polls the output of the UVLO detector to ensure that VIN voltage is

at least about 2.1V. Once verified, the device initiates a start-up

sequence. During the start-up sequence, trim settings are first

read and latched. Then, sequentially, the bandgap, reference

voltage and current generation circuitry power-up. Once the

references are stable, a fast-start circuit quickly charges the

external reference bypass capacitor (connected to the CBYP pin)

to the proper operating voltage. After the bypass capacitor has

been charged, the LDOs power-up in their specified sequence.

Soft-start circuitry integrated into each LDO limits the initial

ramp-up rate to about 30µs/V to minimize current surge.

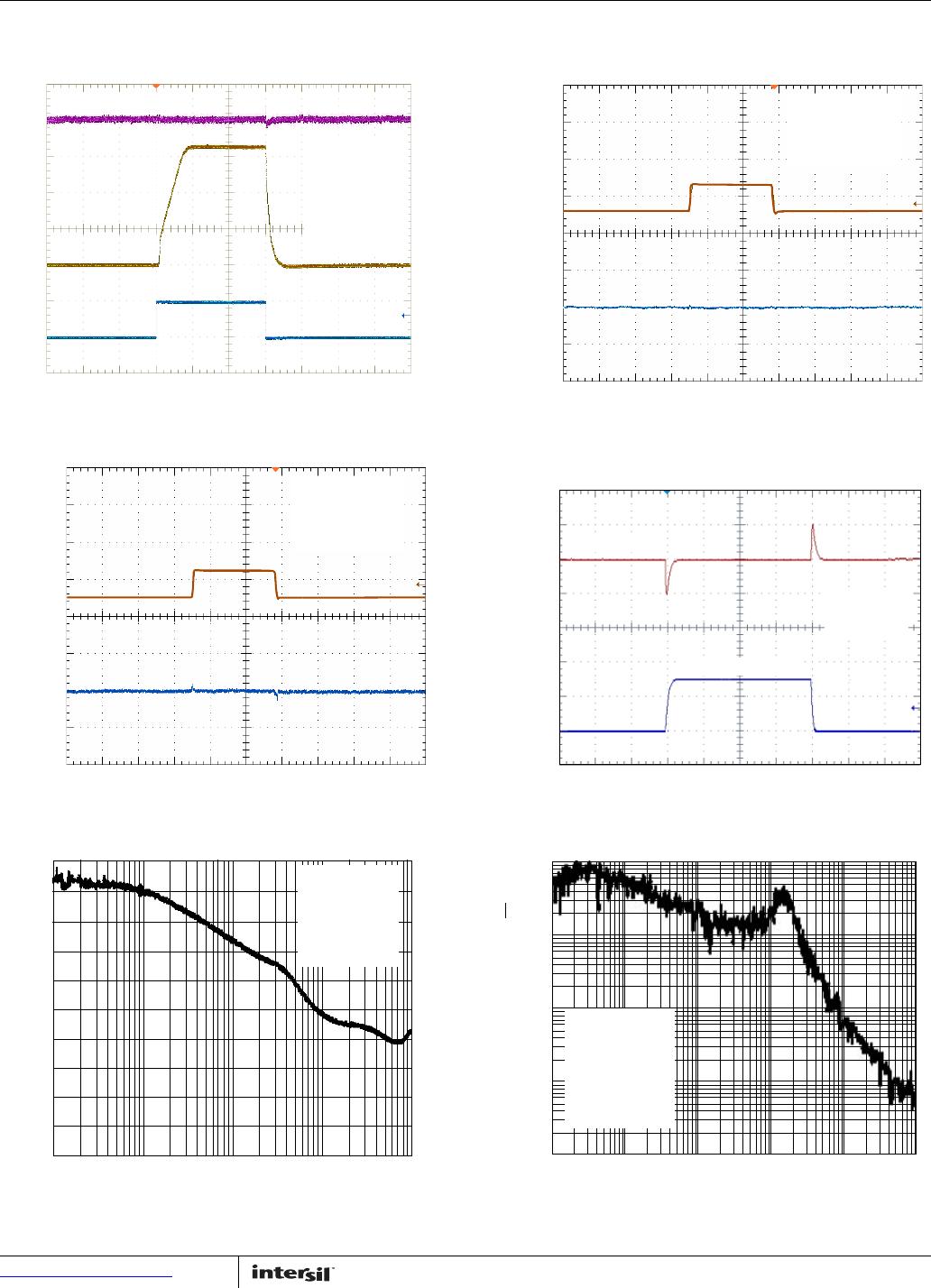

If EN1 is brought HIGH, and EN2 goes HIGH before the VO1

output stabilizes, the ISL9000A delays the VO2 turn-on until the

VO1 output reaches its target level.

If EN2 is brought high, and EN1 goes HIGH before VO2 starts its

output ramp, then VO1 turns on first and, the ISL9000A delays

the VO2 turn-on until the VO1 output reaches its target level.

If EN2 is brought HIGH, and EN1 goes HIGH after VO2 starts its

output ramp, then the ISL9000A immediately starts to ramp up

the VO1 output.

If both EN1 and EN2 are brought HIGH at the same time, the VO1

output has priority, and is always powered up first.

During operation, whenever the VIN voltage drops below about

1.8V, the ISL9000A immediately disables both LDO outputs.

When VIN rises back above 2.1V, the device re-initiates its

start-up sequence and LDO operation will resume automatically.

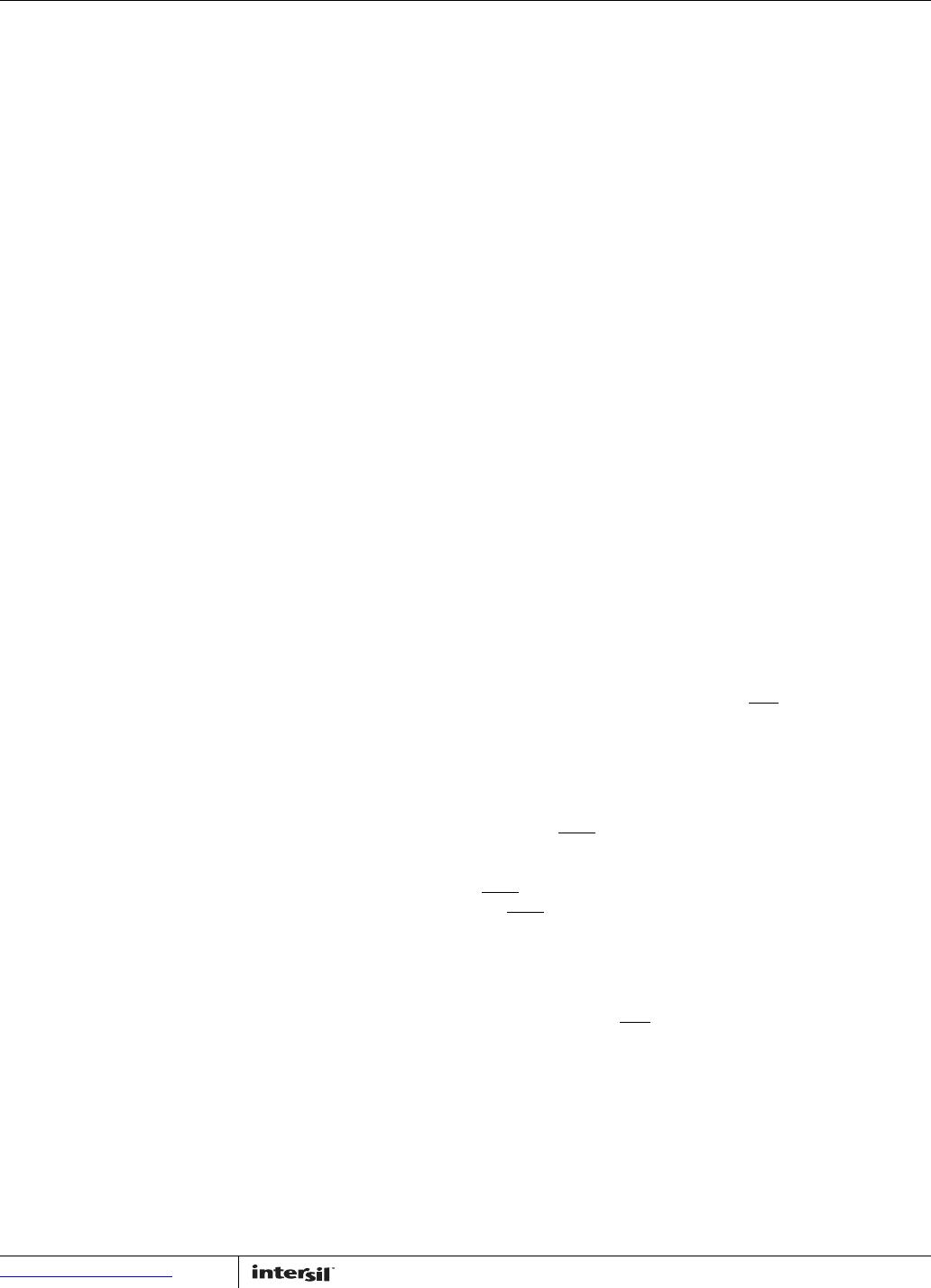

Reference Generation

The reference generation circuitry includes a trimmed bandgap,

a trimmed voltage reference divider, a trimmed current reference

generator, and an RC noise filter. The filter includes the external

capacitor connected to the CBYP pin. A 0.01µF capacitor

connected CBYP implements a 100Hz lowpass filter, and is

recommended for most high performance applications. For the

lowest noise application, a 0.1µF or greater CBYP capacitor

should be used. This filters the reference noise below the 10Hz to

1kHz frequency band, which is crucial in many noise-sensitive

applications.

The bandgap generates a zero temperature coefficient (TC)

voltage for the reference divider. The reference divider provides

the regulation reference, POR detection thresholds, and other

voltage references required for current generation and over-

temperature detection.

The current generator provides the references required for

adaptive biasing as well as references for LDO output current

limit and thermal shutdown determination.

LDO Regulation and Programmable Output

Divider

The LDO Regulator is implemented with a high-gain operational

amplifier driving a PMOS pass transistor. The design of the

ISL9000A provides a regulator that has low quiescent current,

fast transient response, and overall stability across all operating

and load current conditions. LDO stability is guaranteed for a 1µF

to 10µF output capacitor that has a tolerance better than 20%

and ESR less than 200m. The design is performance-optimized

for a 1F capacitor. Unless limited by the application, use of an

output capacitor value above 4.7µF is not normally needed as

LDO performance improvement is minimal.

Each LDO uses an independently trimmed 1V reference. An

internal resistor divider drops the LDO output voltage down to 1V.

This is compared to the 1V reference for regulation. The resistor

division ratio is programmed in the factory to one of the following

output voltages: 1.5V, 1.8V, 1.85V, 2.5V, 2.6V, 2.7V, 2.8V, 2.85V,

2.9V, 3.0V, and 3.3V.

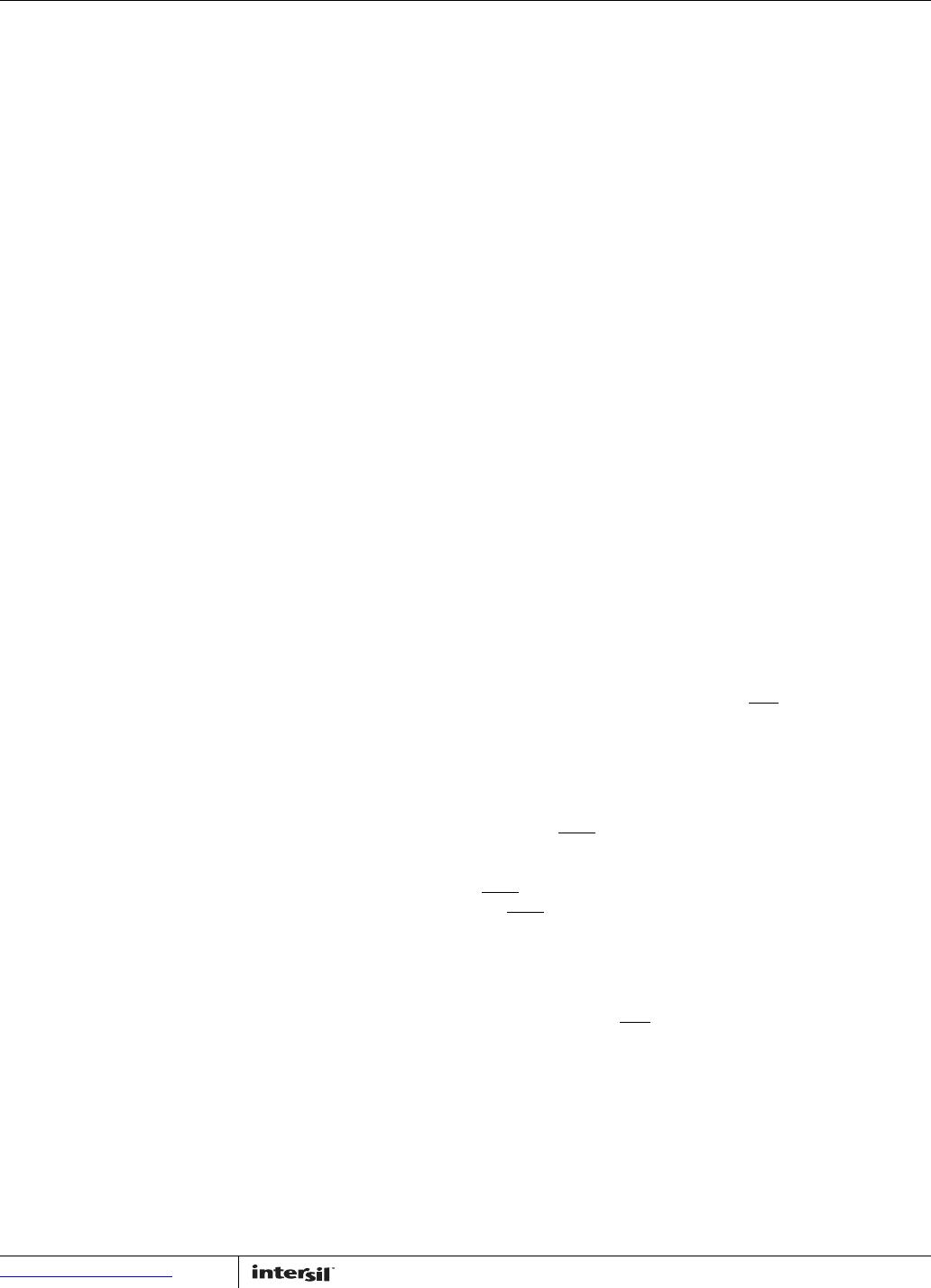

Power-On Reset Generation

Each LDO has a separate Power-on Reset signal generation

circuit which outputs to the respective POR

pins. The POR signal

is generated as follows:

A POR comparator continuously monitors the output of each LDO.

The LDO enters a power-good state when the output voltage is

above 94% of the expected output voltage for a period exceeding

the LDO PGOOD entry delay time. In the power-good state, the

open-drain PORx

output is in a high-impedance state. An internal

100k pull-up resistor pulls the pin up to the respective LDO

output voltage. An external resistor can be added between the

PORx

output and the LDO output for a faster rise time, however,

the PORx

output should not connect through an external resistor to

a supply greater than the associated LDO voltage.

The power-good state is exited when the LDO output falls below

90% of the expected output voltage for a period longer than the

PGOOD exit delay time. While power-good is false, the ISL9000A

pulls the respective POR

pin low.

For LDO-1, the PGOOD entry delay time is fixed at about 2ms

while the PGOOD exit delay is about 25µs. For LDO-2, the PGOOD

entry and exit delays are determined by the value of the external

capacitor connected to the CPOR pin. For a 0.01µF capacitor, the

entry and exit delays are 200ms and 25µs respectively. Larger or

smaller capacitor values will yield proportionately longer or

shorter delay times. The POR exit delay should never be allowed

to be less than 10µs to ensure sufficient immunity against

transient induced false POR triggering.