DMOS Dual Full-Bridge PWM Motor Driver

With Overcurrent Protection

A4987

15

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

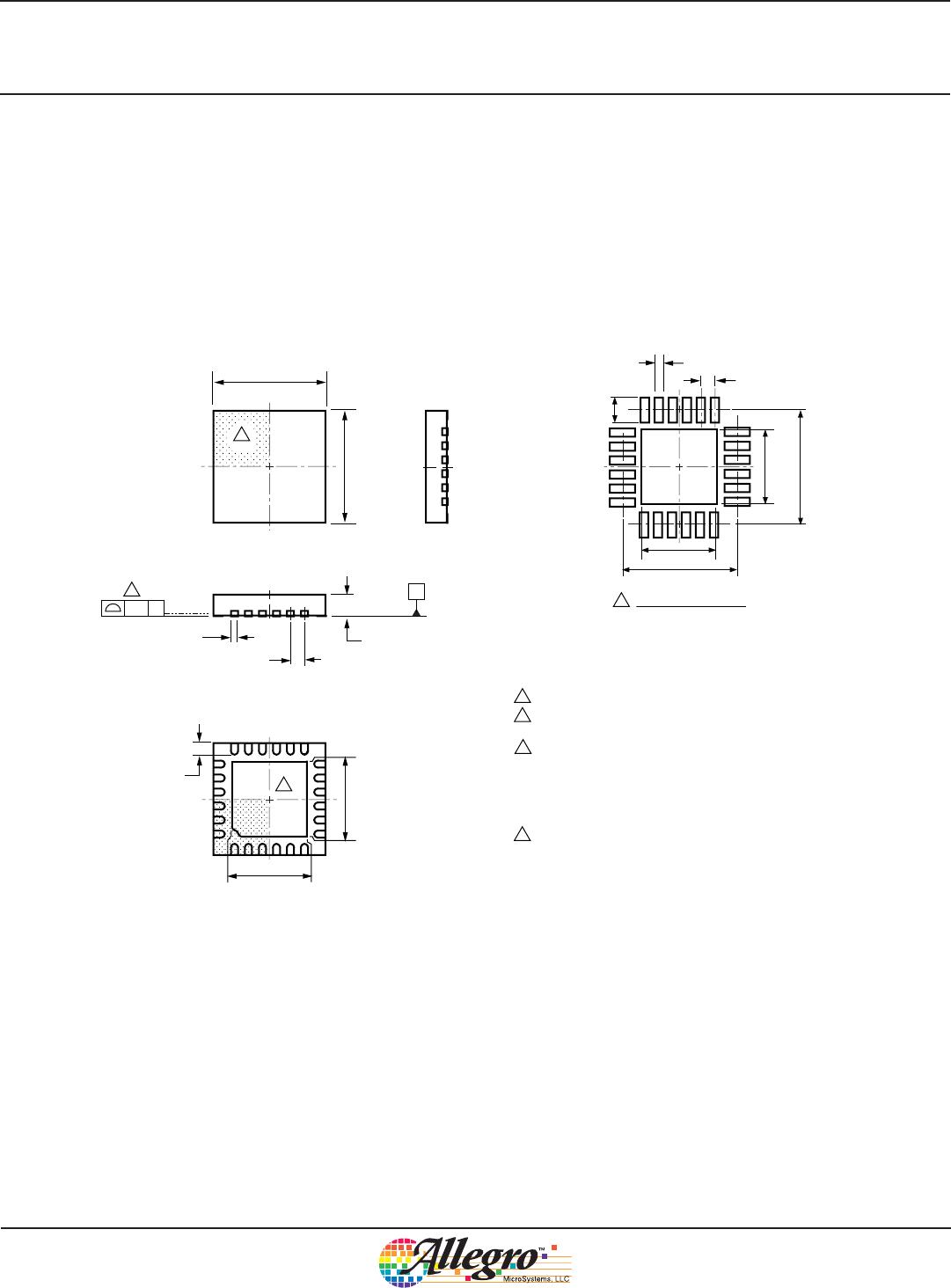

ES Package, 24-Pin QFN with Exposed Thermal Pad

0.95

C

SEATING

PLANE

C0.08

25X

24

24

2

1

1

2

24

2

1

A

A

Terminal #1 mark area

Coplanarity includes exposed thermal pad and terminals

B

Exposed thermal pad (reference only, terminal #1

identifier appearance at supplier discretion)

For Reference Only; not for tooling use (reference JEDEC MO-220WGGD)

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

C

D

D

C

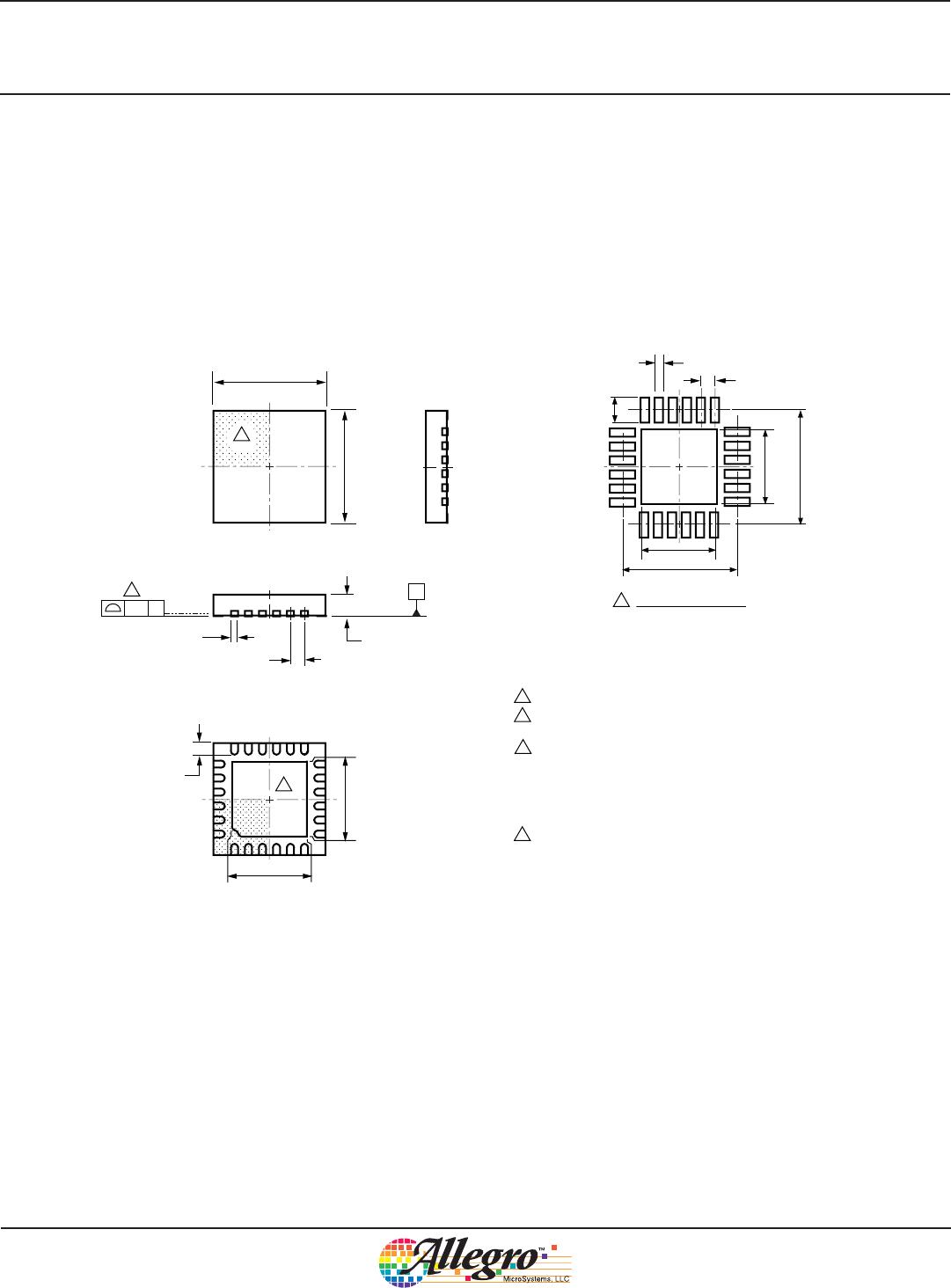

Reference land pattern layout (reference IPC7351

QFN50P400X400X80-25W6M)

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary

to meet application process requirements and PCB layout tolerances; when

mounting on a multilayer PCB, thermal vias at the exposed thermal pad land

can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

4.10

0.30

0.50

4.10

0.50 BSC

4.00 ±0.15

4.00 ±0.15

2.70

2.70

2.70

2.70

0.75 ±0.05

0.45 MAX

B

PCB Layout Reference View

0.25

+0.05

–0.07