DMOS Dual Full-Bridge PWM Motor Driver

With Overcurrent Protection

A4987

7

Allegro MicroSystems, LLC

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

www.allegromicro.com

Charge Pump (CP1 and CP2). The charge pump is used to

generate a gate supply greater than that of VBB for driving the

source-side FET gates. A 0.1 μF ceramic capacitor, should be

connected between CP1 and CP2. In addition, a 0.1 μF ceramic

capacitor is required between VCP and VBB, to act as a reservoir

for operating the high-side FET gates.

Capacitor values should be Class 2 dielectric ±15% maximum,

or tolerance R, according to EIA (Electronic Industries Alliance)

specifications.

V

REG

(VREG). This internally-generated voltage is used to

operate the sink-side FET outputs. The nominal output voltage

of the VREG terminal is 7 V. The VREG pin must be decoupled

with a 0.22 μF ceramic capacitor to ground. V

REG

is internally

monitored. In the case of a fault condition, the FET outputs of the

A4987 are disabled.

Capacitor values should be Class 2 dielectric ±15% maximum,

or tolerance R, according to EIA (Electronic Industries Alliance)

specifications.

Shutdown. In the event of a fault, overtemperature (excess T

J

)

or an undervoltage (on VCP), the FET outputs of the A4987 are

disabled until the fault condition is removed. At power-on, the

UVLO (undervoltage lockout) circuit disables the FET outputs

and resets the translator to the Home state.

Sleep Mode (

¯

S

¯

¯

L

¯

¯

E

¯

¯

E

¯

¯

P

¯

). To minimize power consumption

when the motor is not in use, this input disables much of the

internal circuitry including the output FETs, current regulator, and

charge pump. A logic low on the S

¯

¯

L

¯

¯

E

¯

¯

E

¯

¯

P

¯

pin puts the A4987 into

Sleep mode. When emerging from Sleep mode, in order to allow

the charge pump to stabilize, provide a delay of 1 ms before issu-

ing a logic command.

Mixed Decay Operation. The bridge operates in Mixed

Decay mode, as shown in figures 5 through 7. As the trip point

is reached, the A4987 initially goes into a fast decay mode for

31.25% of the off-time, t

OFF

. After that, it switches to Slow Decay

mode for the remainder of t

OFF

. A timing diagram for this feature

appears in figure 4.

Synchronous Rectification. When a PWM-off cycle is

triggered by an internal fixed-off time cycle, load current recir-

culates in Mixed Decay mode. This synchronous rectification

feature turns on the appropriate FETs during current decay, and

effectively shorts out the body diodes with the low FET R

DS(ON)

.

This reduces power dissipation significantly, and can eliminate

the need for external Schottky diodes in many applications. Syn-

chronous rectification turns off when the load current approaches

zero (0 A), preventing reversal of the load current.

t →

Fixed off-time

5 A / div.

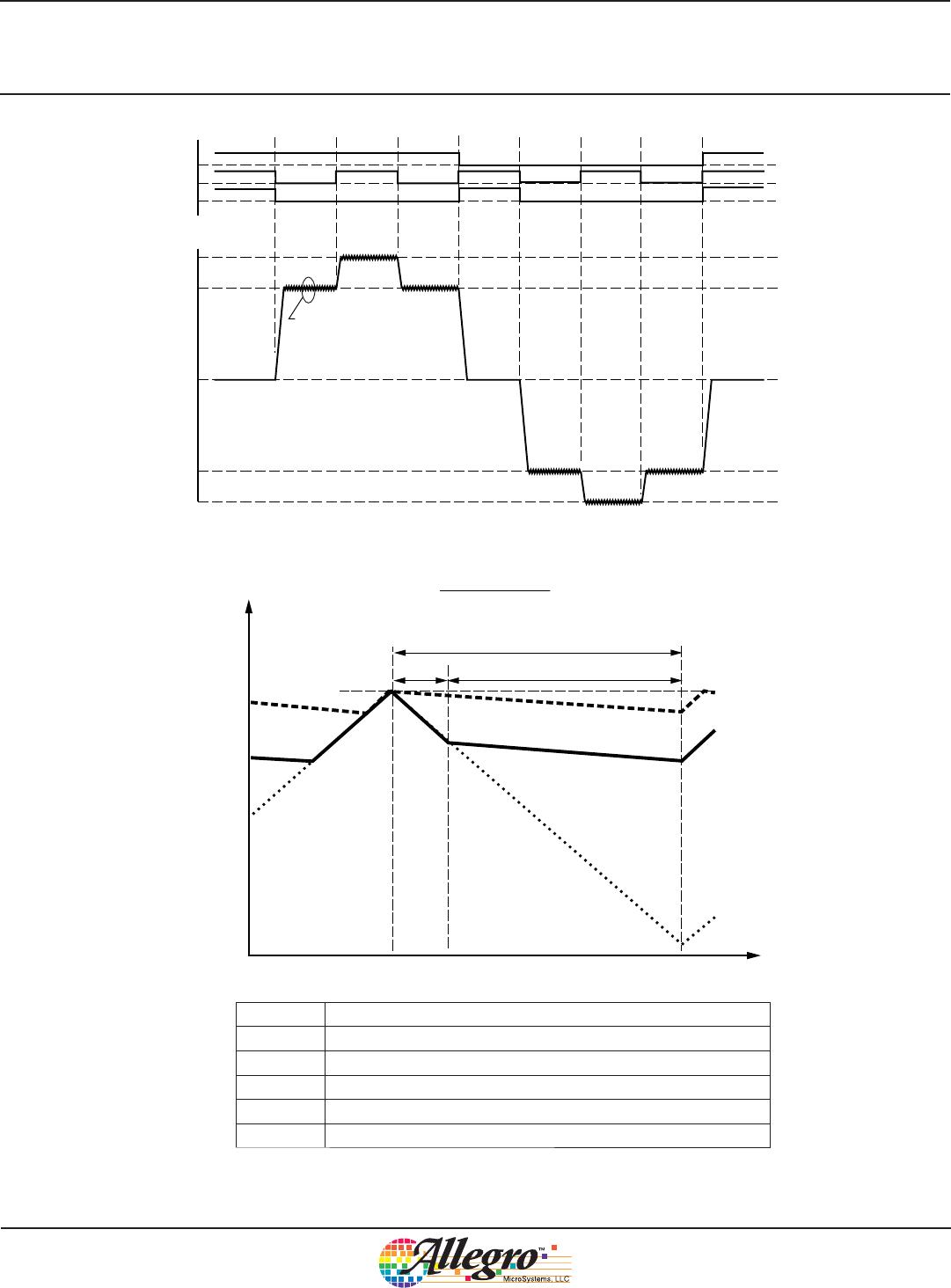

t →

5 A / div.

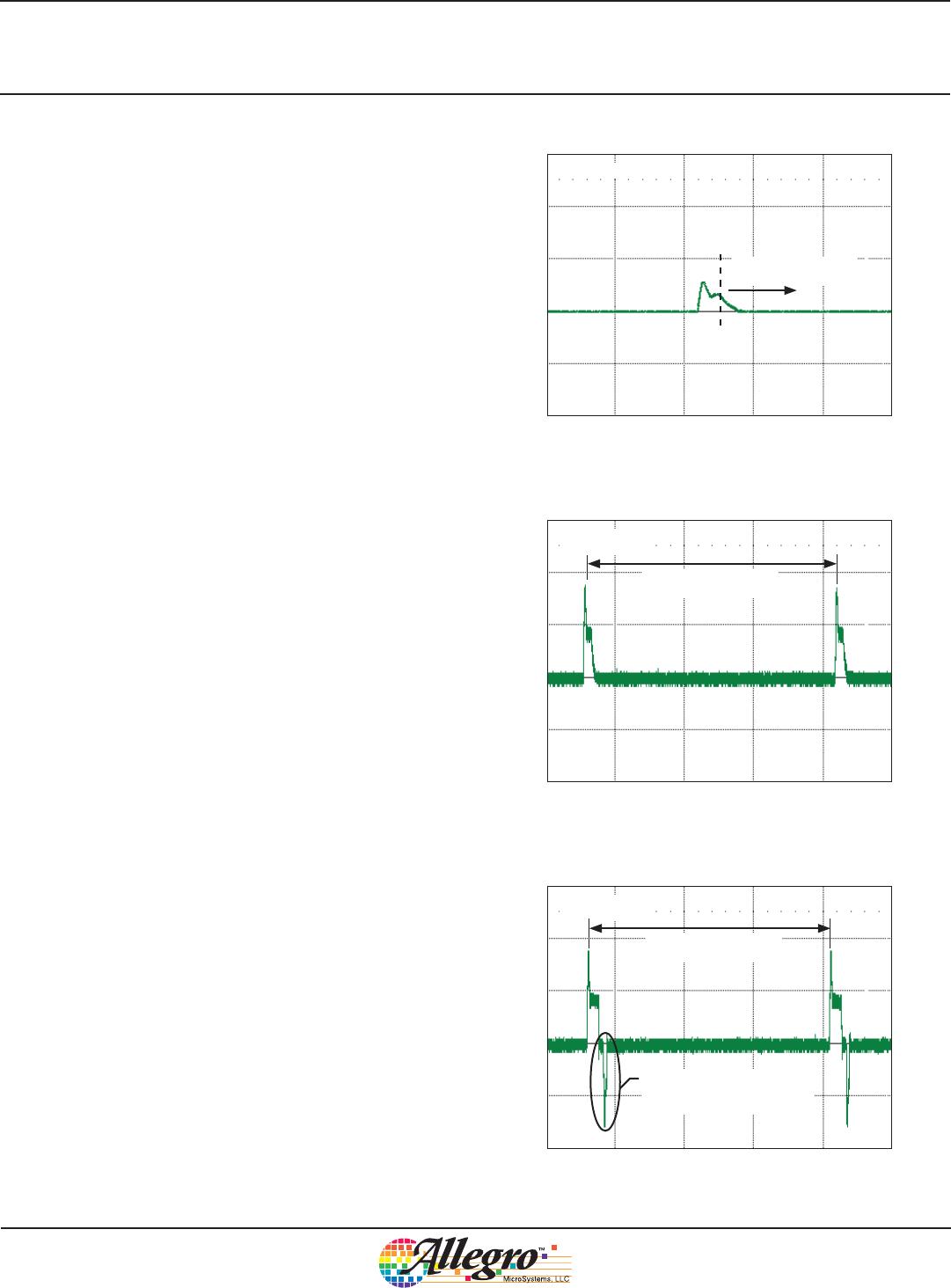

Figure 2. Shorted load (OUTxA → OUTxB) in

Slow decay mode

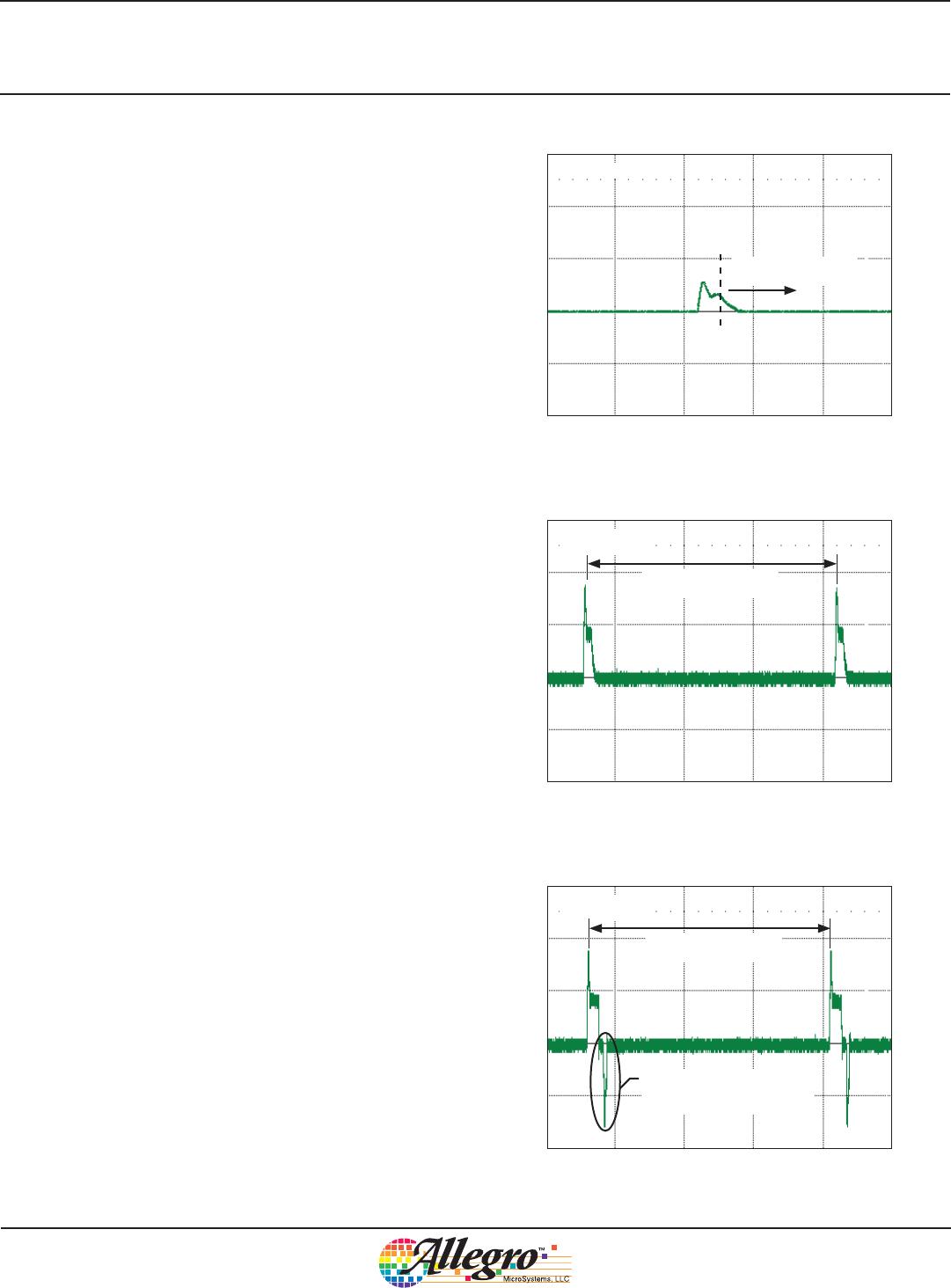

Figure 3. Shorted load (OUTxA → OUTxB) in Mixed decay mode

Fixed off-time

Fast decay portion

(direction change)

t →

Fault latched

5 A / div.

Figure 1. Short-to-ground event