6.42

15

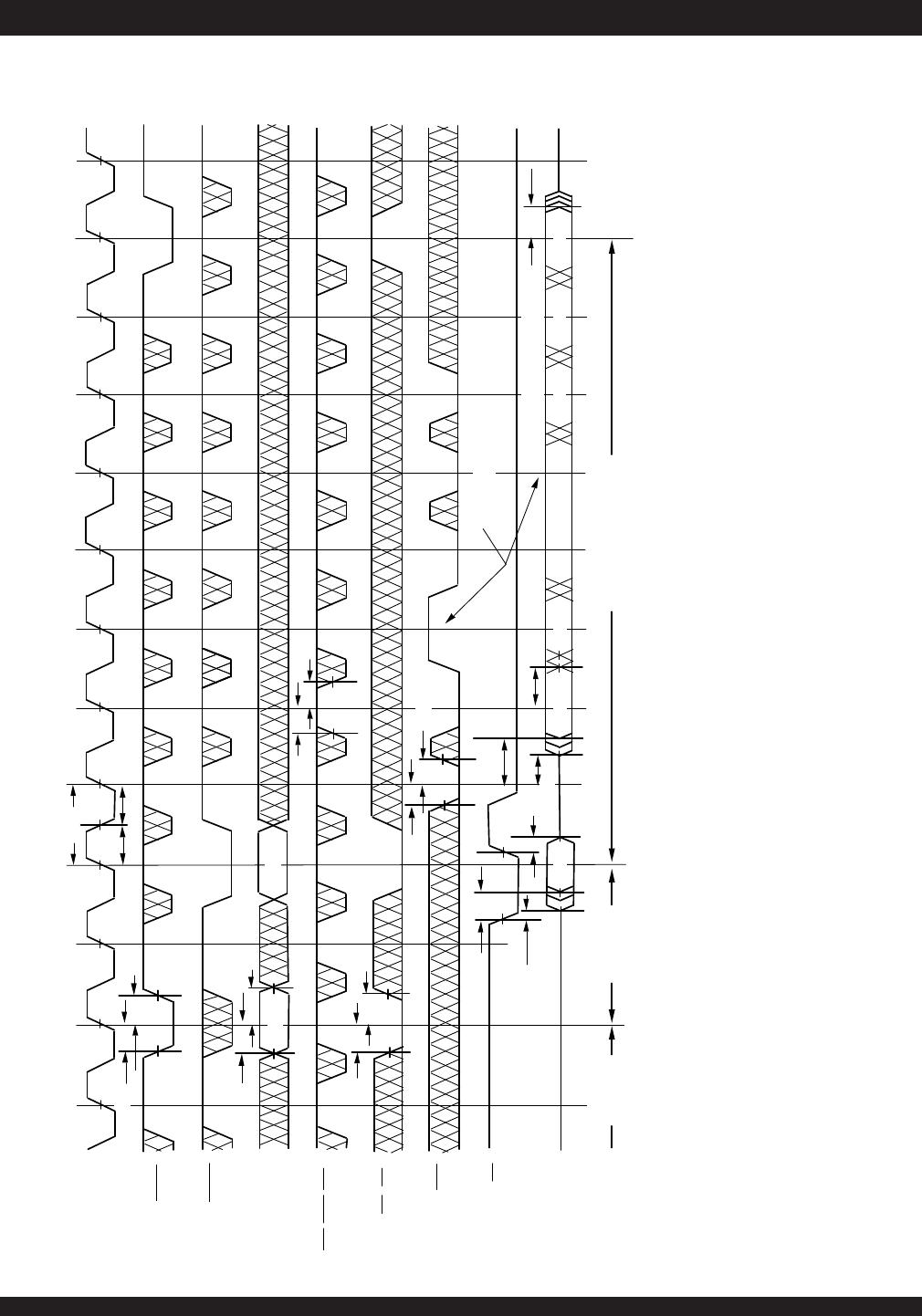

IDT71V67603, IDT71V67803, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with

3.3V I/O, Pipelined Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges

NOTES:

1. ZZ input is LOW, BWE is HIGH and LBO is Don't Care for this cycle.

2. O4 (Aw) represents the final output data in the burst sequence of the base address Aw. I1 (Ax) represents the first input from the external address Ax. I1 (Ay) represents the first input

from the external address Ay; I2 (Ay) represents the next input data in the burst sequence of the base address Ay, etc. where A0 and A1 are advancing for the four word burst in the

sequence defined by the state of the LBO input. In the case of input I2 (Ay) this data is valid for two cycles because ADV is high and has suspended the burst.

3. CS

0 timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

Timing Waveform of Write Cycle No. 1 — GW Controlled

(1,2,3)

D

D

R

E

S

S

C

L

K

A

D

S

P

A

D

S

C

t

C

Y

C

t

S

S

t

H

S

t

C

H

t

C

L

t

H

A

t

S

A

A

x

A

y

A

z

A

D

V

D

A

T

A

O

U

T

O

E

t

H

C

t

S

D

I

1

(

A

x

)

I

1

(

A

z

)

I

2

(

A

y

)

t

H

D

t

O

H

Z

D

A

T

A

I

N

t

H

A

V

O

3

(

A

w

)

O

4

(

A

w

)

C

E

,

C

S

1

t

H

W

G

W

t

S

W

(

N

o

t

e

3

)

I

2

(

A

z

)

B

u

r

s

t

W

r

i

t

e

B

u

r

s

t

R

e

a

d

B

u

r

s

t

W

r

i

t

e

S

i

n

g

l

e

W

r

i

t

e

I

3

(

A

z

)

I

4

(

A

y

)

I

3

(

A

y

)

I

2

(

A

y

)

t

S

A

V

(

A

D

V

H

I

G

H

s

u

s

p

e

n

d

s

b

u

r

s

t

)

I

1

(

A

y

)

G

W

i

s

i

g

n

o

r

e

d

w

h

e

n

A

D

S

P

i

n

i

t

i

a

t

e

s

a

c

y

c

l

e

a

n

d

i

s

s

a

m

p

l

e

d

o

n

t

h

e

n

e

x

t

c

l

o

c

k

r

i

s

i

n

g

e

d

g

e

t

S

C

5

3

1

0

d

r

w

1

0

,