REV. E

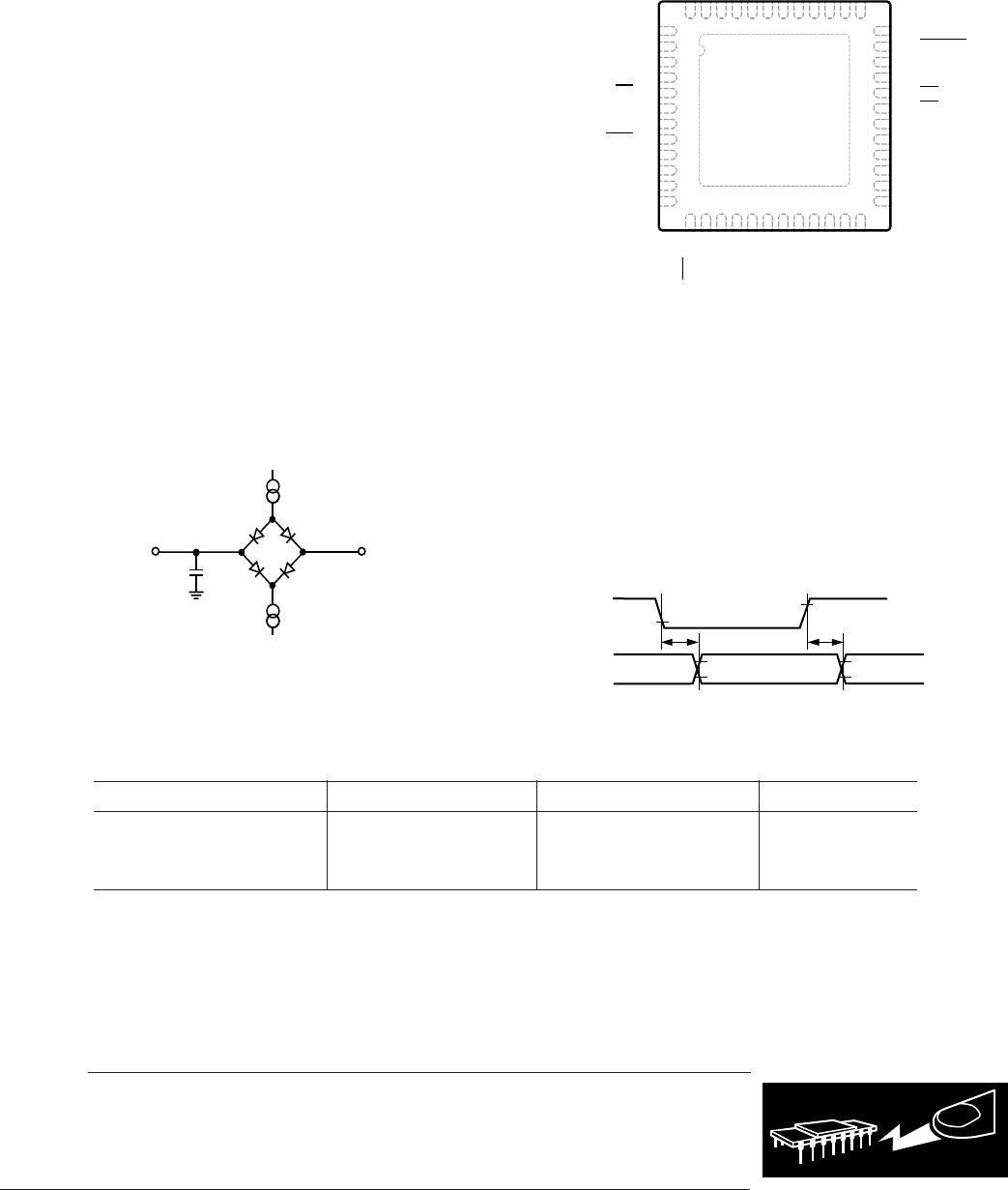

AD7660

–5–

PIN FUNCTION DESCRIPTIONS

Pin

No. Mnemonic Type Description

1 AGND P Analog Power Ground Pin

2 AVDD P Input Analog Power Pins. Nominally 5 V.

3, 6, 7, NC No Connect

40–42,

44–48

4 DGND DI Must Be Tied to Digital Ground

5OB/2C DI Straight Binary/Binary Twos Complement. When OB/2C is HIGH, the digital output is

straight binary; when LOW, the MSB is inverted resulting in a twos complement output from

its internal shift register.

8 SER/PAR DI Serial/Parallel Selection Input. When LOW, the Parallel Port is selected; when HIGH, the

Serial Interface Mode is selected and some bits of the DATA bus are used as a Serial Port.

9–12 D[0:3] DO Bit 0 to Bit 3 of the Parallel Port Data Output Bus. These pins are always outputs regardless

of the state of SER/PAR.

13 D4 DI/O When SER/PAR is LOW, this output is used as the Bit 4 of the Parallel Port Data Output Bus.

or EXT/INT When SER/PAR is HIGH, this input, part of the Serial Port, is used as a digital select input

for choosing the internal or an external data clock. With EXT/INT tied LOW, the internal

clock is selected on the SCLK output. With EXT/INT set to a logic HIGH, output data is

synchronized to an external clock signal connected to the SCLK input.

14 D5 DI/O When SER/PAR is LOW, this output is used as the Bit 5 of the Parallel Port Data Output Bus.

or INVSYNC When SER/PAR is HIGH, this input, part of the Serial Port, is used to select the active state

of the SYNC signal. When LOW, SYNC is active HIGH. When HIGH, SYNC is active LOW.

15 D6 DI/O When SER/PAR is LOW, this output is used as the Bit 6 of the Parallel Port Data Output Bus.

or INVSCLK When SER/PAR is HIGH, this input, part of the Serial Port, is used to invert the SCLK

signal. It is active in both Master and Slave Modes.

16 D7 DI/O When SER/PAR is LOW, this output is used as the Bit 7 of the Parallel Port Data Output Bus.

or RDC/SDIN When SER/PAR is HIGH, this input, part of the Serial Port, is used as either an external data

input or a Read Mode selection input depending on the state of EXT/INT.

When EXT/INT is HIGH, RDC/SDIN could be used as a data input to daisy-chain the

conversion results from two or more ADCs onto a single SDOUT line. The digital data level

on SDIN is output on DATA with a delay of 16 SCLK periods after the initiation of the read

sequence.

When EXT/INT is LOW, RDC/SDIN is used to select the Read Mode. When RDC/SDIN is

HIGH, the data is output on SDOUT during conversion. When RDC/SDIN is LOW, the

data is output on SDOUT only when the conversion is complete.

17 OGND P Input/Output Interface Digital Power Ground

18 OVDD P Input/Output Interface Digital Power. Nominally at the same supply as the supply of the host

interface (5 V or 3 V).

19 DVDD P Digital Power. Nominally at 5 V.

20 DGND P Digital Power Ground

21 D8 DO When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus.

or SDOUT When SER/PAR is HIGH, this output, part of the Serial Port, is used as a serial data output

synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7660

provides the conversion result, MSB first, from its internal shift register. The DATA format

is determined by the logic level of OB/2C. In Serial Mode, when EXT/INT is LOW, SDOUT

is valid on both edges of SCLK.

In Serial Mode, when EXT/INT is HIGH:

If INVSCLK is LOW, SDOUT is updated on the SCLK rising edge and valid on the next

falling edge.

If INVSCLK is HIGH, SDOUT is updated on the SCLK falling edge and valid on the next

rising edge.