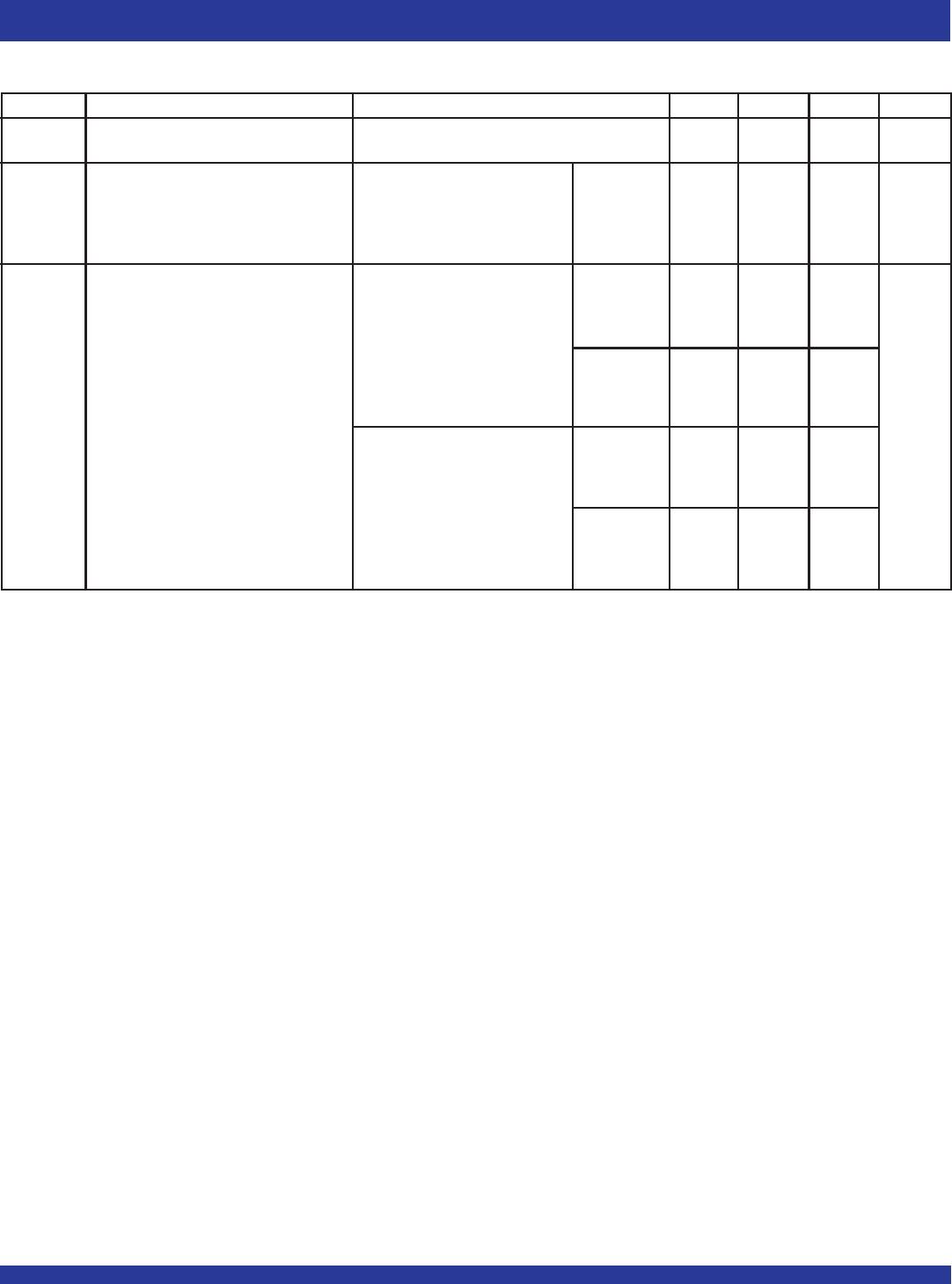

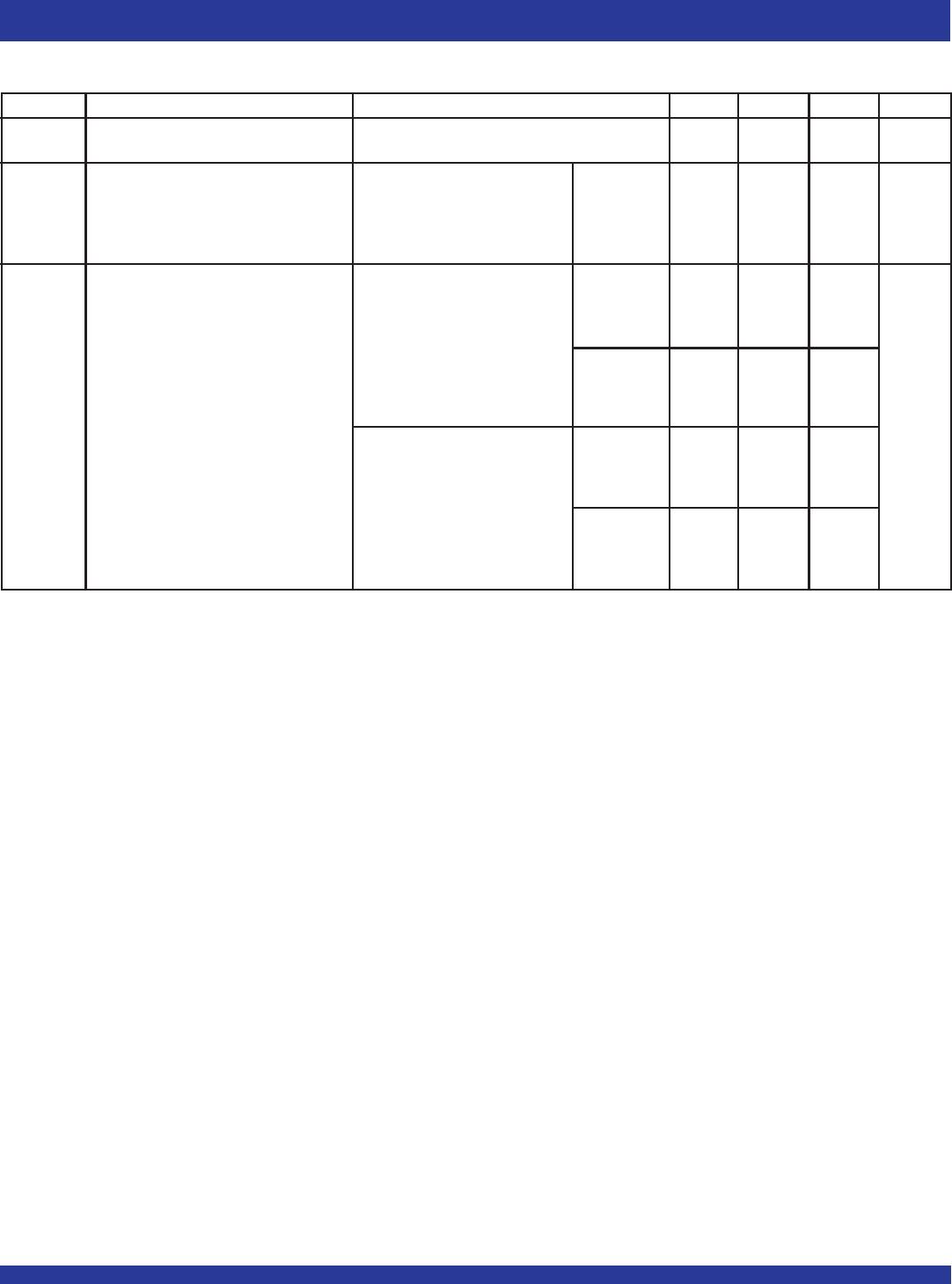

4

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT162823AT/CT

FAST CMOS 18-BIT REGISTER

Symbol Parameter Test Conditions

(1)

Min. Typ.

(2)

Max. Unit

ΔI

CC Quiescent Power Supply Current VCC = Max. — 0.5 1.5 mA

TTL Inputs HIGH VIN = 3.4V

(3)

ICCD Dynamic Power Supply Current

(4)

VCC = Max. VIN = VCC — 75 120 µ A /

Outputs Open VIN = GND MHz

xOE = xCLKEN = GND

One Input Toggling

50% Duty Cycle

IC Total Power Supply Current

(6)

VCC = Max. VIN = VCC — 0.8 1.7 mA

Outputs Open VIN = GND

f

CP = 10MHz

50% Duty Cycle

xOE = xCLKEN = GND V

IN = 3.4V — 1.3 3.2

at fi = 5MHz VIN = GND

50% Duty Cycle

One Bit Toggling

V

CC = Max. VIN = VCC — 4.2 7.1

(5)

Outputs Open VIN = GND

fCP = 10MHz

50% Duty Cycle

xOE = xCLKEN = GND VIN = 3.4V — 9.2 22.1

(5)

at fi = 2.5MHz VIN = GND

50% Duty Cycle

Eighteen Bits Toggling

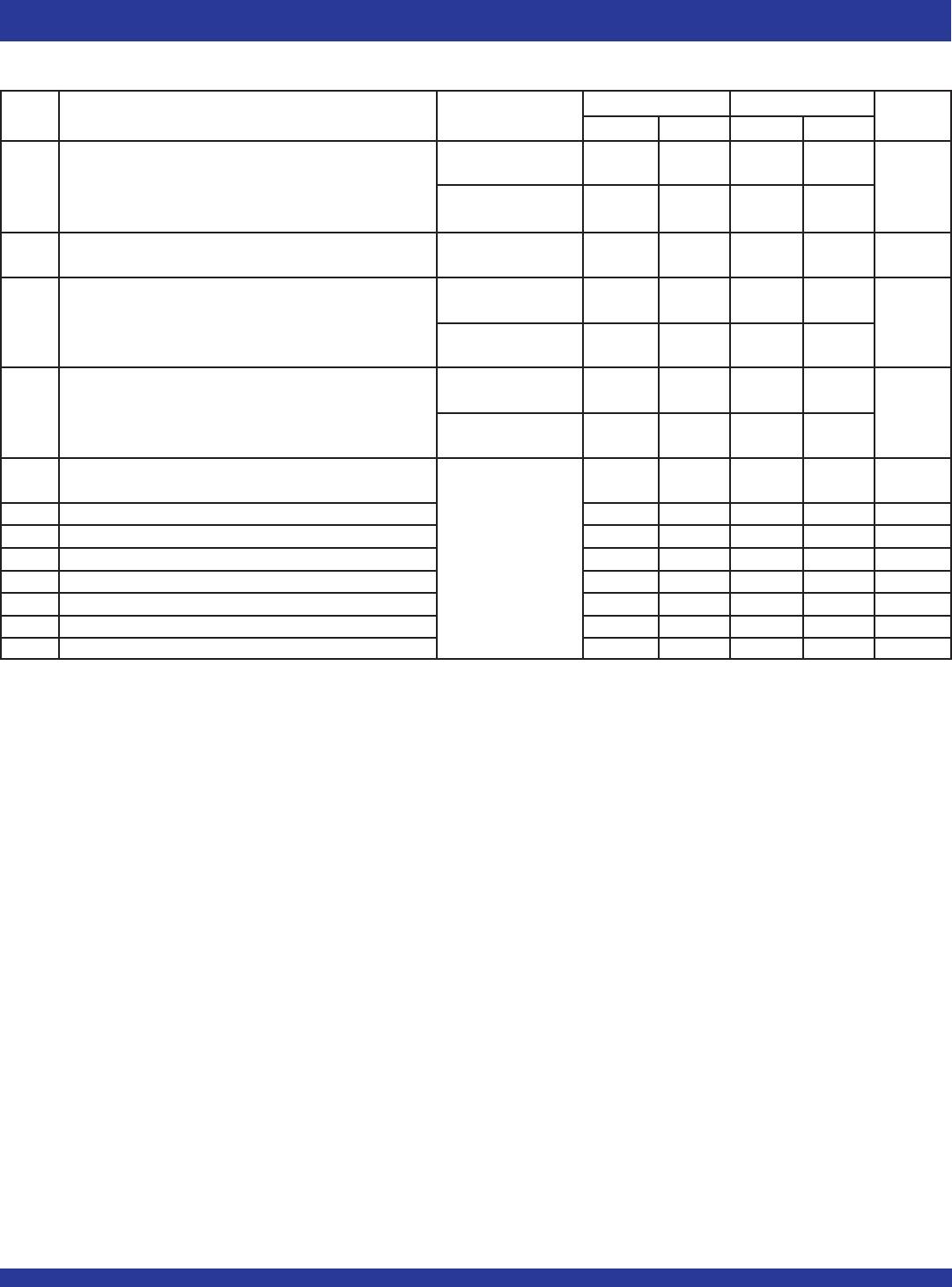

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at VCC = 5.0V, +25°C ambient.

3. Per TTL driven input (VIN = 3.4V). All other inputs at VCC or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of the ICC formula. These limits are guaranteed but not tested.

6. IC = IQUIESCENT + IINPUTS + IDYNAMIC

IC = ICC + ΔICC DHNT + ICCD (fCPNCP/2 + fiNi)

ICC = Quiescent Current (ICCL, ICCH and ICCZ)

ΔICC = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

fCP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

NCP = Number of Clock Inputs at fCP

fi = Input Frequency

Ni = Number of Inputs at fi

POWER SUPPLY CHARACTERISTICS