NB2308A

http://onsemi.com

5

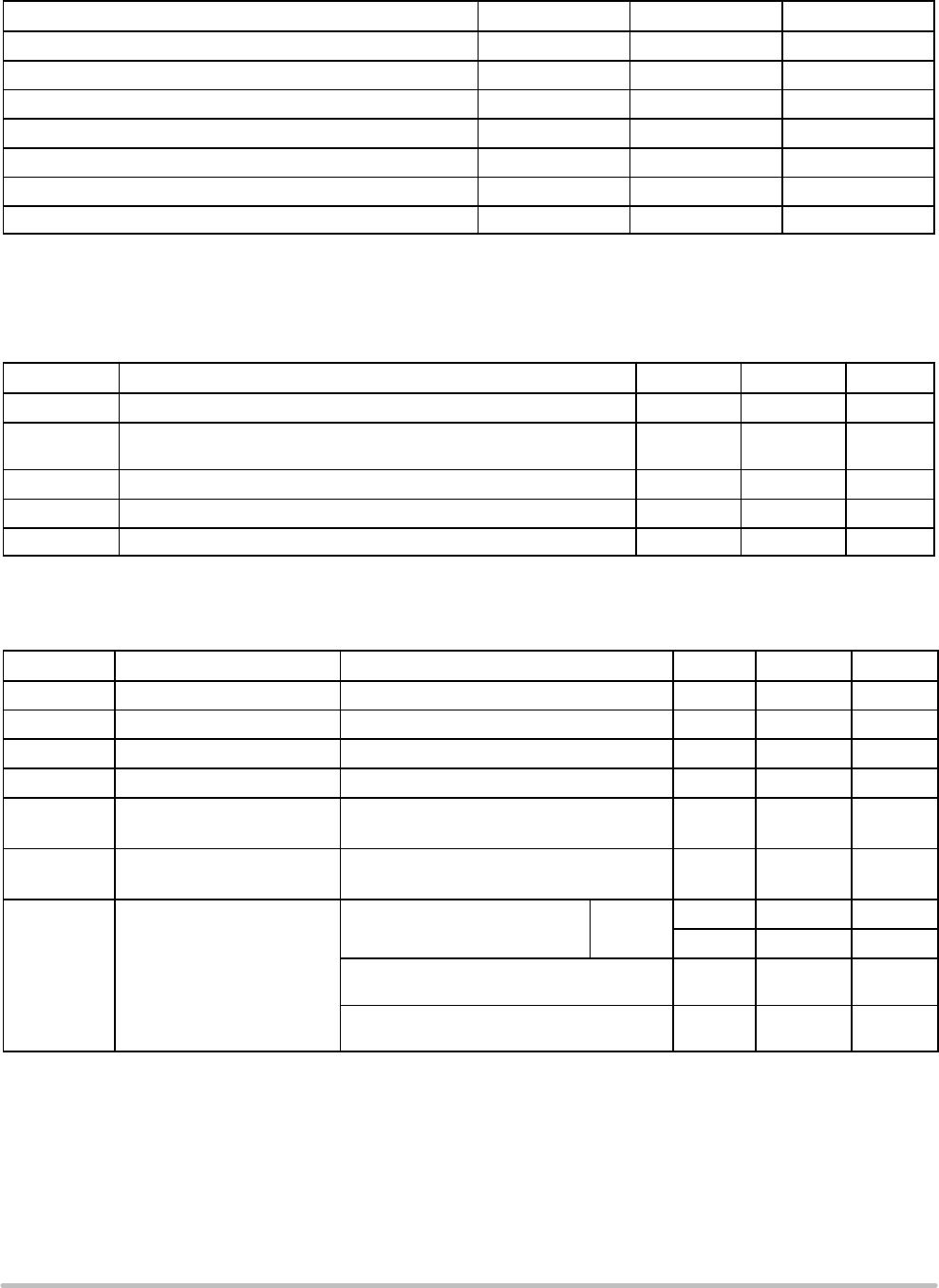

Table 7. SWITCHING CHARACTERISTICS FOR COMMERCIAL AND INDUSTRIAL TEMPERATURE DEVICES

Parameter Description Test Conditions Min Typ Max Unit

t

1

Output Frequency 30 pF load (all devices)

15 pF load (−1H, −5H)

15 pF load (−1, −2, −3, −4)

15

15

15

100

133.3

133.3

MHz

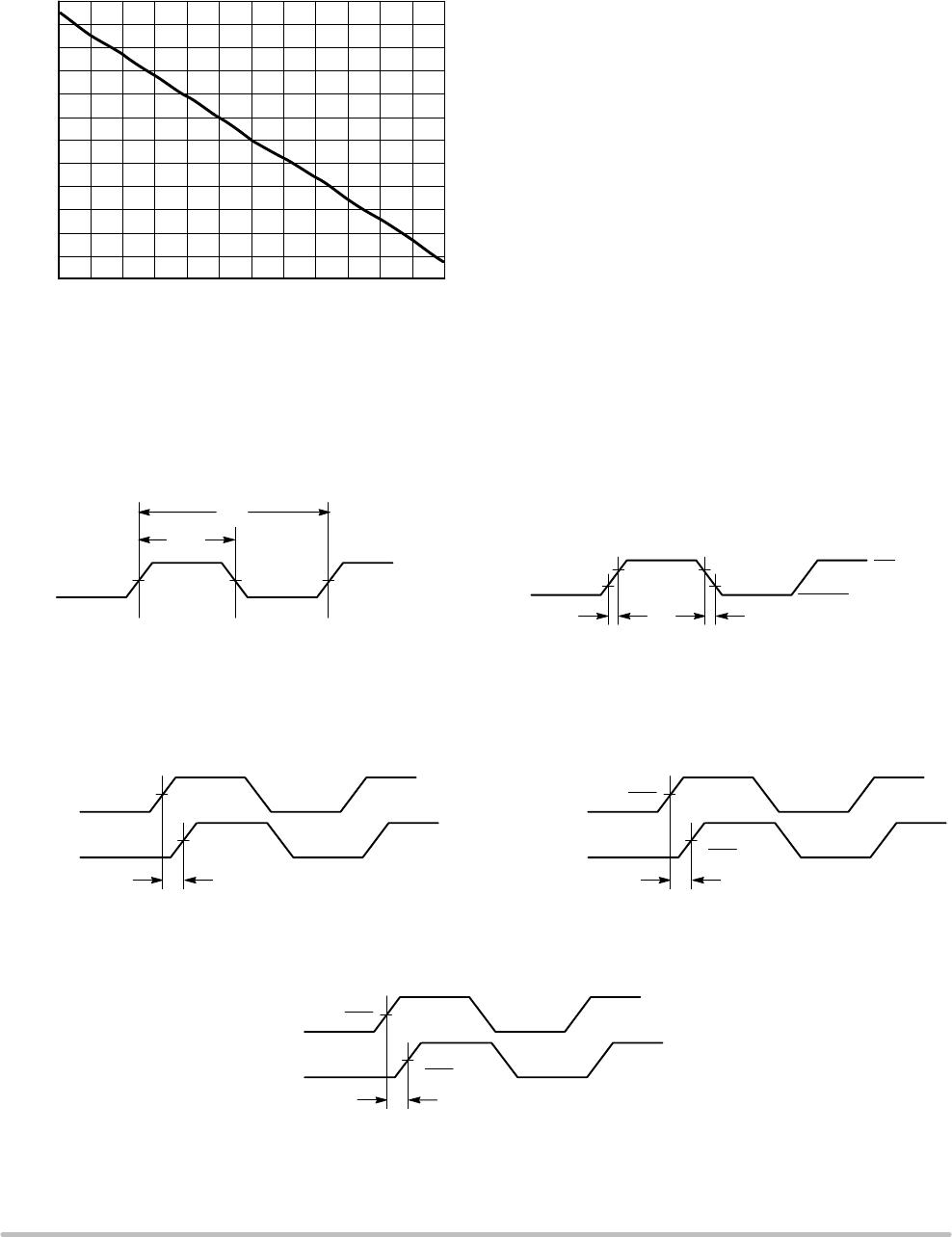

t

1

Duty Cycle = (t

2

/ t

1

) * 100

(all devices)

Measured at 1.4 V, F

OUT

= < 66.66 MHz

30 pF load

40.0 50.0 60.0

%

Measured at 1.4 V, F

OUT

= < 50 MHz

15 pF load

45.0 50.0 55.0

t

3

Output Rise Time

(−1, −2, −3, −4)

Measured between 0.8 V and 2.0 V

30 pF load

2.20

ns

Measured between 0.8 V and 2.0 V

15 pF load

1.50

Output Rise Time

(−1H, −5H)

Measured between 0.8 V and 2.0 V

30 pF load

1.50

t

4

Output Fall Time

(−1, −2, −3, −4)

Measured between 2.0 V and 0.8 V

30 pF load

2.20

ns

Measured between 0.8 V and 2.0 V

15 pF load

1.50

Output Fall Time

(−1H, −5H)

Measured between 2.0 V and 0.8 V

30 pF load

1.25

t

5

Output−to−Output Skew on same Bank

(−1, −2, −3, −4)

All outputs equally loaded 200

ps

Output−to−Output Skew

(−1H, −5H)

All outputs equally loaded 200

Output Bank A−to−Output Bank B Skew

(−1, −4, −5H)

All outputs equally loaded 200

Output Bank A−to−Output Bank B Skew

(−2, −3)

All outputs equally loaded 400

t

6

Delay, REF Rising Edge to FBK

Rising Edge

Measured at V

DD

/2 0 ±250 ps

t

7

Device−to−Device Skew Measured at V

DD

/2 on the FBK pins of the

device

0 700 ps

t

J

Cycle−to−Cycle Jitter

(−1, −1H, −4, −5H)

Measured at 66.67 MHz, loaded outputs,

15 pF load

200

ps

Measured at 66.67 MHz, loaded outputs,

30 pF load

200

Measured at 133.3 MHz, loaded outputs

15 pF load

100

Cycle−to−Cycle Jitter

(−2, −3)

Measured at 66.67 MHz, loaded outputs,

30 pF load

400

Measured at 66.67 MHz, loaded outputs,

15 pF load

400

t

LOCK

PLL Lock Time Stable power supply, valid clock presented

on REF and FBK pins

1.0 ms