4

Rev. 1.8

08/20/02

IRU1050

www.irf.com

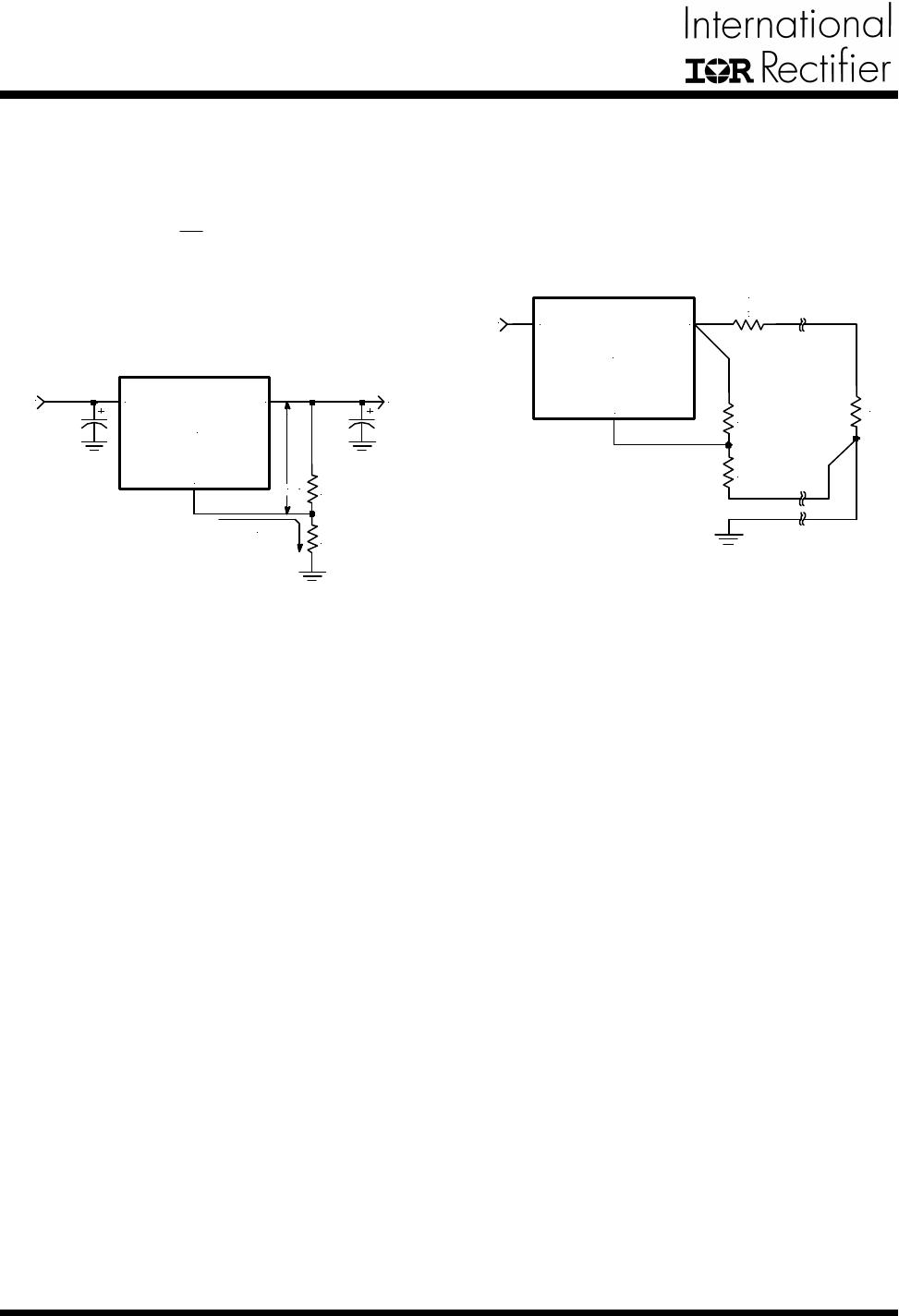

Output Voltage Setting

The IRU1050 can be programmed to any voltages in the

range of 1.25V to 5.5V with the addition of R1 and R2

external resistors according to the following formula:

Where:

VREF = 1.25V Typically

IADJ = 50mA Typically

R1 and R2 as shown in Figure 3:

Figure 3 - Typical application of the IRU1050

for programming the output voltage.

The IRU1050 keeps a constant 1.25V between the out-

put pin and the adjust pin. By placing a resistor R1 across

these two pins a constant current flows through R1, add-

ing to the IADJ current and into the R2 resistor producing

a voltage equal to the (1.25/R1)3R2 + IADJ3R2 which

will be added to the 1.25V to set the output voltage.

This is summarized in the above equation. Since the

minimum load current requirement of the IRU1050 is

10mA, R1 is typically selected to be 121V resistor so

that it automatically satisfies the minimum current re-

quirement. Notice that since IADJ is typically in the range

of 50mA it only adds a small error to the output voltage

and should only be considered when a very precise out-

put voltage setting is required. For example, in a typical

3.3V application where R1=121V and R2=200V the er-

ror due to IADJ is only 0.3% of the nominal set point.

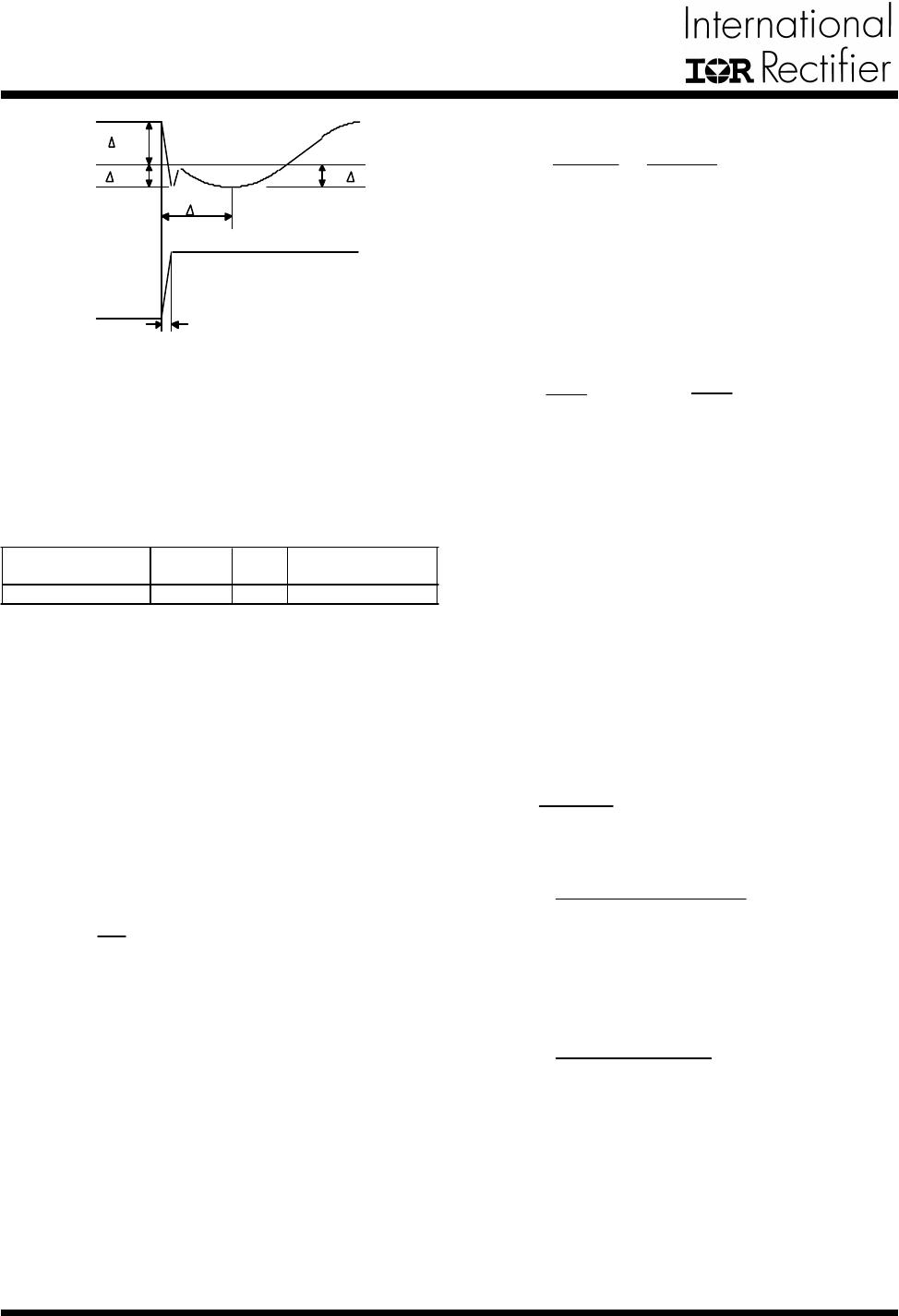

Load Regulation

Since the IRU1050 is only a three-terminal device, it is

not possible to provide true remote sensing of the output

voltage at the load. Figure 4 shows that the best load

regulation is achieved when the bottom side of R2 is

connected to the load and the top side of R1 resistor is

connected directly to the case or the VOUT pin of the

regulator and not to the load. In fact, if R1 is connected

to the load side, the effective resistance between the

regulator and the load is gained up by the factor of (1+R2/

R1), or the effective resistance will be RP(eff)=RP3(1+R2/

R1). It is important to note that for high current applica-

tions, this can represent a significant percentage of the

overall load regulation and one must keep the path from

the regulator to the load as short as possible to mini-

mize this effect.

Figure 4 - Schematic showing connection

for best load regulation.

Stability

The IRU1050 requires the use of an output capacitor as

part of the frequency compensation in order to make the

regulator stable. Typical designs for microprocessor ap-

plications use standard electrolytic capacitors with a

typical ESR in the range of 50 to 100mV and an output

capacitance of 500 to 1000mF. Fortunately as the ca-

pacitance increases, the ESR decreases resulting in a

fixed RC time constant. The IRU1050 takes advantage

of this phenomena in making the overall regulator loop

stable. For most applications a minimum of 100mF alu-

minum electrolytic capacitor such as Sanyo MVGX se-

ries, Panasonic FA series as well as the Nichicon PL

series insures both stability and good transient response.

Thermal Design

The IRU1050 incorporates an internal thermal shutdown

that protects the device when the junction temperature

exceeds the maximum allowable junction temperature.

Although this device can operate with junction tempera-

tures in the range of 1508C, it is recommended that the

selected heat sink be chosen such that during maxi-

mum continuous load operation the junction tempera-

ture is kept below this number. The example below shows

the steps in selecting the proper regulator heat sink for

the worst case current consumption using Intel 200MHz

microprocessor as the load.

VOUT

R1

R2

VIN

VREF

IADJ = 50uA

Adj

VOUT

VIN

IRU1050

R1

R2

V

IN

R

L

R

P

PARASITIC LINE

RESISTANCE

IRU1050

Adj

V

OUT

Vin

VOUT = VREF3 1+ +IADJ3R2

R2

R1

( )