MP28265 – 5A, 21V, SYNCHRONOUS STEP-DOWN CONVERTER WITH INTERNAL MOSFETS

MP28265 Rev. 0.92 www.MonolithicPower.com 9

12/2/2009 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

OPERATION

The MP28265 is a high frequency synchronous

rectified step-down switch mode converter with

built in internal power MOSFETs. It offers a very

compact solution to achieve 5A continuous

output current over a wide input supply range

with excellent load and line regulation.

The MP28265 operates in a fixed frequency,

peak current control mode to regulate the output

voltage. A PWM cycle is initiated by the internal

clock. The integrated high-side power MOSFET

is turned on and remains on until its current

reaches the value set by the COMP voltage.

When the power switch is off, it remains off until

the next clock cycle starts. If, in 90% of one PWM

period, the current in the power MOSFET does

not reach the COMP set current value, the power

MOSFET will be forced to turn off

Power Good Indicator

When the FB is below 0.85V

FB

, the PG pin will be

internally pulled low. When the FB is above

0.9V

FB

, the PG becomes an open-drain output.

Internal Regulator

Most of the internal circuitries are powered from

the 5V internal regulator. This regulator takes the

VIN input and operates in the full VIN range.

When VIN is greater than 5.0V, the output of the

regulator is in full regulation. When VIN is lower

than 5.0V, the output decreases, 0.1uF ceramic

capacitor for decoupling purpose is required.

Error Amplifier

The error amplifier compares the FB pin voltage

with the internal FB reference (V

FB

) and outputs a

current proportional to the difference between the

two. This output current is then used to charge or

discharge the internal compensation network to

form the COMP voltage, which is used to control

the power MOSFET current. The optimized

internal compensation network minimizes the

external component counts and simplifies the

control loop design.

Enable/Sync Control

EN/Sync is a digital control pin that turns the

regulator on and off. Drive EN high to turn on the

regulator, drive it low to turn it off. There is an

internal 1MEG resistor from EN/Sync to GND

thus EN/Sync can be floated to shut down the

chip.

1) Enabled by external logic H/L signal

The chip starts up once the enable signal goes

higher than EN/SYNC input high voltage (2V),

and is shut down when the signal is lower than

EN/SYNC input low voltage (0.4V). To disable

the chip, EN must be pulled low for at least 5µs.

The input is compatible with both CMOS and TTL.

2) Enabled by Vin through voltage divider.

Connect EN with VIN through a resistive voltage

divider for automatic startup as the figure 2

shows.

EN

V

IN

R

EN1

R

EN2

Figure 2—Enable Divider Circuit

Choose the value of the pull-up resistor R

EN1

and

pull-down resistor R

EN2

to reset the automatic

start-up voltage:

R

R(R

VV

EN2

EN2EN1

EN_RISINGIN_START

Ω

+

⋅=

M

M

1||

)1||

Ω

+

⋅

=

M

M

1||

)1||

EN2

EN2EN1

FALLING-ENIN_STOP

R

R(R

VV

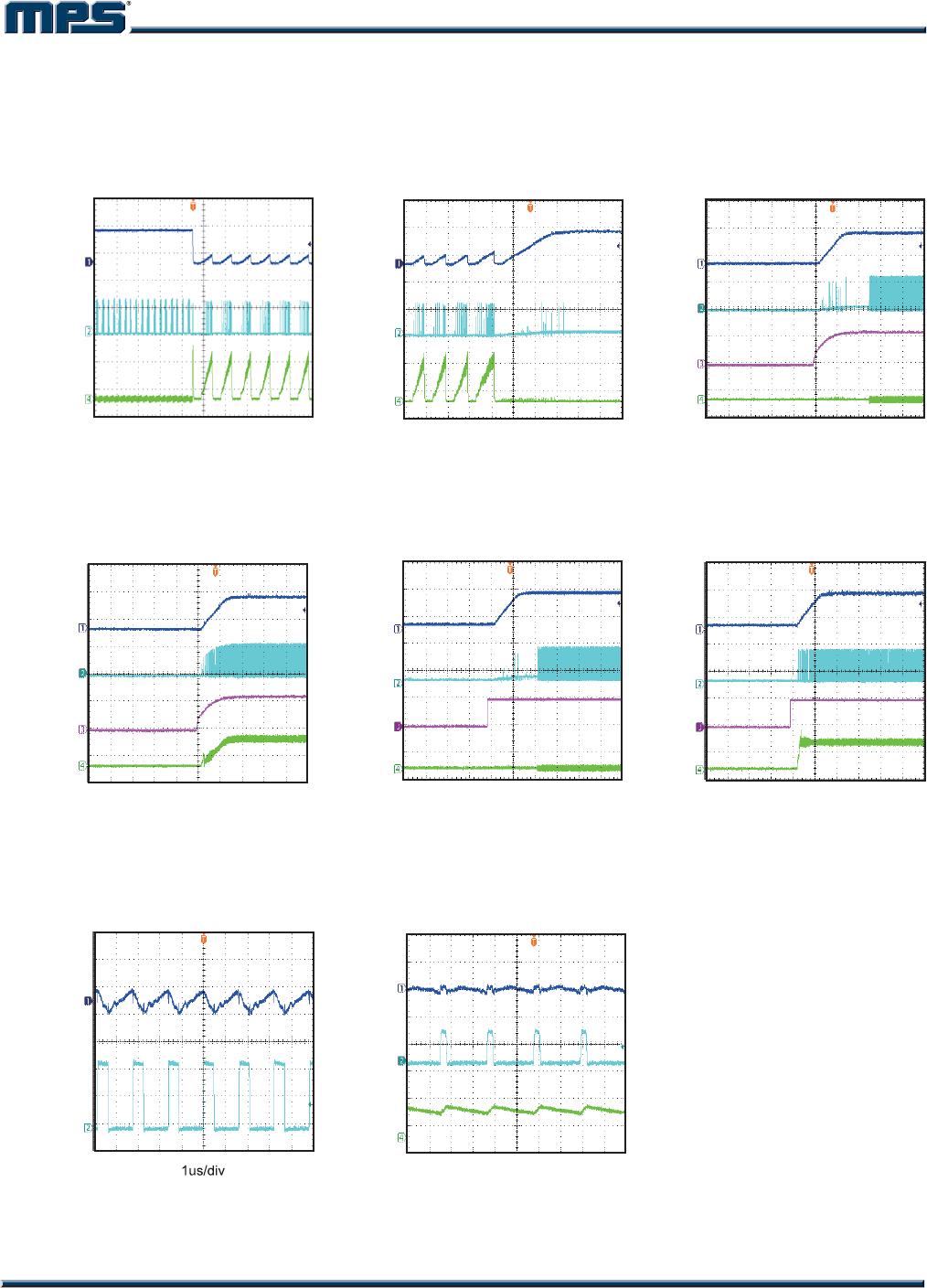

Figure 3—Startup Sequence Using EN Divider

3) Synchronized by External Sync Clock Signal

The chip can be synchronized to external clock

range from 400kHz up to 2MHz through this pin

2ms right after output voltage is set, with the

internal clock rising edge synchronized to the

external clock rising edge.