Document Number: 001-06435 Rev. *J Page 2 of 17

Contents

Pin Layout and Specifications ........................................3

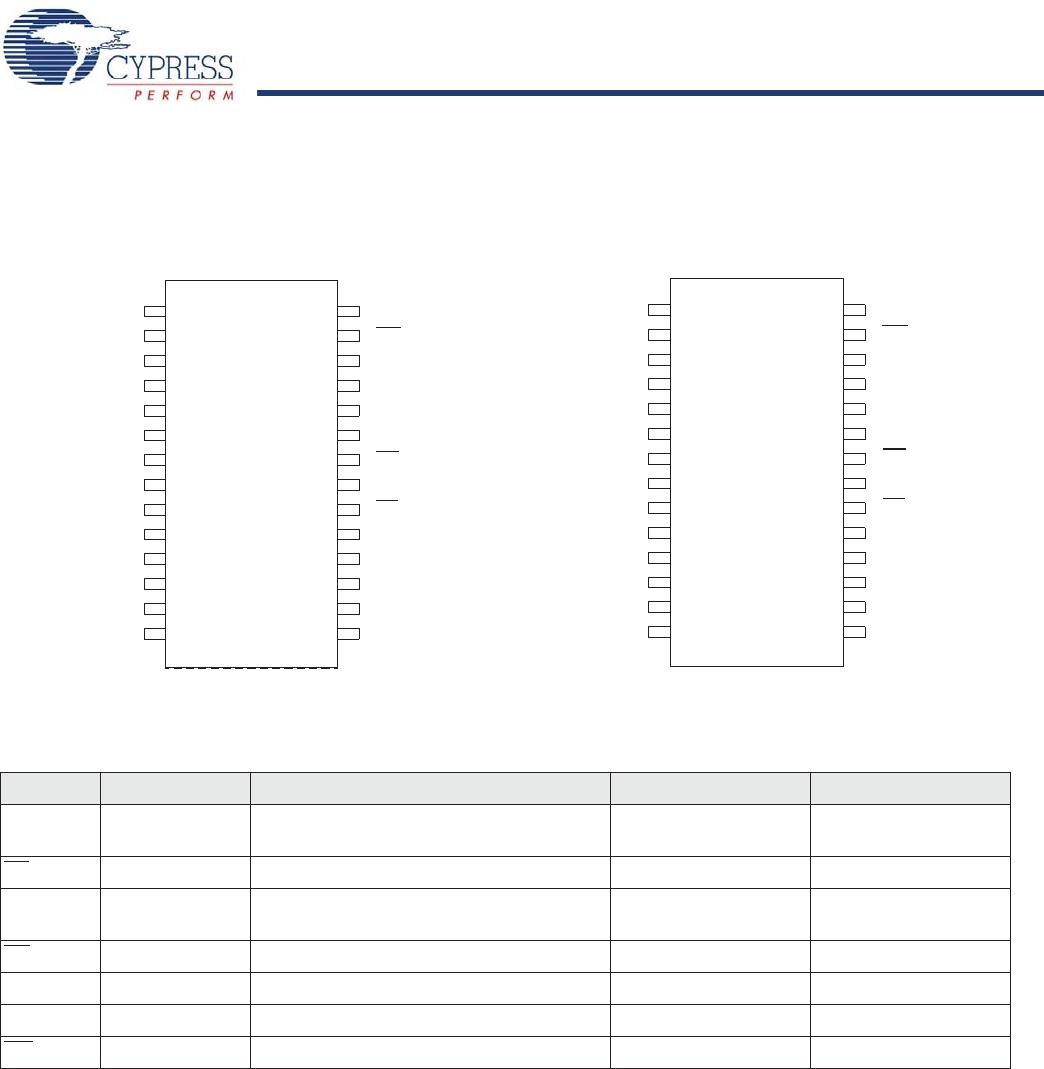

Pin Description .................................................................3

Truth Table ........................................................................4

Maximum Ratings .............................................................5

Operating Range ...............................................................5

DC Electrical Characteristics ..........................................5

Capacitance ......................................................................6

Thermal Resistance ..........................................................6

AC Test Loads ..................................................................6

AC Test Conditions ..........................................................6

Data Retention Characteristics .......................................7

Data Retention Waveform ................................................7

AC Electrical Characteristics ..........................................8

Ordering Information ......................................................12

Ordering Code Definitions ......................................... 12

Package Diagrams ..........................................................13

Acronyms ........................................................................15

Document Conventions .................................................15

Units of Measure ....................................................... 15

Document History Page .................................................16

Sales, Solutions, and Legal Information ......................17

Worldwide Sales and Design Support ....................... 17

Products .................................................................... 17

PSoC® Solutions ...................................................... 17

Cypress Developer Community ................................. 17

Technical Support ..................................................... 17