AD8346

Rev. A | Page 10 of 20

CIRCUIT DESCRIPTION

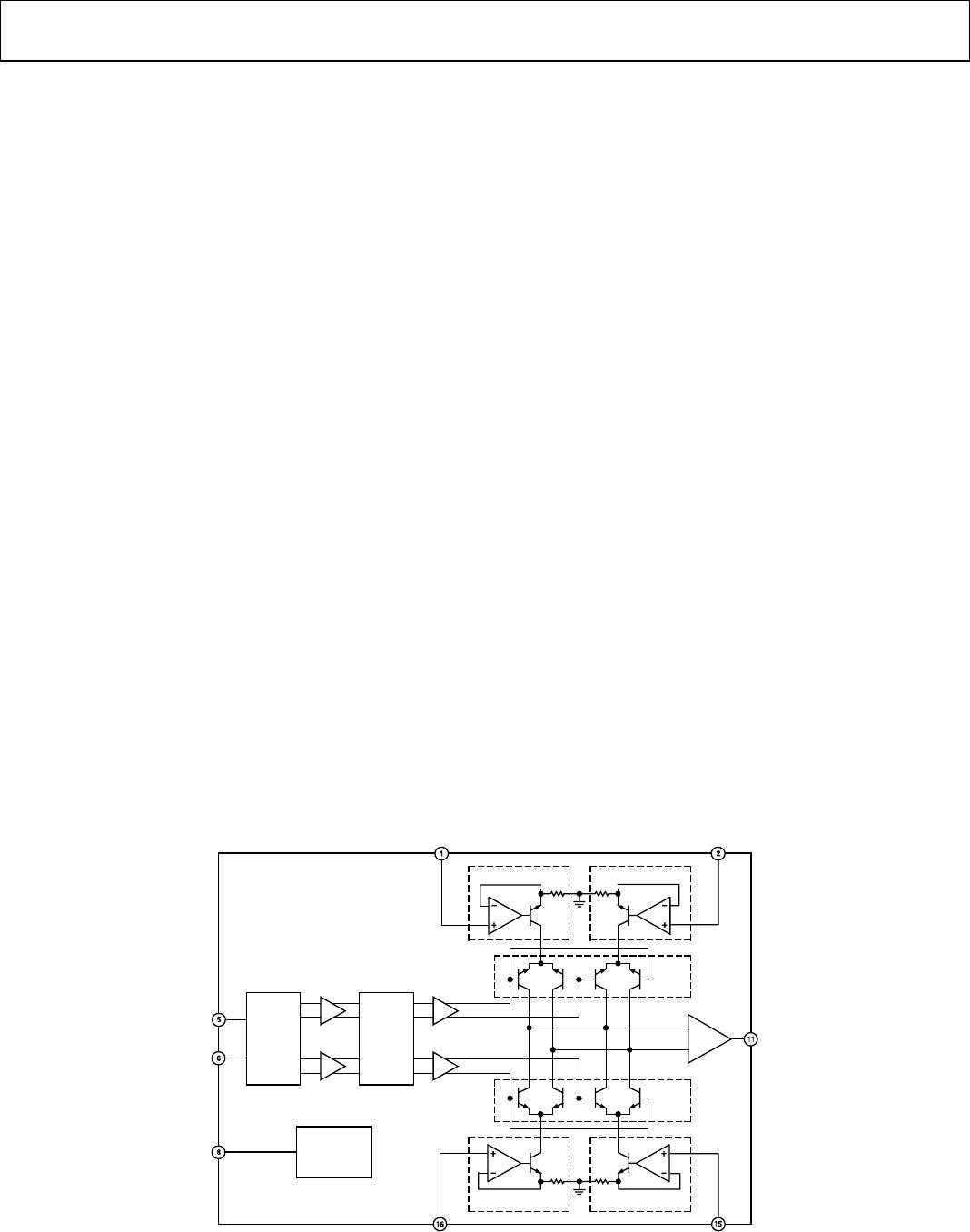

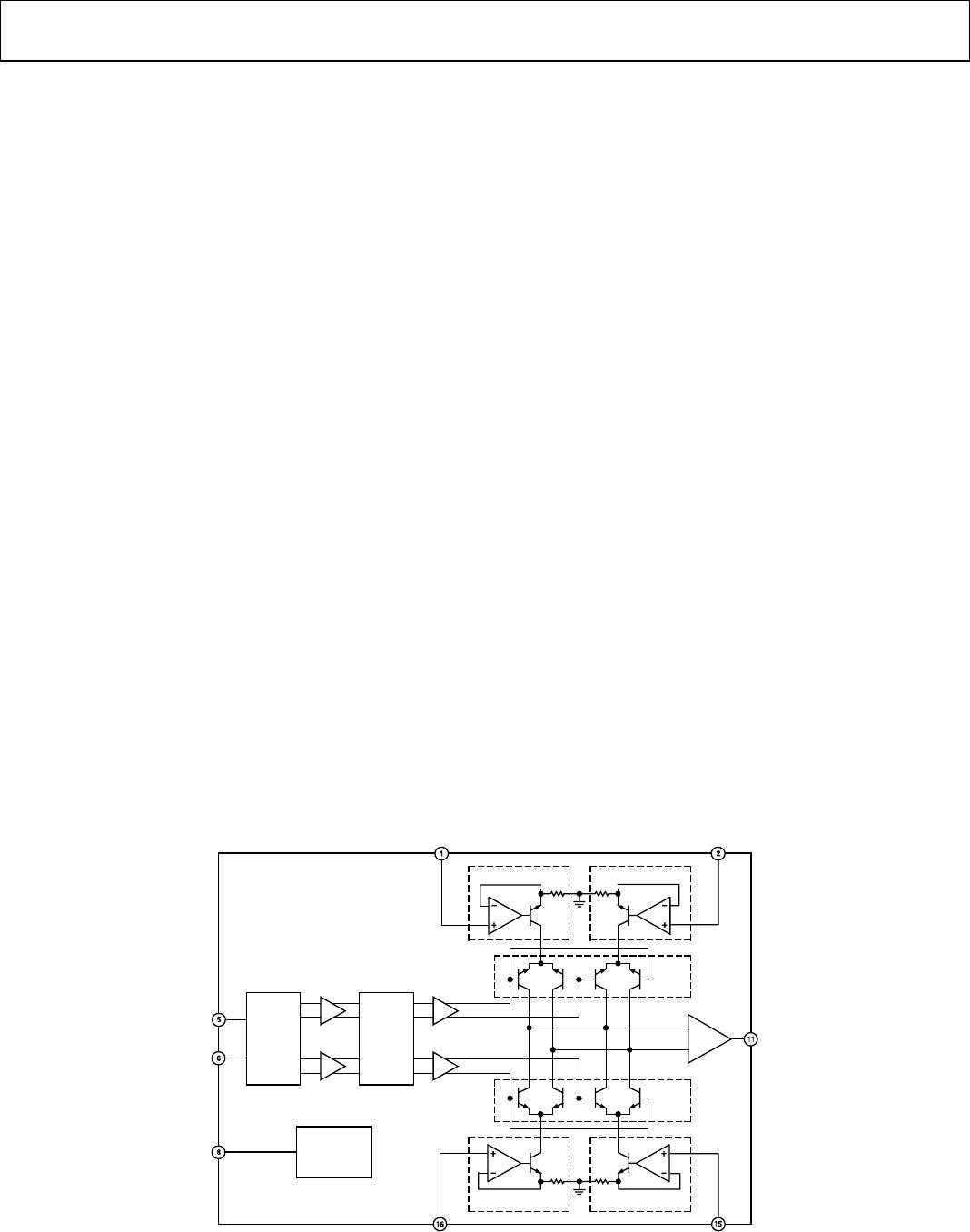

OVERVIEW

The AD8346 can be divided into the following sections: local

oscillator (LO) interface, mixer, voltage-to-current (V-to-I)

converter, differential-to-single-ended (D-to-S) converter, and

bias. A detailed block diagram of the part is shown in

Figure 25.

The LO interface generates two LO signals, with 90° of phase

difference between them, to drive two mixers in quadrature.

Baseband voltage signals are converted into current form in

the V-to-I converters, feeding into two mixers. The output of

the mixers are combined to feed the D-to-S converter which

provides the 50 Ω output interface. Bias currents to each

section are controlled by the Enable (ENBL) signal. Detailed

descriptions of each section follows.

LO INTERFACE

The differential LO inputs allow the user to drive the LO differ-

entially in order to achieve maximum performance. The LO can

be driven single-endedly but the LO feedthrough performance

is degraded, especially towards the higher end of the frequency

range. The LO interface consists of interleaved stages of

polyphase network phase splitters and buffer amplifiers. The

phase-splitter contains resistors and capacitors connected in a

circular manner to split the LO signal into I and Q paths in

precise quadrature with each other. The signal on each path

goes through a buffer amplifier to make up for the loss and high

frequency roll-off. The two signals then go through another

polyphase network to enhance the quadrature accuracy. The

broad operating frequency range of 0.8 GHz to 2.5 GHz is

achieved by staggering the RC time constants in each stage of

the phase-splitters. The outputs of the second phase-splitter are

fed into the driver amplifiers for the mixers’ LO inputs.

V-TO-I CONVERTER

Each baseband input pin is connected to an op amp driving an

emitter follower. Feedback at the emitter maintains a current

proportional to the input voltage through the transistor. This

current is fed to the two mixers in differential form.

MIXERS

There are two double-balanced mixers, one for the in-phase

channel (I-channel) and one for the quadrature channel

(Q channel). Each mixer uses the gilbert cell design with four

cross-connected transistors. The bases of the transistors are

driven by the LO signal of the corresponding channel. The

output currents from the two mixers are summed together in

two resistors in series with two coupled on-chip inductors. The

signal developed across the R-L loads is sent to the D-to-S stage.

DIFFERENTIAL-TO-SINGLE-ENDED CONVERTER

The differential-to-single-ended converter consists of two

emitter followers driving a totem-pole output stage. Output

impedance is established by the emitter resistors in the output

transistors. The output of this stage is connected to the output

(VOUT) pin.

BIAS

A band gap reference circuit based on the Δ-V

BE

principle

generates the proportional-to-absolute-temperature (PTAT)

currents used by the different sections as references. The band

gap voltage is also used to generate a temperature-stable current

in the V-to-I converters to produce a temperature-independent

slew rate. When the band gap reference is disabled by pulling

down the ENBL pin, all other sections are shut off accordingly.

MIXER

MIXER

V-TO-I

V-TO-I

V-TO-I

V-TO-I

D-TO-S

BIAS CELL

AD8346

LOIN

LOIP

ENBL

QBBP

QBBN

V

OU

IBBNIBBP

PHASE

SPLITTER

1

PHASE

SPLITTER

2

05335-025

Figure 25. Detailed Block Diagram