AD8346

Rev. A | Page 12 of 20

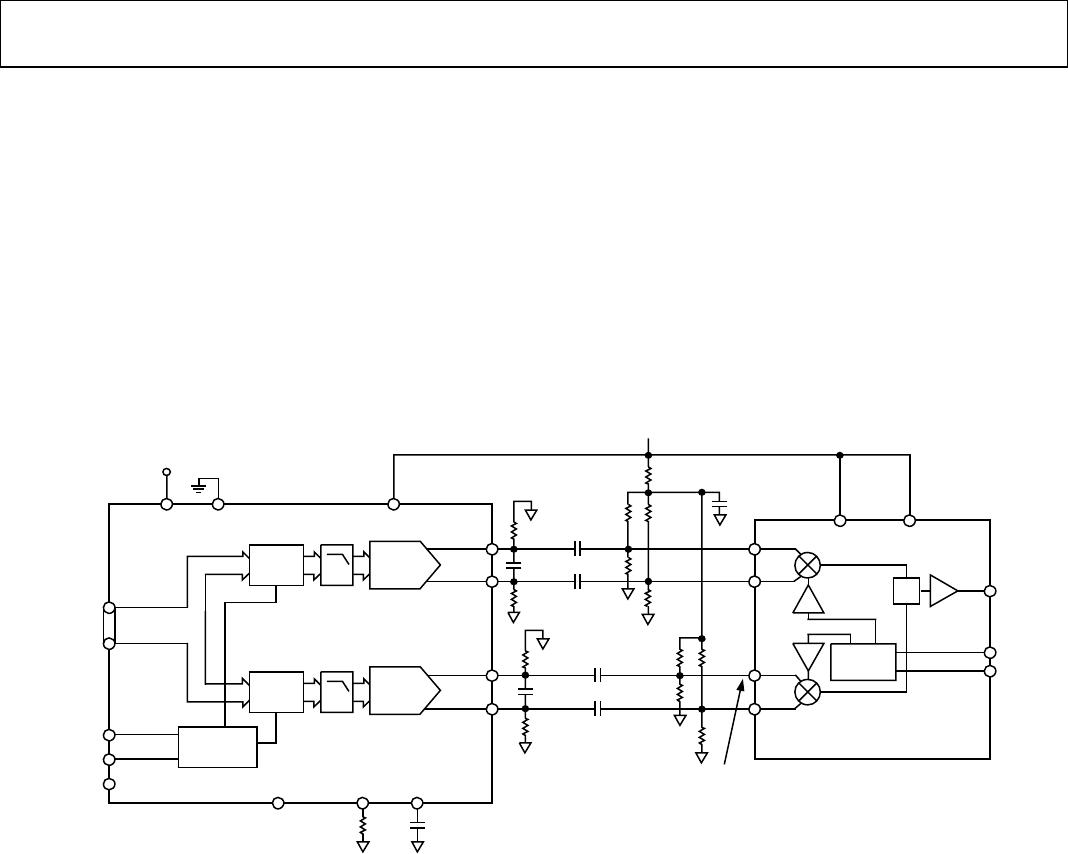

INTERFACE TO AD9761 TXDAC®

Figure 28 shows a dc-coupled current output DAC interface.

The use of dual-integrated DACs, such as the AD9761 with

specified ±0.02 dB and ±0.004 dB gain and offset matching

characteristics, ensures minimum error contribution (over

temperature) from this portion of the signal chain. The use of a

precision thin-film resistor network sets the bias levels precisely

to prevent the introduction of offset errors, which increase LO

feedthrough. For instance, selecting resistor networks with a

0.1% ratio matching characteristics maintains 0.03 dB gain and

offset matching performance.

Using resistive division, the dc bias level at the I and Q inputs

to the AD8346 is set to approximately 1.2 V. Each of the four

current outputs of the DAC delivers a full-scale current of

10 mA, giving a voltage swing of 0 V to 1 V (at the DAC

output). This results in a 0.5 V p-p swing at the I and Q inputs

of the AD8346 (resulting in a 1 V p-p differential swing).

Note that the ratio matching characteristics of the resistive

network, as opposed to its absolute accuracy, is critical in

preserving the gain and offset balance between the I and Q

signal path.

By applying small dc offsets to the I and Q signals from the

DAC, the LO suppression can be reduced from its nominal

value of −42 dBm to as low as −60 dBm while holding to

approximately −50 dBm over temperature (see

Figure 12 for

a plot of LO feedthrough over temperature for an offset

compensated circuit).

I

DAC

2

×

LATCH

I

IOUTB

IOUTA

Q

DAC

2

×

LATCH

Q

QOUTB

QOUTA

MUX

CONTROL

SELECT

WRITE

CLOCK

AD9761

DVDD DCOM AVDD

0.1

μ

F

R

SET

2k

Ω

SLEEP FS ADJ REFIO

DAC

DATA

INPUTS

C

FILTER

100

Ω

100

Ω

C

FILTER

100

Ω

100

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

500

Ω

0.1

μ

F

634

Ω

5V

PHASE

SPLITTER

Σ

VOUT

IBBP

IBBN

QBBP

QBBN

AD8346

LOIP

LOIN

VPS1 VPS2

0.5V p-p EACH PIN

WITH V

CM

= 1.2V

+5V

05335-028

Figure 28. AD8346 Interface to AD9761 TxDAC