CAT1021, CAT1022, CAT1023

www.onsemi.com

6

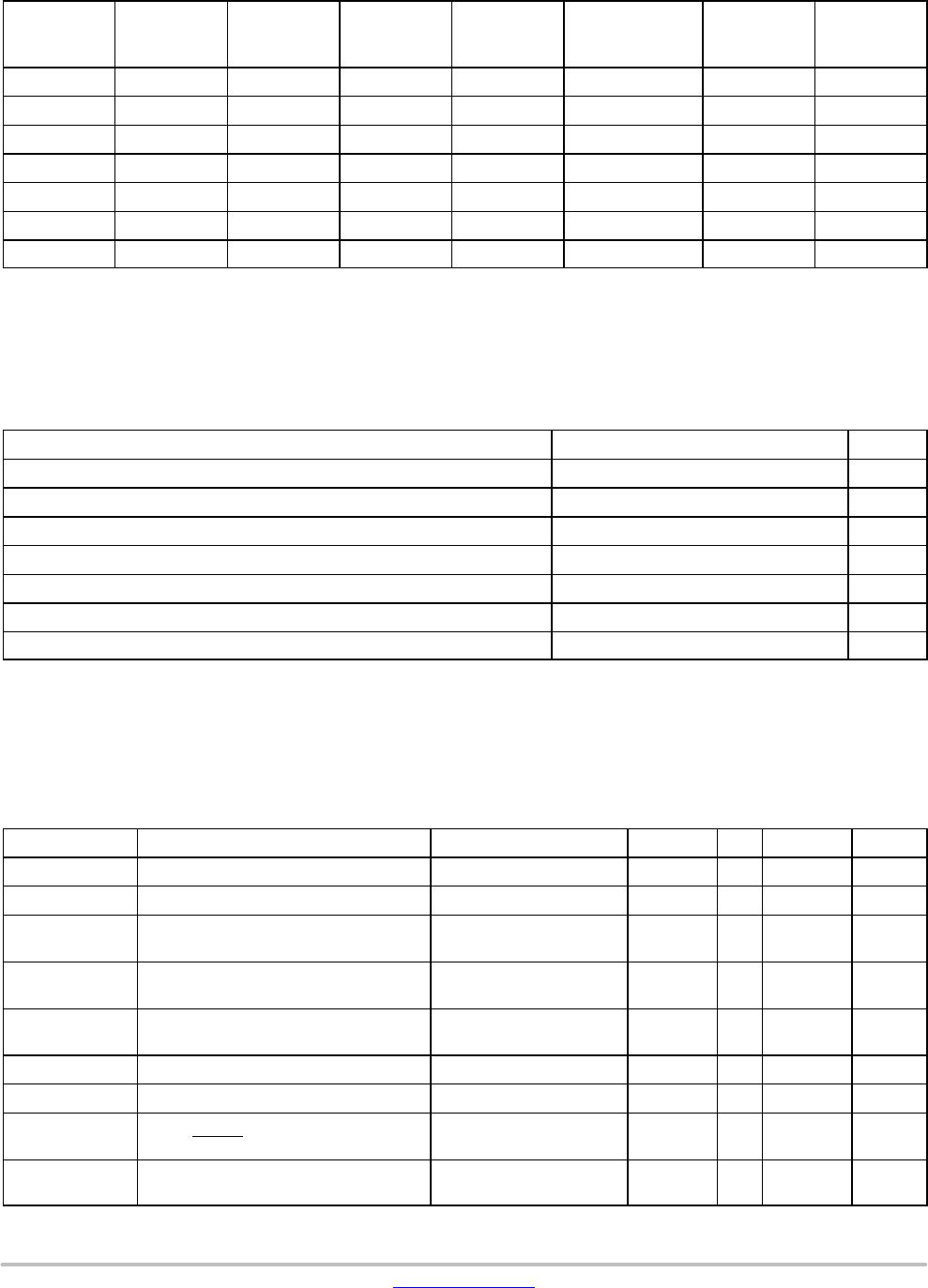

Table 9. RESET CIRCUIT AC CHARACTERISTICS

Symbol Parameter Test Conditions Min Typ Max Units

t

PURST

Power−Up Reset Timeout Note 2 130 200 270 ms

t

RDP

V

TH

to RESET output Delay Note 3 5

ms

t

GLITCH

V

CC

Glitch Reject Pulse Width Notes 4 and 5 30 ns

MR Glitch Manual Reset Glitch Immunity Note 1 100 ns

t

MRW

MR Pulse Width Note 1 5

ms

t

MRD

MR Input to RESET Output Delay Note 1 1

ms

t

WD

Watchdog Timeout Note 1 1.0 1.6 2.1 sec

Table 10. POWER−UP TIMING (Notes 5 and 6)

Symbol Parameter Test Conditions Min Typ Max Units

t

PUR

Power−Up to Read Operation 270 ms

t

PUW

Power−Up to Write Operation 270 ms

Table 11. AC TEST CONDITIONS

Parameter Test Conditions

Input Pulse Voltages 0.2 x V

CC

to 0.8 x V

CC

Input Rise and Fall Times 10 ns

Input Reference Voltages 0.3 x V

CC

, 0.7 x V

CC

Output Reference Voltages 0.5 x V

CC

Output Load Current Source: I

OL

= 3 mA; C

L

= 100 pF

Table 12. RELIABILITY CHARACTERISTICS

Symbol Parameter Reference Test Method Min Max Units

N

END

(Note 5) Endurance MIL−STD−883, Test Method 1033 1,000,000 Cycles/Byte

T

DR

(Note 5) Data Retention MIL−STD−883, Test Method 1008 100 Years

V

ZAP

(Note 5) ESD Susceptibility MIL−STD−883, Test Method 3015 2000 Volts

I

LTH

(Notes 5 & 7) Latch−Up JEDEC Standard 17 100 mA

1. Test Conditions according to “AC Test Conditions” table.

2. Power−up, Input Reference Voltage V

CC

= V

TH

, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

3. Power−Down, Input Reference Voltage V

CC

= V

TH

, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

4. V

CC

Glitch Reference Voltage = V

THmin

; Based on characterization data

5. This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

6. t

PUR

and t

PUW

are the delays required from the time V

CC

is stable until the specified memory operation can be initiated.

7. Latch−up protection is provided for stresses up to 100 mA on input and output pins from −1 V to V

CC

+ 1 V.