PROGRAMMABLE CLOCK GENERATOR 24 MARCH 3, 2017

5P49V5901 DATASHEET

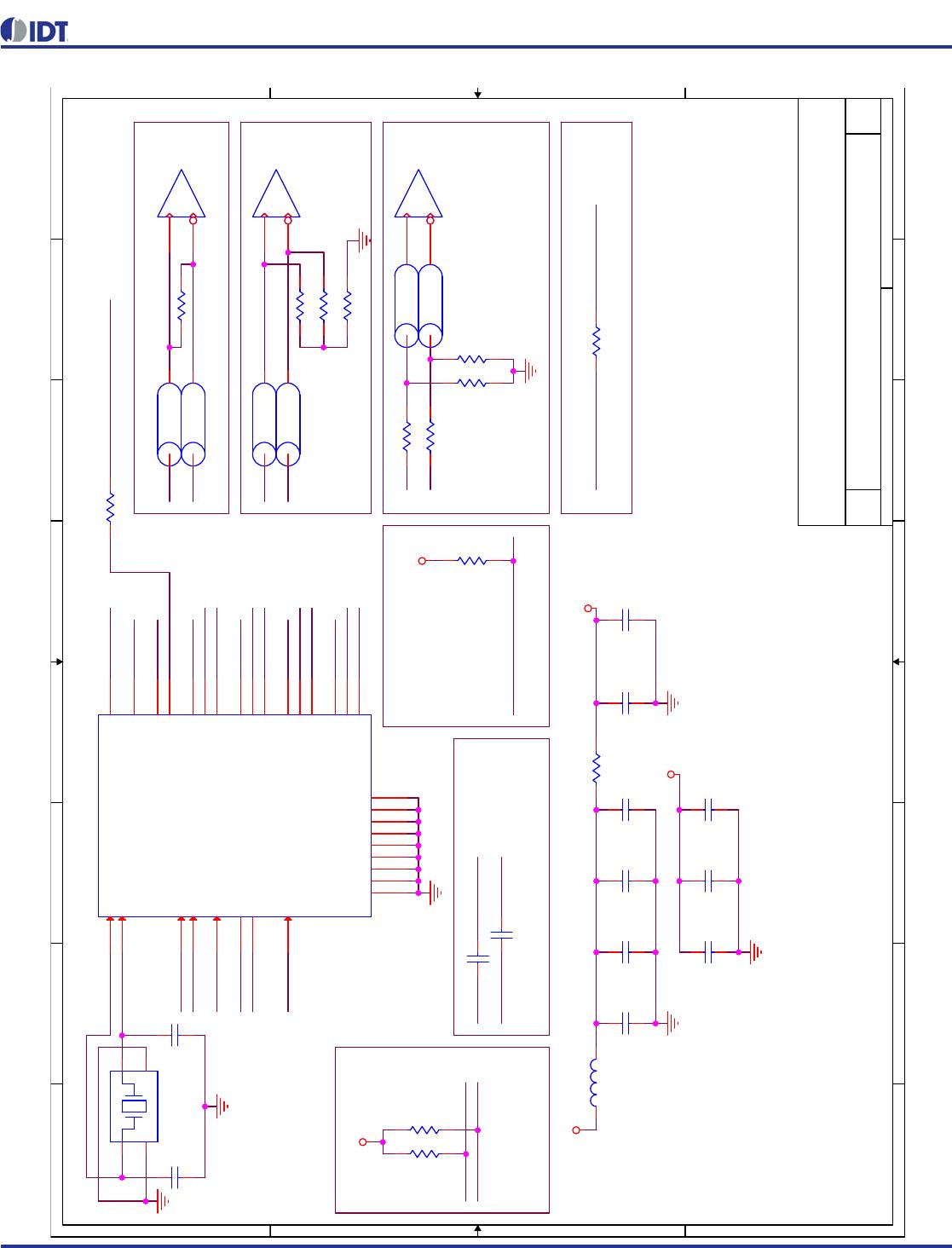

Overdriving the XIN/REF Interface

LVCMOS Driver

The XIN/REF input can be overdriven by an LVCMOS driver

or by one side of a differential driver through an AC coupling

capacitor. The XOUT pin can be left floating. The amplitude of

the input signal should be between 500mV and 1.2V and the

slew rate should not be less than 0.2V/ns. Figure General

Diagram for LVCMOS Driver to XTAL Input Interface shows an

example of the interface diagram for a LVCMOS driver.

This configuration has three properties; the total output

impedance of Ro and Rs matches the 50 ohm transmission

line impedance, the Vrx voltage is generated at the CLKIN

inputs which maintains the LVCMOS driver voltage level

across the transmission line for best S/N and the R1-R2

voltage divider values ensure that the clock level at XIN is less

than the maximum value of 1.2V.

General Diagram for LVCMOS Driver to XTAL Input Interface

Table 25 Nominal Voltage Divider Values vs LVCMOS VDD for

XIN

shows resistor values that ensure the maximum drive

level for the XIN/REF port is not exceeded for all combinations

of 5% tolerance on the driver VDD, the VersaClock VDDA and

5% resistor tolerances. The values of the resistors can be

adjusted to reduce the loading for slower and weaker

LVCMOS driver by increasing the voltage divider attenuation

as long as the minimum drive level is maintained over all

tolerances. To assist this assessment, the total load on the

driver is included in the table.

Table 25: Nominal Voltage Divider Values vs LVCMOS VDD for XIN

XOUT

XIN / REF

R1

R2

C3

0. 1 uF

V_XIN

LV CMOS

VDD

Ro

Ro + Rs = 50 ohms

Rs Zo = 50 Ohm

LVCMOS Driver VDD Ro+Rs R1 R2 V_XIN (peak) Ro+Rs+R1+R2

3.3 50.0 130 75 0.97 255

2.5 50.0 100 100 1.00 250

1.8 50.0 62 130 0.97 242