Data Sheet AD9665

Rev. F | Page 9 of 16

APPLICATIONS INFORMATION

The AD9665 uses the current at one or more of its four inputs,

RSET, W1SET, W2SET, and W3SET, and generates an output

current proportional to the sum of the input currents. The read

channel has a typical gain of 105 mA/mA, Write Channel 1 has

a typical gain of 300 mA/mA, Write Channel 2 has a typical

gain of 200 mA/mA, and Write Channel 3 has a typical gain of

100 mA/mA. The input impedance of all the channels is

typically 200 Ω. In most cases, a voltage output DAC can be

used to drive these channels. In this case, a series resistance

should be placed between each of the DAC channels and the

respective input on the AD9665. These resistances should be

selected to scale the desired maximum output current for each

channel with an appropriate voltage from the DAC without

excessively loading it.

BOARD LAYOUT

Due to the fast rise and fall time (<1 ns) required for the

operation of high speed drives, trace lengths carrying high

speed signals, such as

RDIS

, W1DIS, W2DIS, and W3DIS, and

the output current should be kept as short as possible to

minimize series inductance. A decoupling capacitor should be

located near each V

DD

pin, and the ground return for the

cathode of the laser diode should be kept as short as possible.

An S11 measurement of a piece of flexible printed circuit board

(FPC) can show the inductance associated with that section of

the FPC. In Table 4, an S11 measurement of two different pieces

of a 19 mm (0.75 in) FPC was taken. The first piece is a single

layer of an FPC with 0.5 ounce copper and 25.4 micron (1 mil)

thick Kapton

® and coverlay. The second piece is an FPC with

2 layers of 0.5 ounce copper and 25.4 micron (1 mil) thick

Kapton and coverlay.

Table 4. Inductance of FPC

S11 L, nH @ 10 MHz L, nH @ 300 MHz

Single-layer FPC 8.8 8.5

Double-layer FPC 4.3 4.2

As indicated by the measurement results, using two layers of

copper in an FPC can reduce inductance by over 50%. Using the

basic circuit equation

d

di

LV

it can be seen that increasing the amplitude of a current step

increases the voltage drop across the inductor. For example, on

the single-layer FPC, a 200 mA pulse with a rise time of 1 ns

generates a voltage drop of 1.86 V, assuming an additional

0.5 nH of inductance due to the laser diode itself. Increase this

current to 250 mA, and the voltage drop is greater than 2.3 V.

Add this to the ~2 V of operating voltage that is required for the

laser diode, and voltage headroom can become a problem if

operating on a 5 V supply. Because the di/dt term seems to be a

system requirement, L is the only contributor that can be

changed when trying to reduce the voltage drop. Decreasing the

inductance of the FPC can be done by either making the trace

wider or by making it shorter. Because the distance from the

laser diode driver (LDD) to the laser diode is fixed, using a

wider trace is the only option. This can be accomplished by

changing from a single-layer FPC design to a double-layer FPC

design. This additional layer allows the full width of the FPC

from the LDD to the laser diode to be used for the drive

current, while the bottom layer can be used entirely for the

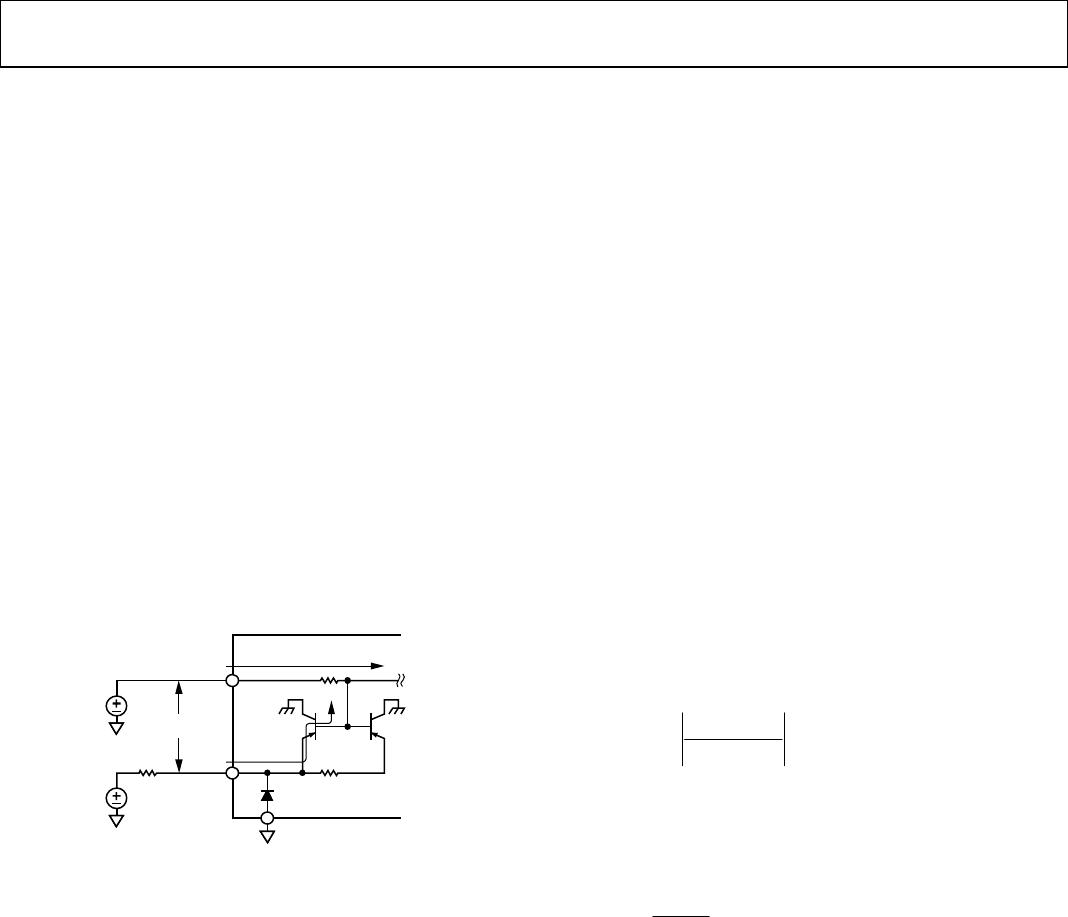

return path (see Figure 15).

LASER

DIODE

TOP

TRACE

BOTTOM

TRACE

SINGLE-LAYER

FPC

I

DIODE

I

D

I

O

DE

DOUBLE-LAYER

FPC

I

DIOD

E

I

DIODE

VIA

05269-016

Figure 15. Single-Layer and Double-Layer Flexible Printed Circuit Boards

TEMPERATURE CONSIDERATIONS

The AD9665 is available in a 32-lead LFCSP with an exposed

heat pad on top of the package. Using a 4-layer JEDEC standard

test board, the θ

JA

of this package was determined without any

external heat sink attached to the exposed pad. This board is

made of FR4, is 1.60 mm thick, and consists of four copper

layers. The two internal layers are solid copper (1 oz/in

2

or

0.35 mm thick). The two surface layers (containing the

component and back side traces) use 2 oz/in

2

(0.70 mm thick)

of copper. This method of construction yields a θ

JA

for the

AD9665 of approximately 110°C/W. An integrated circuit

dissipating 500 mW and packaged in an LFCSP, while operating

in an ambient environment of 85°C, would have an internal

junction temperature of approximately 140°C.

85°C + 0.5 W × 110°C/W = 140°C

This junction temperature is within the maximum

recommended operating junction temperature of 150°C. This

can be improved by attaching an external heat sink to the exposed

heat pad of the package. Of course, this is not a realistic method for

mounting a laser diode driver in an optical storage device.

In an actual application, the laser diode driver would most

likely be mounted to a flexible circuit board. The θ

JA

of a system