CAT24C256

www.onsemi.com

6

Power-On Reset (POR)

The CAT24C256 Die Rev. C incorporates Power−On

Reset (POR) circuitry which protects the internal logic

against powering up in the wrong state.

The device will power up into Standby mode after V

CC

exceeds the POR trigger level and will power down into

Reset mode when V

CC

drops below the POR trigger level.

This bi−directional POR behavior protects the device

against brown−out failure, following a temporary loss of

power.

Pin Description

SCL: The Serial Clock input pin accepts the Serial Clock

signal generated by the Master.

SDA: The Serial Data I/O pin receives input data and

transmits data stored in EEPROM. In transmit mode, this pin

is open drain. Data is acquired on the positive edge, and is

delivered on the negative edge of SCL.

A

0

, A

1

and A

2

: The Address pins accept the device address.

These pins have on−chip pull−down resistors.

WP: The Write Protect input pin inhibits all write

operations, when pulled HIGH. This pin has an on−chip

pull−down resistor.

Functional Description

The CAT24C256 supports the Inter−Integrated Circuit

(I

2

C) Bus data transmission protocol, which defines a device

that sends data to the bus as a transmitter and a device

receiving data as a receiver. Data flow is controlled by a

Master device, which generates the serial clock and all

START and STOP conditions. The CAT24C256 acts as a

Slave device. Master and Slave alternate as either

transmitter or receiver. Up to 8 devices may be connected to

the bus as determined by the device address inputs A

0

, A

1

,

and A

2

.

I

2

C Bus Protocol

The I

2

C bus consists of two ‘wires’, SCL and SDA. The

two wires are connected to the V

CC

supply via pull−up

resistors. Master and Slave devices connect to the 2−wire

bus via their respective SCL and SDA pins. The transmitting

device pulls down the SDA line to ‘transmit’ a ‘0’ and

releases it to ‘transmit’ a ‘1’.

Data transfer may be initiated only when the bus is not

busy (see A.C. Characteristics).

During data transfer, the SDA line must remain stable

while the SCL line is HIGH. An SDA transition while SCL

is HIGH will be interpreted as a START or STOP condition

(Figure 2).

START

The START condition precedes all commands. It consists

of a HIGH to LOW transition on SDA while SCL is HIGH.

The START acts as a ‘wake−up’ call to all receivers. Absent

a START, a Slave will not respond to commands.

STOP

The STOP condition completes all commands. It consists

of a LOW to HIGH transition on SDA while SCL is HIGH.

The STOP starts the internal Write cycle (when following a

Write command) or sends the Slave into standby mode

(when following a Read command).

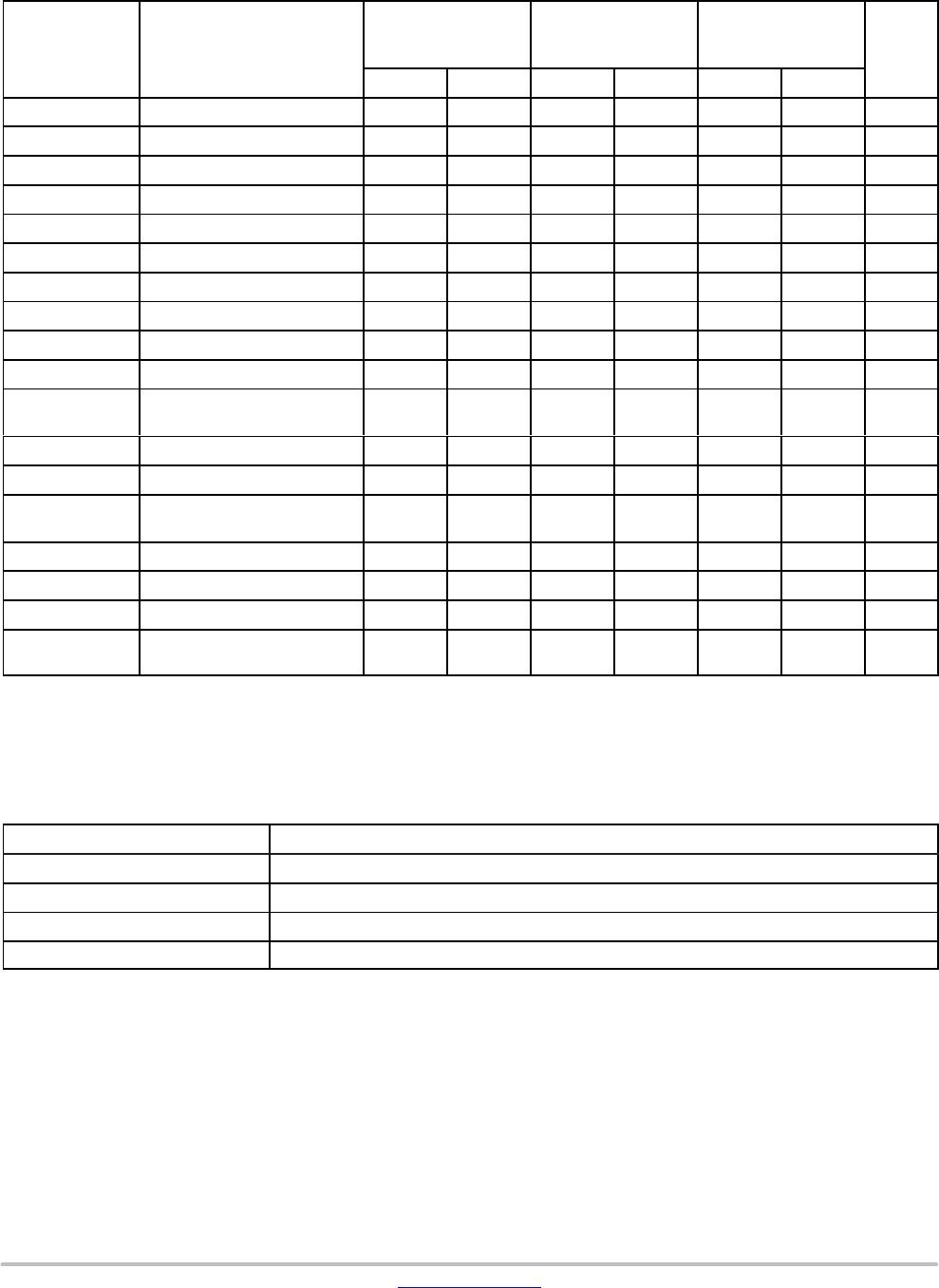

Device Addressing

The Master initiates data transfer by creating a START

condition on the bus. The Master then broadcasts an 8−bit

serial Slave address. The first 4 bits of the Slave address are

set to 1010, for normal Read/Write operations (Figure 3).

The next 3 bits, A

2

, A

1

and A

0

, select one of 8 possible Slave

devices. The last bit, R/W, specifies whether a Read (1) or

Write (0) operation is to be performed.

Acknowledge

After processing the Slave address, the Slave responds

with an acknowledge (ACK) by pulling down the SDA line

during the 9th clock cycle (Figure 4). The Slave will also

acknowledge the byte address and every data byte presented

in Write mode. In Read mode the Slave shifts out a data byte,

and then releases the SDA line during the 9th clock cycle. If

the Master acknowledges the data, then the Slave continues

transmitting. The Master terminates the session by not

acknowledging the last data byte (NoACK) and by sending

a STOP to the Slave. Bus timing is illustrated in Figure 5.