IN

Trilevel input to select High BW, Bypass or Low BW mode. This pin is biased to VDD/2 (Bypass

mode) with internal pull up/pull down resistors. See PLL Operating Mode Table for Details.

3 FB_DNC DNC

True clock of differential feedback. The feedback output and feedback input are connected

internally on this pin. Do not connect anything to this pin.

4 FB_DNC# DNC

Complement clock of differential feedback. The feedback output and feedback input are

connected internally on this pin. Do not connect anything to this pin.

5 VDDR3.3 PWR

3.3V power for differential input clock (receiver). This VDD should be treated as an Analog

power rail and filtered appropriately.

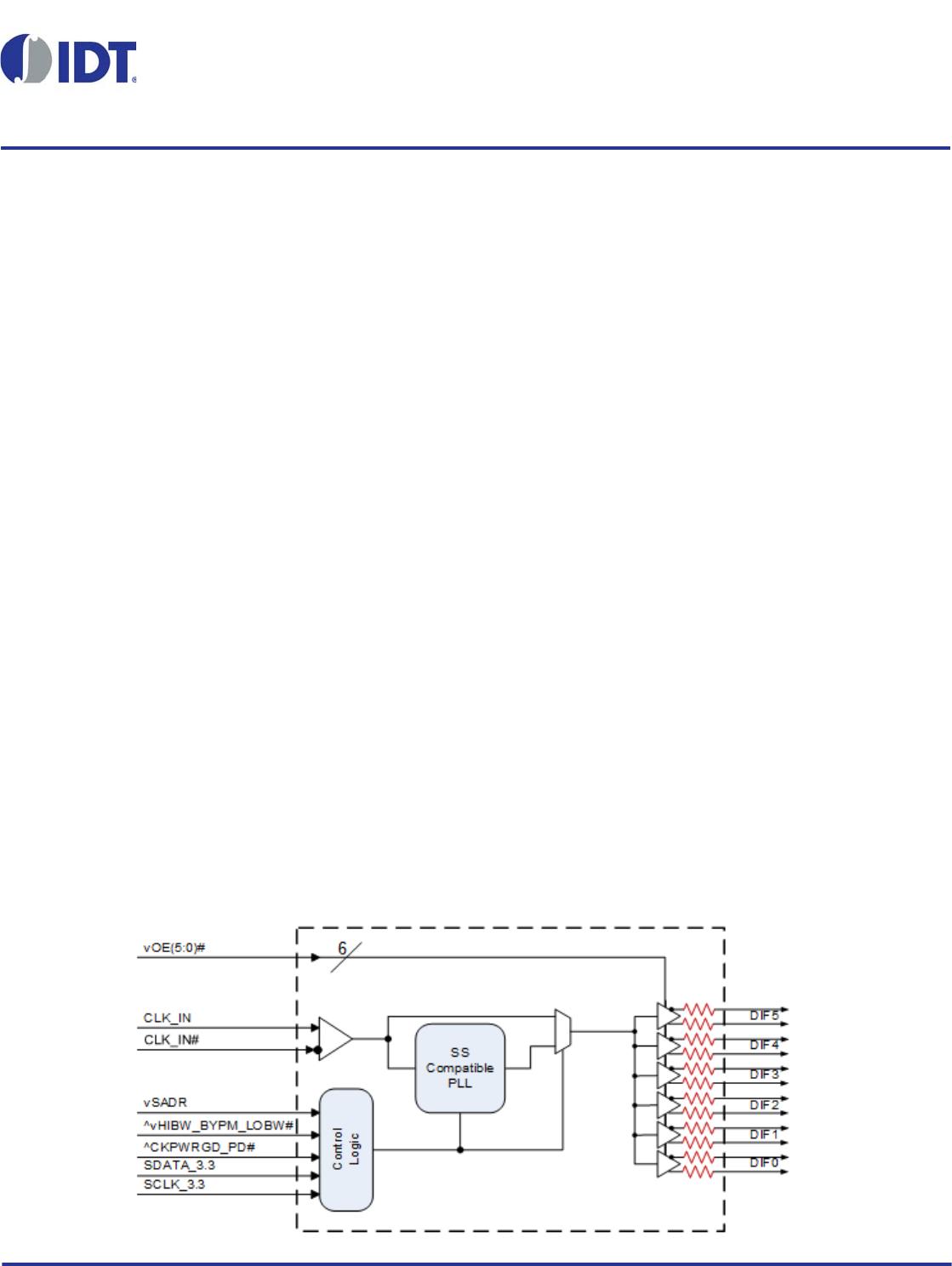

6 CLK_IN IN True Input for differential reference clock.

7 CLK_IN# IN Complementary Input for differential reference clock.

8 GNDDIG GND Ground pin for digital circuitry

9 SCLK_3.3 IN Clock pin of SMBus circuitry, 3.3V tolerant.

10 SDATA_3.3 I/O Data pin for SMBus circuitry, 3.3V tolerant.

11 VDDDIG3.3 PWR 3.3V digital power (dirty power)

12 VDDIO PWR Power supply for differential outputs

13 vOE0# IN

Active low input for enabling DIF pair 0. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

14 DIF0 OUT Differential true clock output

15 DIF0# OUT Differential Complementary clock output

16 VDD3.3 PWR Power supply, nominal 3.3V

17 VDDIO PWR Power supply for differential outputs

18 DIF1 OUT Differential true clock output

19 DIF1# OUT Differential Complementary clock output

20 NC N/A No Connection.

21 vOE1# IN

Active low input for enabling DIF pair 1. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

22 DIF2 OUT Differential true clock output

23 DIF2# OUT Differential Complementary clock output

24 vOE2# IN

Active low input for enabling DIF pair 2. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

25 VDDA3.3 PWR 3.3V power for the PLL core.

26 VDDIO PWR Power supply for differential outputs

27 DIF3 OUT Differential true clock output

28 DIF3# OUT Differential Complementary clock output

29 vOE3# IN

Active low input for enabling DIF pair 3. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

30 NC N/A No Connection.

31 VDD3.3 PWR Power supply, nominal 3.3V

32 VDDIO PWR Power supply for differential outputs

33 DIF4 OUT Differential true clock output

34 DIF4# OUT Differential Complementary clock output

35 vOE4# IN

Active low input for enabling DIF pair 4. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

36 DIF5 OUT Differential true clock output

37 DIF5# OUT Differential Complementary clock output

38 vOE5# IN

Active low input for enabling DIF pair 5. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

39 VDDIO PWR Power supply for differential outputs

40 ^CKPWRGD_PD# IN

Input notifies device to sample latched inputs and start up on first high assertion. Low enters

Power Down Mode, subsequent high assertions exit Power Down Mode. This pin has internal

pull-up resistor.

41 ePAD GND Connect paddle to ground.