Data Sheet ADuM4150

Rev. B | Page 5 of 21

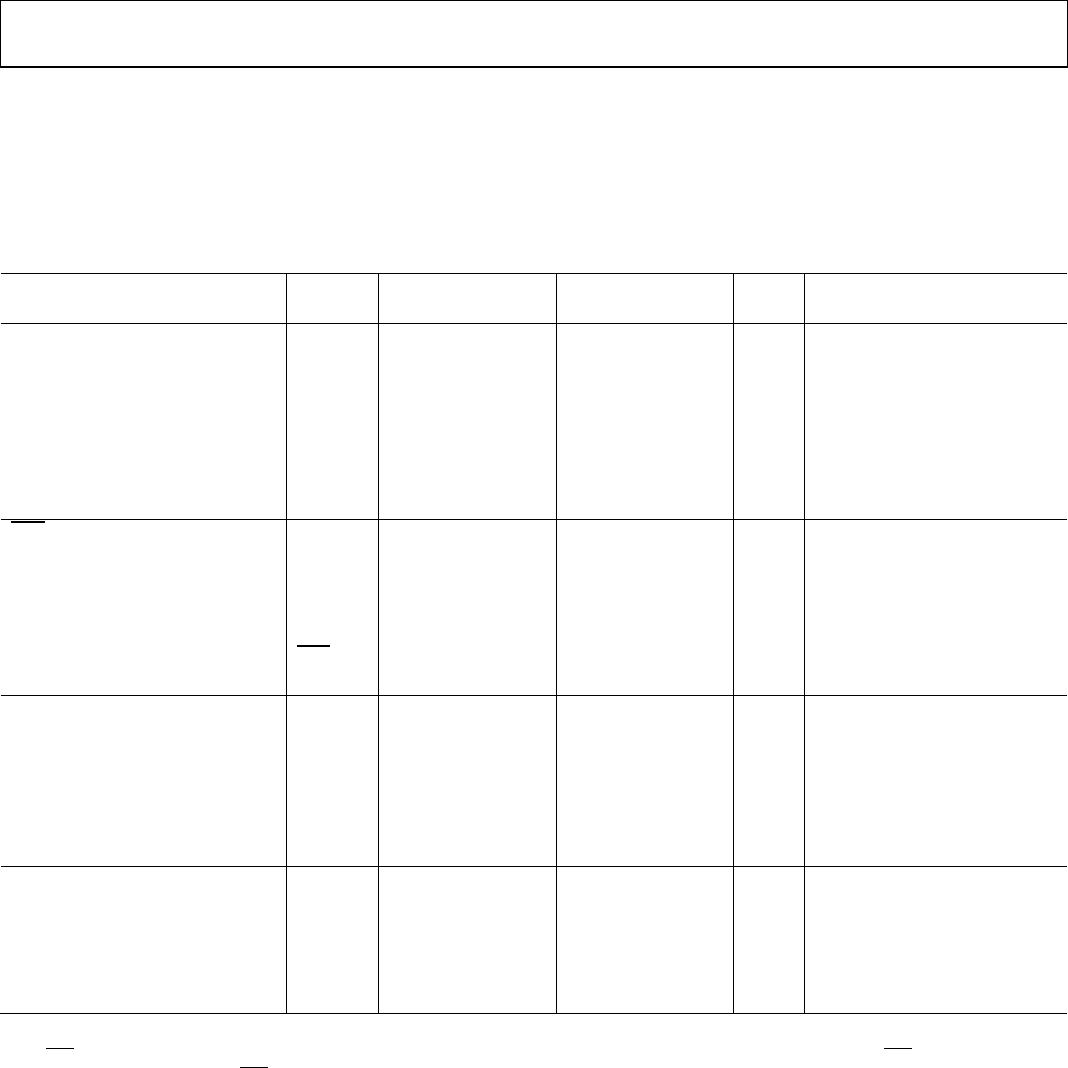

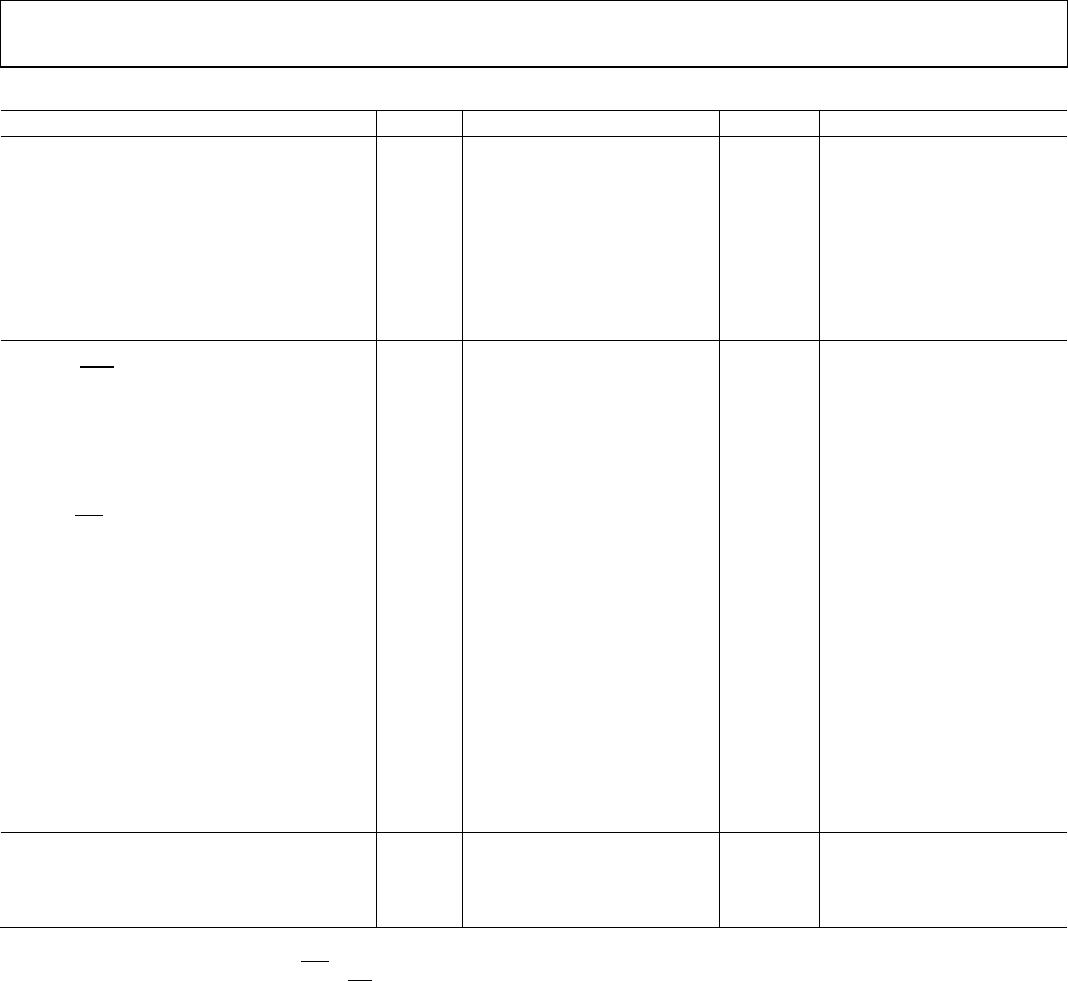

ELECTRICAL CHARACTERISTICS—3.3 V OPERATION

All typical specifications are at T

A

= 25°C and V

DD1

= V

DD2

= 3.3 V. Minimum and maximum specifications apply over the entire recommended

operation range: 3.0 V ≤ V

DD1

≤ 3.6 V, 3.0 V ≤ V

DD2

≤ 3.6 V, and −40°C ≤ T

A

≤ +125°C, unless otherwise noted. Switching specifications

are tested with C

L

= 15 pF and CMOS signal levels, unless otherwise noted.

Table 4. Switching Specifications

Parameter Symbol

A Grade B Grade

Unit Test Conditions/Comments Min Typ Max Min Typ Max

MCLK, MO, SO

SPI Clock Rate SPI

MCLK

8.3 12.5 MHz

Data Rate Fast (MO, SO) DR

FAS T

40 40 Mbps Within PWD limit

Propagation Delay t

PHL

, t

PLH

30 20 ns 50% input to 50% output

Pulse Width PW 12.5 12.5 ns Within PWD limit

Pulse Width Distortion PWD 3 3 ns |t

PLH

− t

PHL

|

Codirectional Channel Matching

1

t

PSKCD

3 3 ns

HS

MSS

Data Rate Fast DR

FAS T

40 40 Mbps Within PWD limit

Propagation Delay t

PHL

, t

PLH

30 30 ns 50% input to 50% output

Pulse Width PW 12.5 12.5 ns Within PWD limit

Pulse Width Distortion PWD 3 3 ns |t

PLH

− t

PHL

|

Setup Time

2

MSS

SETUP

1.5 10 ns

Jitter, High Speed J

HS

1 1 ns

DCLK

3

Data Rate 40 40 MHz

Propagation Delay t

PHL

, t

PLH

60 40 ns t

PMCLK

+ t

PSO

+ 3 ns

Pulse Width Distortion PWD 3 3 ns |t

PLH

− t

PHL

|

Pulse Width PW 12 12 ns Within PWD limit

Clock Delay Error DCLK

ERR

−4 +2.4 +9 −3 +2.5 +8 ns t

PDCLK

− (t

PMCLK

+ t

PSO

)

Jitter J

DCLK

1 1 ns

V

IA

, V

IB

Data Rate Slow DR

SLOW

250 250 kbps Within PWD limit

Propagation Delay t

PHL

, t

PLH

0.1 2.6 0.1 2.6 µs 50% input to 50% output

Pulse Width PW 4 4 µs Within PWD limit

Jitter, Low Speed J

LS

2.5 2.5 µs

V

Ix

4

Minimum Input Skew

5

t

VIx SKEW

10 10 ns

1

Codirectional channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier.

2

The

MSS

signal is glitch filtered in both speed grades, whereas the other fast signals are not glitch filtered in the B grade. To guarantee that

MSS

reaches the output

ahead of another fast signal, set up

MSS

prior to the competing signal by different times depending on speed grade.

3

t

PMCLK

is the propagation delay of the MCLK signal from Side 1 to Side 2. t

PSO

is the propagation delay of the SO signal from Side 2 to Side 1. t

PDCLK

is the difference

between the DCLK signal and the round trip propagation delay.

4

V

Ix

= V

IA

or V

IB

.

5

An internal asynchronous clock, not available to users, samples the low speed signals. If edge sequence in codirectional channels is critical to the end application, the

leading pulse must be at least 1 t

VIx SKEW

time ahead of a later pulse to guarantee the correct order or simultaneous arrival at the output.