Data Sheet AD8145

INPUT CLAMPING

The differential input that is assigned to receive the input signal

includes clamping diodes that limit the differential input swing

to approximately 5.5 V p-p at 25°C. Because of this, the input

and feedback stages should never be interchanged.

The supply current drawn by the AD8145 has a strong dependence

on the input signal magnitude because the input transconductance

stages operate with differential input signals that can be up to a

few volts peak-to-peak. This behavior is distinctly different

from that of traditional op amps, where the differential input

signal is driven to essentially 0 V by negative feedback.

For most applications, including receiving RGB video signals,

the input signal magnitudes encountered are well within the

safe operating limits of the AD8145 over its full power supply

and operating temperature ranges. In some extreme applications

where large differential and/or common-mode voltages are

encountered, external clamping may be necessary. External

common-mode clamping is also sometimes required when an

unpowered AD8145 receives a signal from an active driver. In

this case, external diodes are required when the current drawn

by the internal ESD diodes cannot be kept to less than 5 mA.

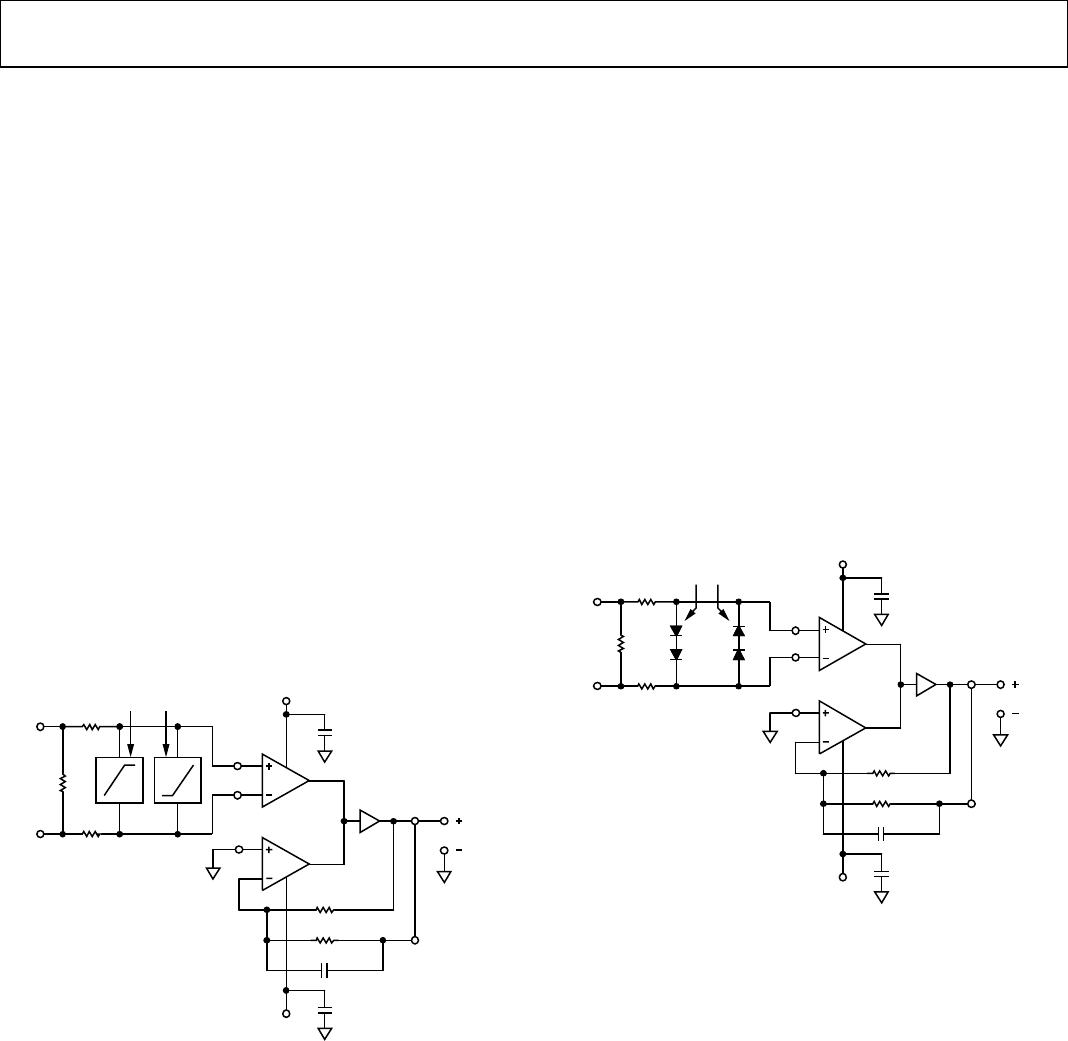

Figure 39 shows a general approach to external differential-mode

clamping.

POSITIVE CLAMP NEGATIVE CLAMP

R

S

R

T

V

IN

R

S

–

+

GAIN

REF

R

R

0.01µF

0.01µF

+5V

–5V

C

OUT

V

OUT

06307-040

Figure 39. Differential-Mode Clamping with G = 1

The positive and negative clamps are nonlinear devices that exhibit

very low impedance when the voltage across them reaches a

critical threshold (clamping voltage), thereby limiting the voltage

across the AD8145 input. The positive clamp has a positive

threshold, and the negative clamp has a negative threshold.

A diode is a simple example of such a clamp. Schottky diodes

generally have lower clamping voltages than typical signal diodes.

The clamping voltage should be larger than the largest expected

signal amplitude, with enough margin to ensure that the received

signal passes without being distorted.

A simple way to implement a clamp is to use a number of diodes in

series. The resultant clamping voltage is then the sum of the

clamping voltages of individual diodes.

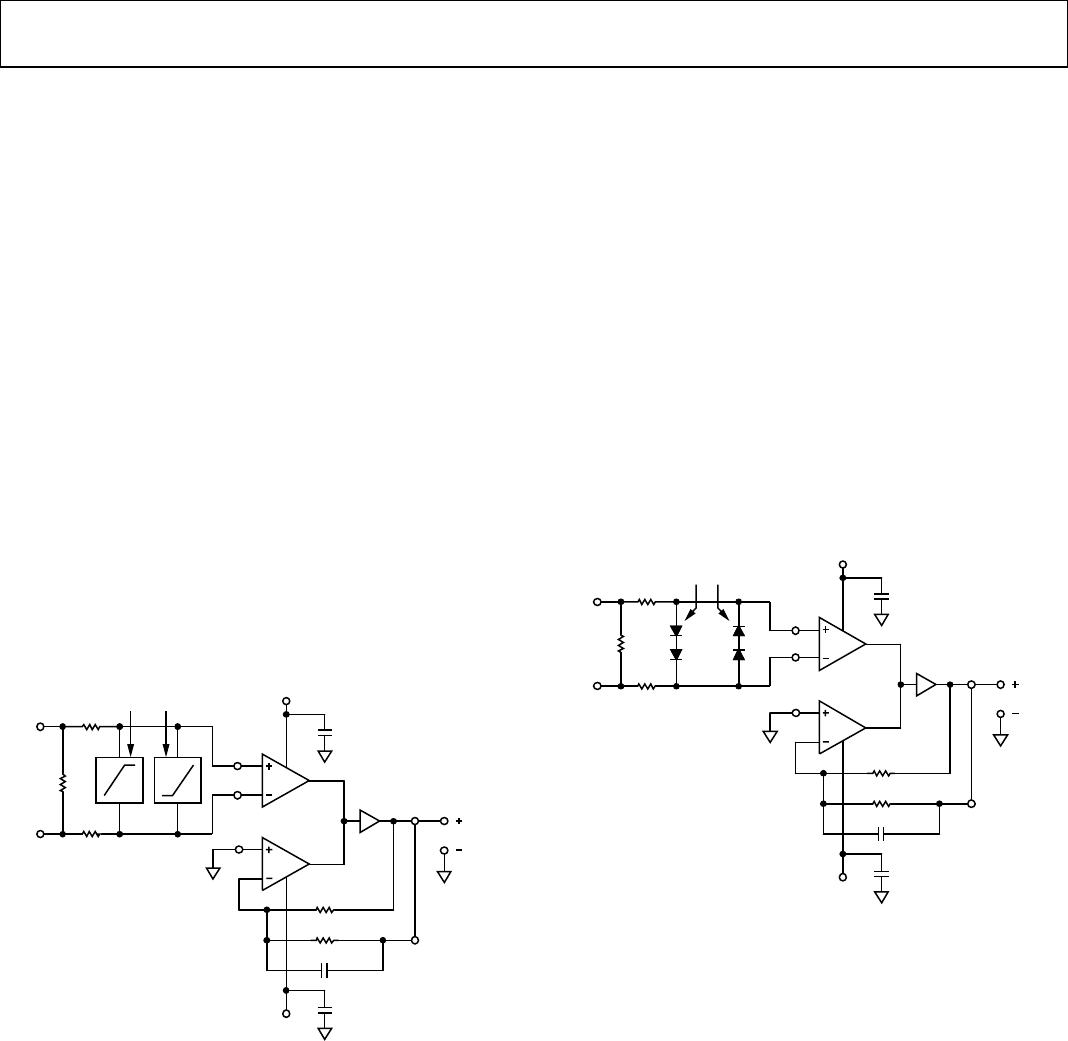

A 1N4448 diode has a forward voltage of approximately 0.70 V

to 0.75 V at typical current levels that are seen when it is being

used as a clamp, and 2 pF maximum capacitance at 0 V bias.

(The capacitance of a diode decreases as its reverse-bias voltage

is increased.) The series connection of two 1N4448 diodes,

therefore, has a clamping voltage of 1.4 V to 1.5 V. Figure 40

shows how to limit the differential input voltage applied to an

AD8145 amplifier to ±1.4 V to ±1.5 V (2.8 V p-p to 3.0 V p-p).

Note that the capacitance of the two series diodes is half that of

one diode. Different numbers of series diodes can be used to

obtain different clamping voltages.

R

T

is the differential termination resistor, and the series

resistances, R

S

, limit the current into the diodes. The series

resistors should be highly matched in value to preserve high

frequency CMRR.

POSITIVE CLAMP NEGATIVE CLAMP

R

S

R

T

V

IN

R

S

–

+

GAIN

REF

R

R

0.01µF

0.01µF

+5V

–5V

C

OUT

V

OUT

06307-041

Figure 40. Using Two 1N4448 Diodes in Series as a Clamp

Many other nonlinear devices can be used as clamps. The best

choice for a particular application depends upon the desired

clamping voltage, response time, parasitic capacitance, and

other factors.

When using external differential-mode clamping, it is important

to ensure that the series resistors (R

S

), the sum of the parasitic

capacitance of the clamping devices, and the input capacitance

of the AD8145 are small enough to preserve the desired signal

bandwidth.

Rev. B | Page 17 of 21