AD5203

–9–REV. 0

OPERATION

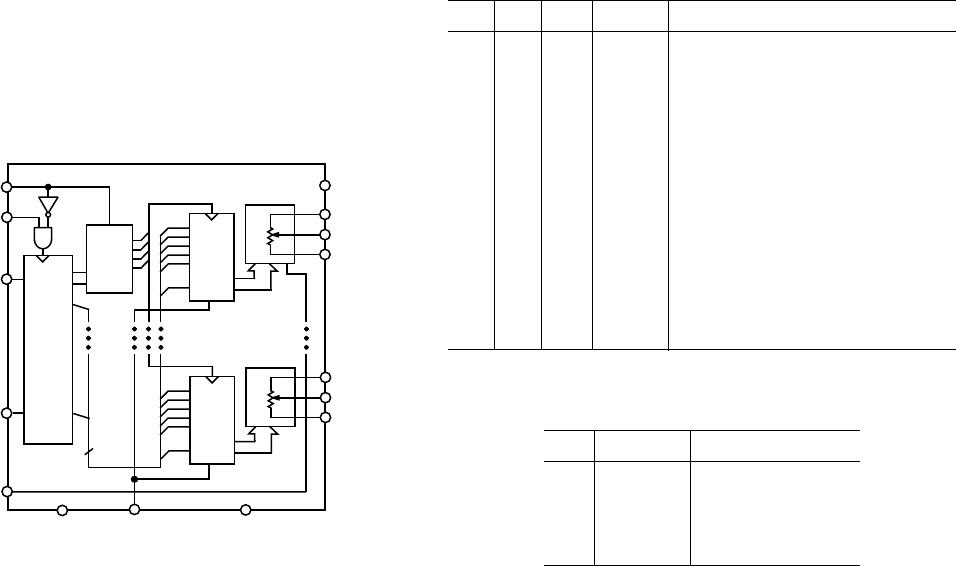

The AD5203 provides a quad channel, 64-position digitally-

controlled variable resistor (VR) device. Changing the pro-

grammed VR settings is accomplished by clocking in an 8-bit

serial data word into the SDI (Serial Data Input) pin. The for-

mat of this data word is two address bits, MSB first, followed by

six data bits, MSB first. Table I provides the serial register data

word format. The AD5203 has the following address assign-

ments for the ADDR decode, which determines the location of

VR latch receiving the serial register data in Bits B5 through B0:

VR# = A1 × 2 + A0 + 1

VR outputs can be changed one at a time in random sequence.

The serial clock running at 10 MHz makes it possible to load all

four VRs in under 3.2 µs (8 × 4 × 100 ns) for the AD5203. The

exact timing requirements are shown in Figure 1.

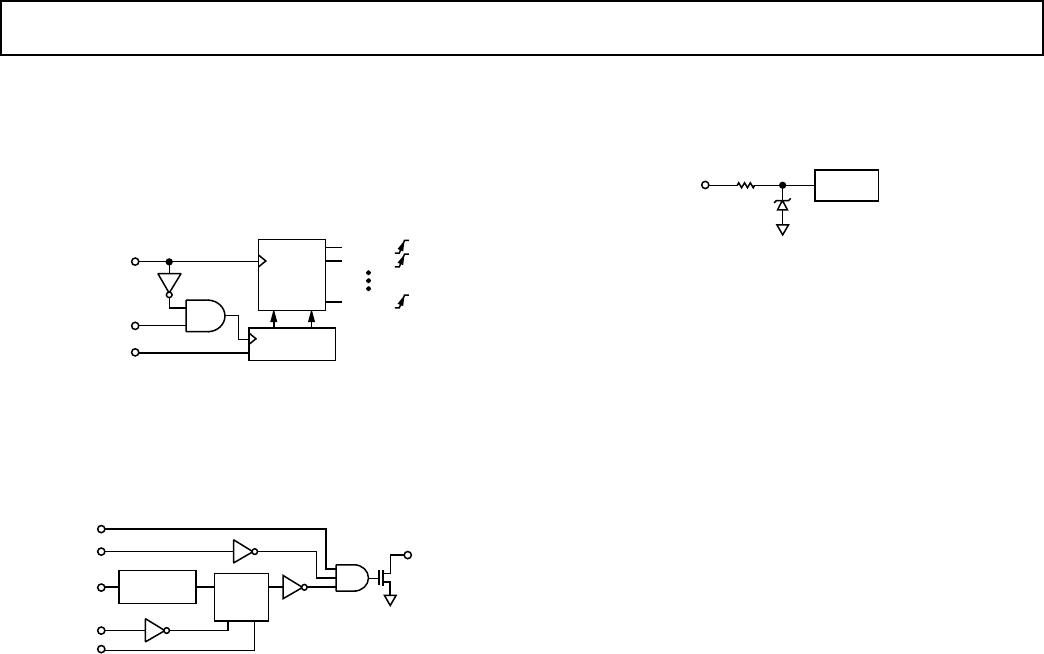

The AD5203 resets to a midscale by asserting the RS pin, sim-

plifying initial conditions at power-up. Both parts have a power

shutdown SHDN pin that places the RDAC in a zero power

consumption state where terminals Ax are open-circuited and

the wiper Wx is connected to Bx, resulting in only leakage cur-

rents being consumed in the VR structure. In shutdown mode

the VR latch settings are maintained so that, returning to opera-

tional mode from power shutdown, the VR settings return to

their previous resistance values.

D5

D4

D3

D2

D1

D0

RDAC

LATCH

&

DECODER

Ax

Wx

Bx

R

S

= R

AB

/64

R

S

R

S

R

S

R

S

SHDN

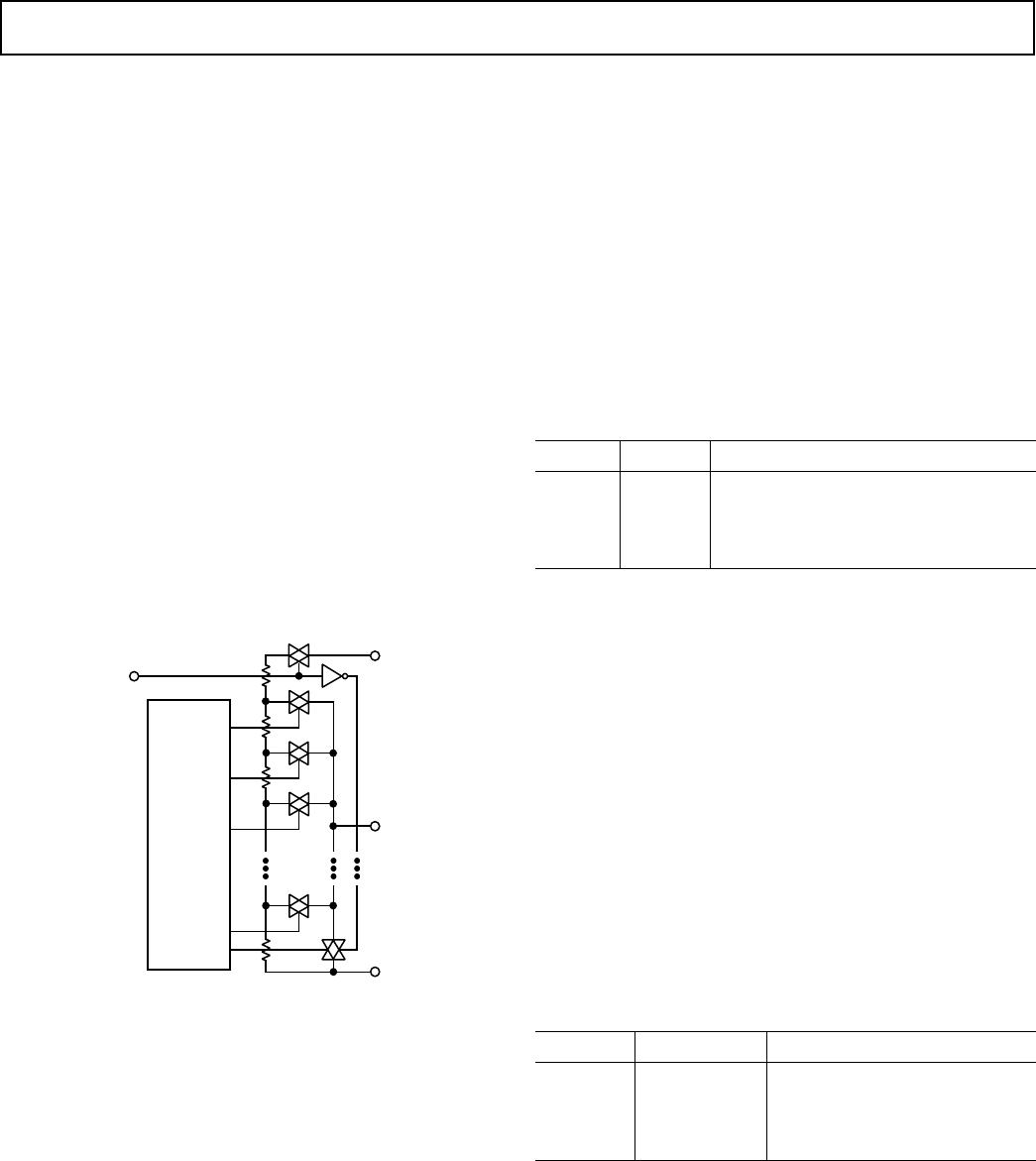

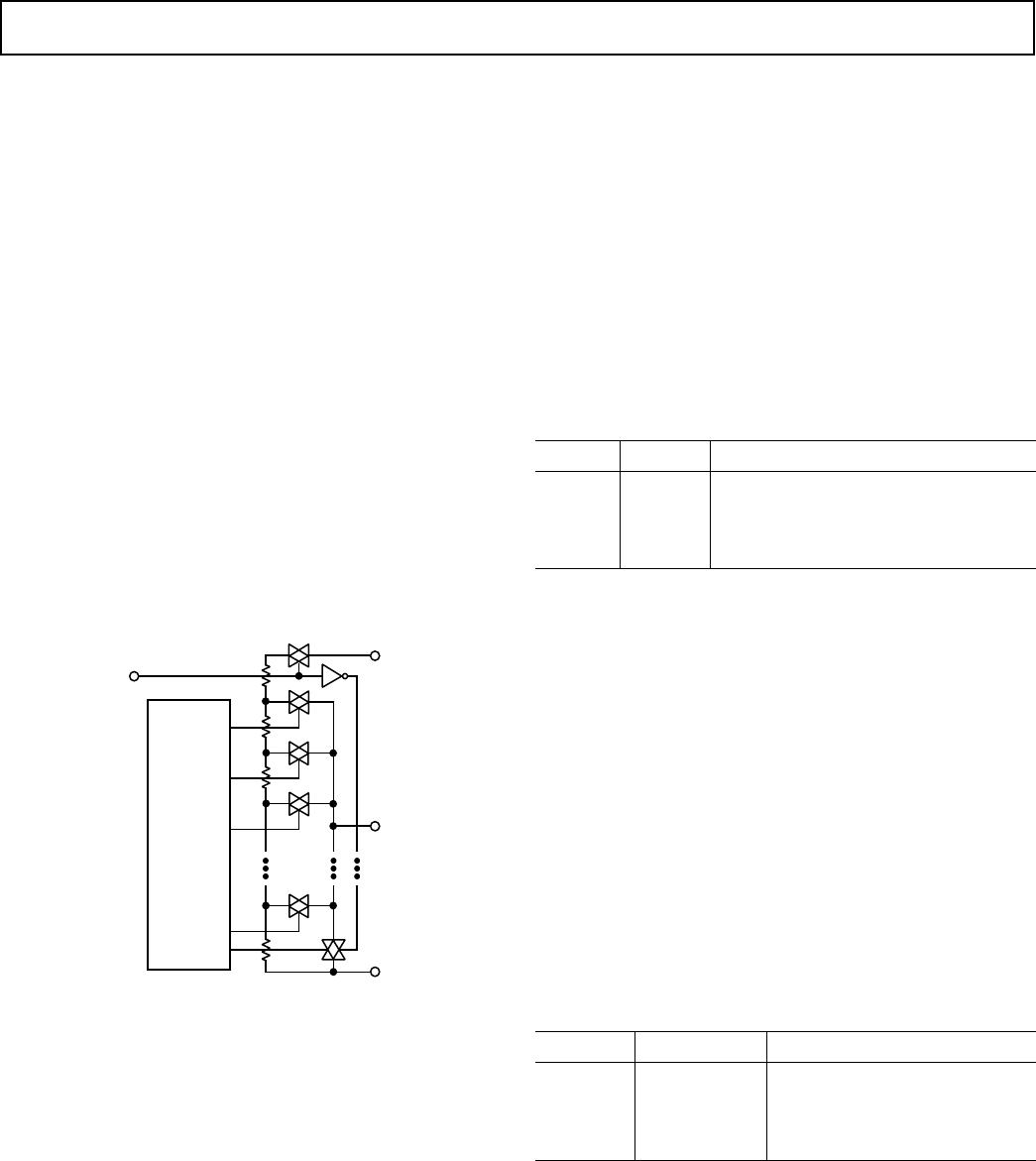

Figure 34. Equivalent RDAC Circuit

PROGRAMMING THE VARIABLE RESISTOR

Rheostat Operation

The nominal resistance of the RDAC between Terminals A and

B are available with values of 10 kΩ, and 100 kΩ. The final

digits of the part number determine the nominal resistance

value, e.g., 10 kΩ = 10; 100 kΩ = 100. The nominal resistance

(R

AB

) of the VR has 64 contact points accessed by the wiper

terminal, plus the B terminal contact. The 6-bit data word in

the RDAC latch is decoded to select one of the 64 possible

settings. The wiper’s first connection starts at the B terminal for

data 00

H

. This B–terminal connection has a wiper contact resis-

tance of 45 Ω. The second connection (10 kΩ part) is the first

tap point located at 201 Ω [= R

BA

(nominal resistance)/64 + R

W

= 156 Ω + 45 Ω)] for data 01

H

. The third connection is the next

tap point representing 312 + 45 = 357 Ω for data 02

H

. Each

LSB data value increase moves the wiper up the resistor ladder

until the last tap point is reached at 9889 Ω. The wiper does not

directly connect to the B Terminal. See Figure 34 for a simpli-

fied diagram of the equivalent RDAC circuit.

The general transfer equation that determines the digitally pro-

grammed output resistance between Wx and Bx is:

R

WB

(Dx) = (Dx)/64 × R

BA

+ R

W

(1)

where Dx is the data contained in the 6-bit RDACx latch and

R

BA

is the nominal end-to-end resistance.

For example, when V

B

= 0 V and A–terminal is open circuit the

following output resistance values will be set for the following

RDAC latch codes (applies to the 10K potentiometer):

D (DEC) R

WB

(⍀) Output State

63 9889 Full-Scale

32 5045 Midscale (RS = 0 Condition)

1 201 1 LSB

0 45 Zero-Scale (Wiper Contact Resistance)

Note that in the zero-scale condition a finite wiper resistance of

45 Ω is present. Care should be taken to limit the current flow

between W and B in this state to a maximum value of 5 mA to

avoid degradation or possible destruction of the internal switch

contact.

Like the mechanical potentiometer the RDAC replaces, it is

totally symmetrical. The resistance between the wiper W and

terminal A also produces a digitally controlled resistance R

WA

.

When these terminals are used the B–terminal should be tied to

the wiper. Setting the resistance value for R

WA

starts at a maxi-

mum value of resistance and decreases as the data loaded in the

latch is increased in value. The general transfer equation for this

operation is:

R

WA

(Dx) = (64-Dx)/64 × R

BA

+ R

W

(2)

where Dx is the data contained in the 6-bit RDACx latch and

R

BA

is the nominal end-to-end resistance. For example, when

V

A

= 0 V and B–terminal is tied to the wiper W, the following

output resistance values will be set for the following RDAC

latch codes:

D (DEC) R

WA

(⍀) Output State

63 201 Full-Scale

32 5045 Midscale (RS = 0 Condition)

1 9889 1 LSB

0 10045 Zero-Scale

The typical distribution of R

BA

from channel to channel matches

within ±1%. However, device-to-device matching is process-lot-

dependent, having a ±30% variation. The change in R

BA

with

temperature has a 700 ppm/°C temperature coefficient.