DS687F5 15

CS5343/4

Draft

3/10/15

4.4.1 Component Values

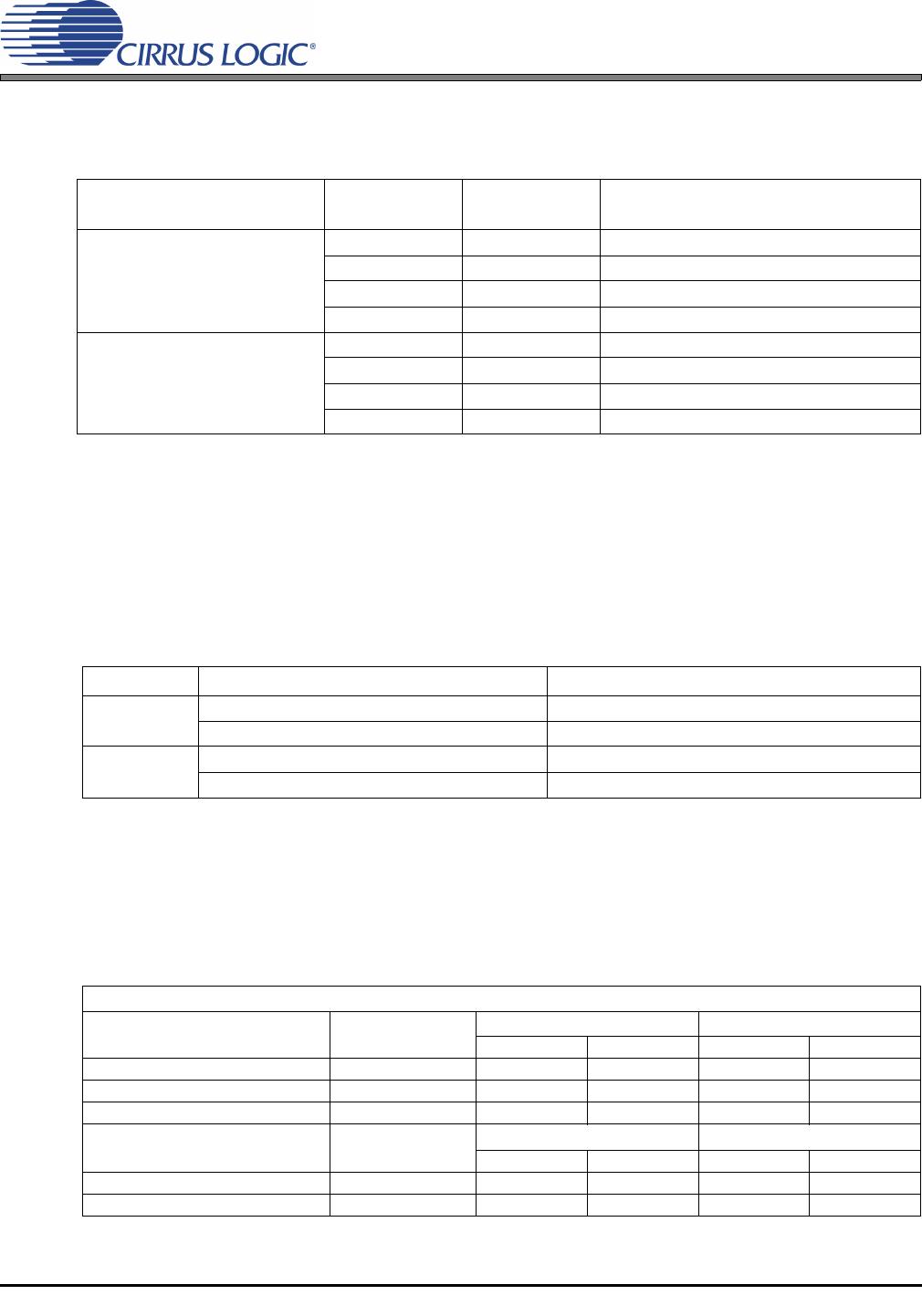

Three parameters determine the values of resistors R1 and R2 as shown in Figure 6: source impedance,

attenuation, and input impedance. Table 6 shows the design equation used to determine these values.

• Source Impedance: Source impedance is defined as the impedance as seen from the ADC looking

back into the signal network. The ADC achieves optimal THD+N performance with a source imped-

ance less than or equal to 2.5 k.

• Attenuation: The required attenuation factor depends on the magnitude of the input signal. The full-

scale input voltage is specified under “Analog Characteristics - Commercial Grade (-CZZ)” on page 5.

The user should select values for R1 and R2 such that the magnitude of the incoming signal multiplied

by the attenuation factor is less than or equal to the full-scale input voltage of the device.

• Input Impedance: Input impedance is the impedance from the signal source to the ADC analog input

pins, including the ADC. Because the ADC’s input impedance (see the “Analog Characteristics - Com-

mercial Grade (-CZZ)” table on page 5) is several orders of magnitude larger than the resistor values

typically used for the input attenuator, its contribution can be neglected when calculating the input im-

pedance. Table 6 shows the input parameters and the associated design equations for the input at-

tenuator.

Figure 7 illustrates an example configuration using two 4.99 kresistors in place of R1 and R2. Based on

the discussion above, this circuit provides an optimal interface for both the ADC and the signal source.

First, consumer equipment frequently requires an input impedance of 10 kwhich the 4.99 kresistors

provide. Second, this circuit will attenuate a typical line level voltage, 2 Vrms, to the full-scale input of the

ADC, 1 Vrms when VA = 5 V. Finally, at 2.5 kthe source impedance optimizes analog performance of

the ADC.

4.5 Grounding and Power Supply Decoupling

As with any high-resolution converter, designing with the CS5343/4 requires careful attention to power sup-

ply and grounding arrangements if its potential performance is to be realized. Figure 3 shows the recom-

mended power arrangements, with VA connected to a clean supply. Decoupling capacitors should be as

near to the ADC as possible, with the low value ceramic capacitor being the nearest. All signals, especially

clocks, should be kept away from the FILT+ and VQ pins in order to avoid unwanted coupling into the mod-

ulators. The FILT+ and VQ decoupling capacitors, particularly the 0.1 µF, must be positioned to minimize

the electrical path from FILT+ to GND. The CDB5343 evaluation board demonstrates the optimum layout

and power supply arrangements. To minimize digital noise, connect the ADC digital outputs only to CMOS

inputs.

Source Impedance

Attenuation Factor

Input Impedance

Table 6. Analog Input Design Parameters

R1 R2

R1 R2+

------------------------ -

R2

R1 R2+

-------------------------

Figure 7. CS5343/4 Example Analog Input Network

4.99 k

4.99 k

1 µF

180pF

C0G