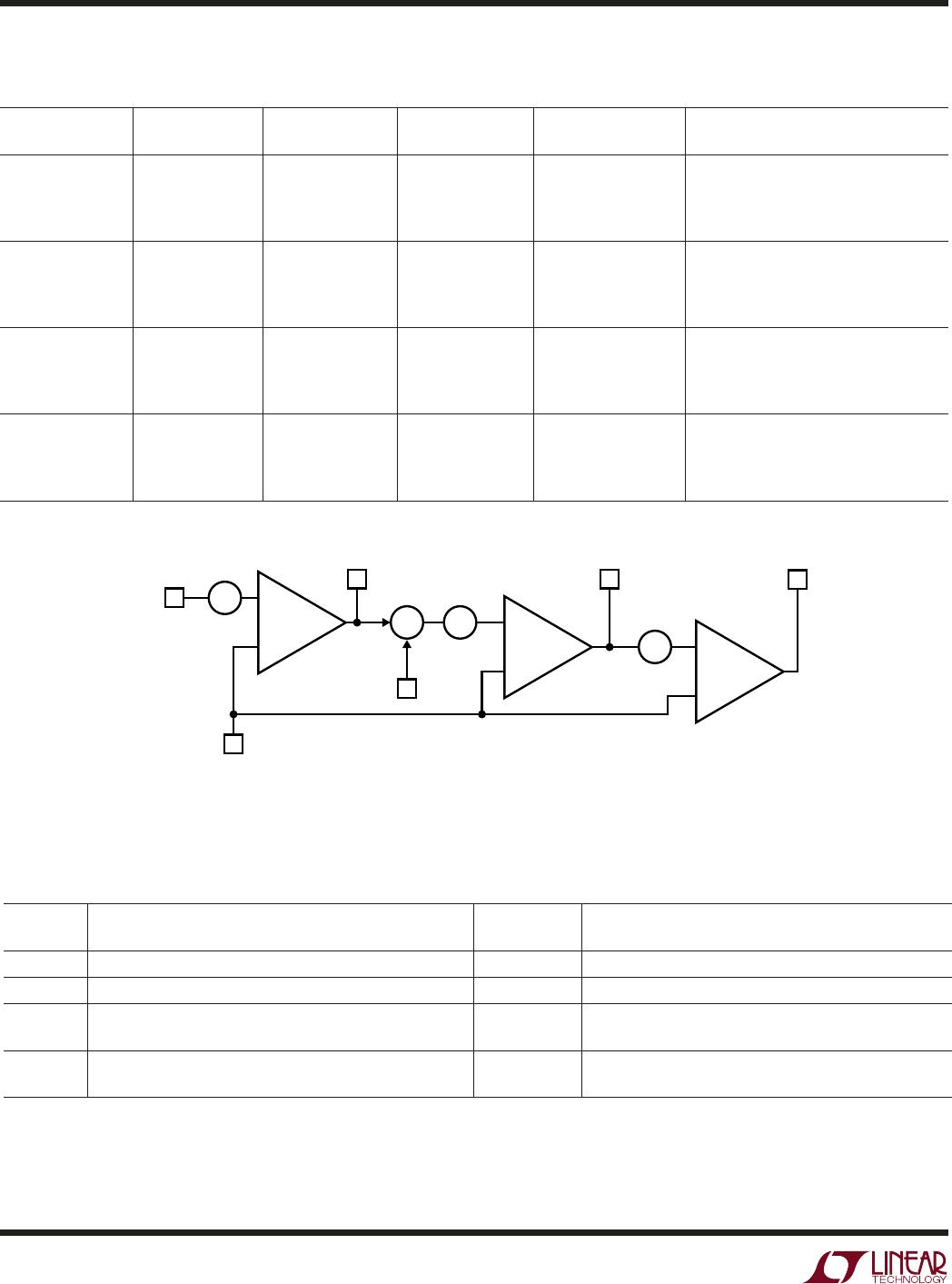

13

LTC1061

1061fe

f

IN

(kHz)

1

V

OUT

/V

IN

(dB)

–10

9

1061 F22

–30

–60

–80

3

5

7

0

–50

–40

–20

0

–70

–90

2

4

6810

STANDARD 1%

RESISTOR VALUES

R11 = 54.9k

R31 = 34.8k

R

h

1 = 28.7k

R22 = 68.1k

R42 = 10k

R

l

2 = 16.2k

R33 = 75k

R21 = 24.3k

R41 = 10k

R

l

1 = 280k

R32 = 18.2k

R

h

2 = 10.2k

R23 = 10k

R43 = 14k

NOTE: FOR CLOCK FREQUEN-

CIES ABOVE 300kHz, ADD

A CAPACITOR C ACROSS

R21 AND R22 SUCH AS

(1/2πR21C) = f

CLK

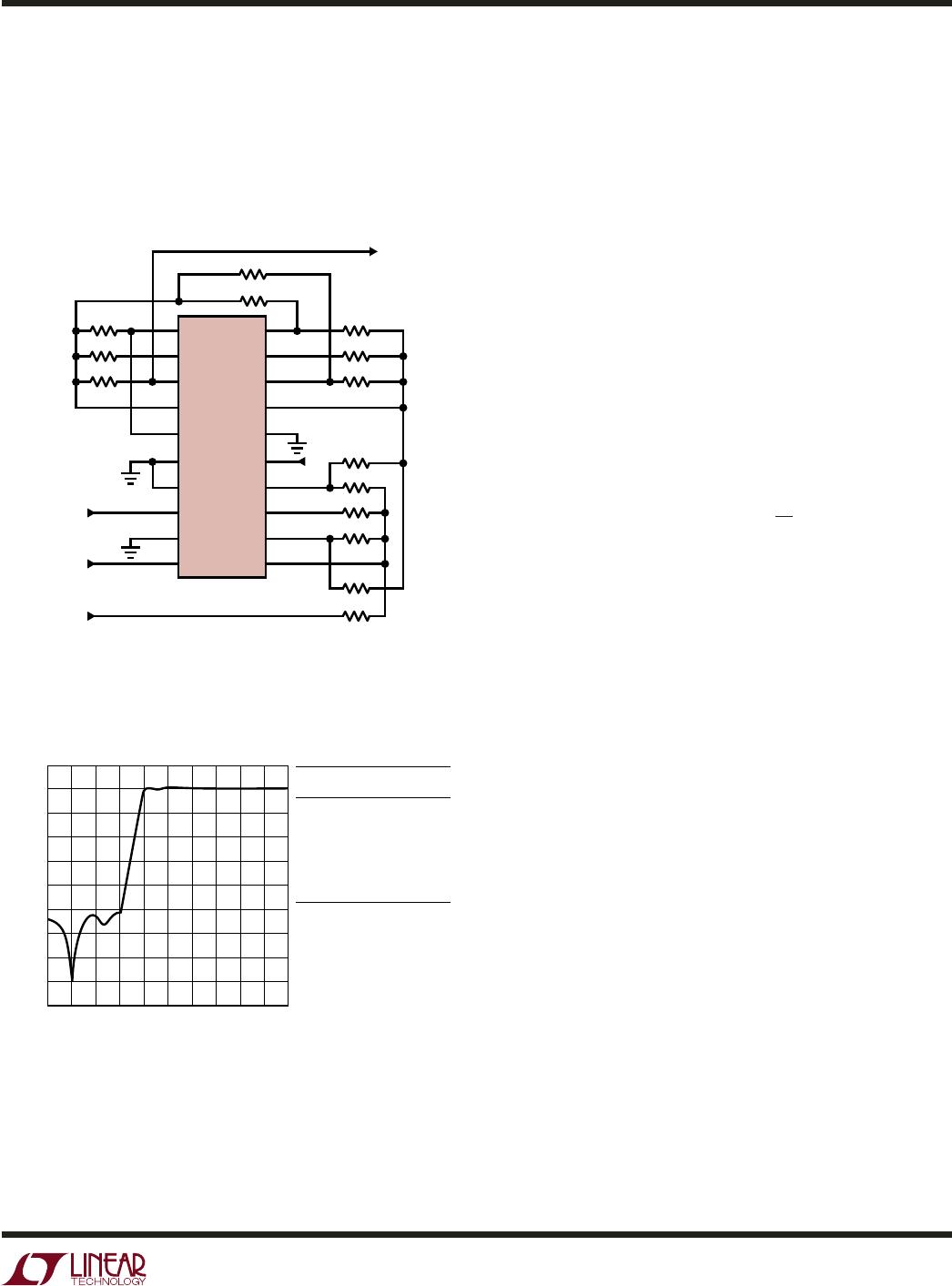

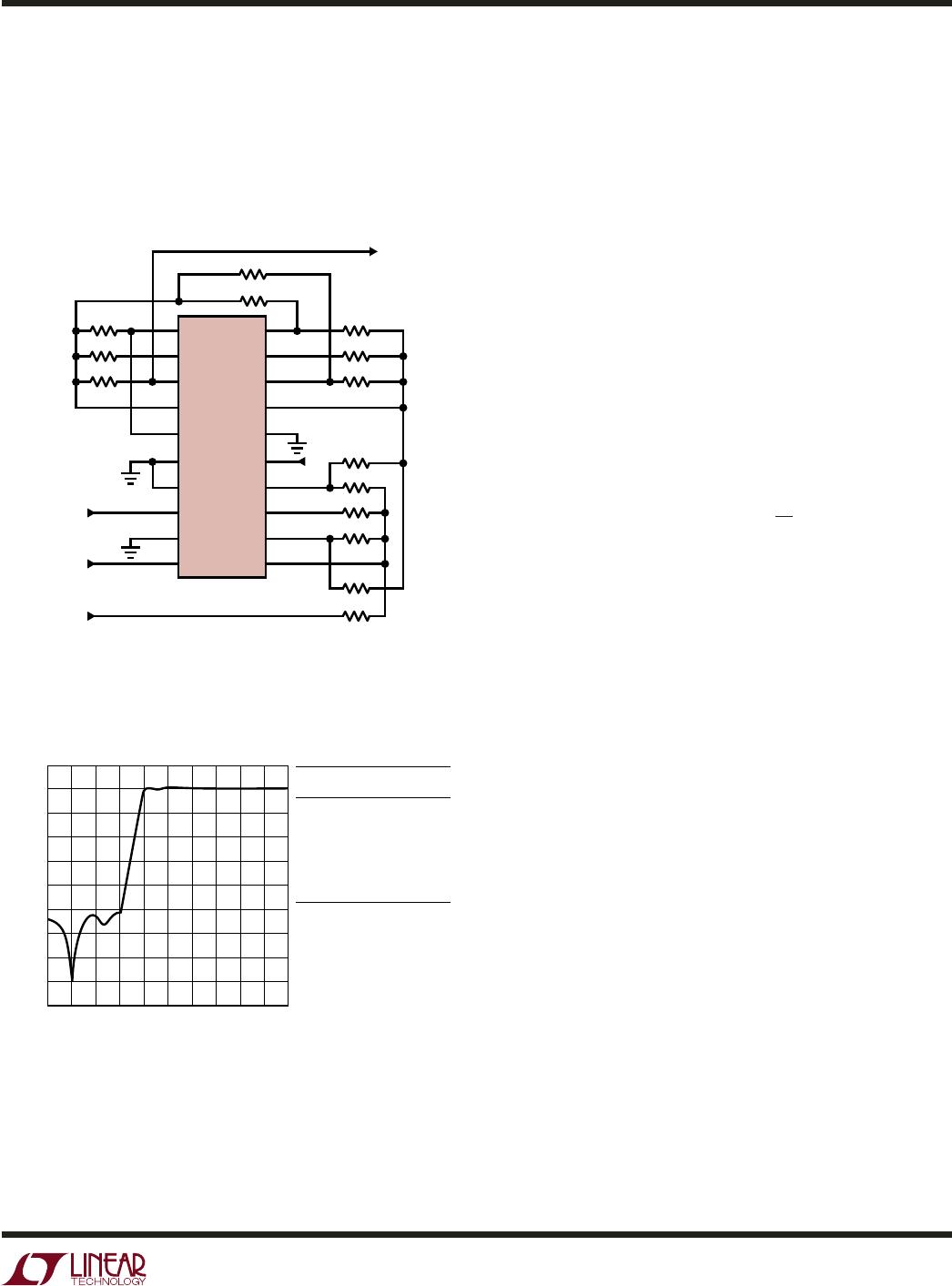

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

V

IN

1061 F21

LTC1061

R

h

2

R43

R33

T

2

L, CMOS

CLOCK INPUT

V

–

V

+

R

l

2

R32

R22

R42

R31

R41

R

l

1

R21

R11

R

h

1

R23

V

OUT

ODES OF OPERATIO

W

U

higher frequency notch provided by the side A of the

LTC1061. As shown in Figure 22, the highpass corner

frequency is 3.93kHz and the higher notch frequency is

3kHz while the filter operates with a 300kHz clock. The

center frequencies, Qs, and notches of Figure 22, when

normalized to the highpass cutoff frequency, are (f

O1

=

1.17, Q1 = 2.24, f

n1

= 0.242, f

O2

= 1.96, Q2 = 0.7, f

n2

= 0.6,

f

O3

= 0.987, f

n3

= 0.753, Q3 = 10). When compared with the

topology of Figure 16, this approach uses lower and more

restricted clock frequencies. The obtained notch in Mode

2 is shallower although the topology is more efficient.

Output Noise

The wideband RMS noise of the LTC1061 outputs is nearly

independent from the clock frequency. The LTC1061

noise when operating with ±2.5V supply is lower, as Table

3 indicates. The noise at the bandpass and lowpass

outputs increases rough as the √Q. Also the noise in-

creases when the clock-to-center frequency ratio is al-

tered with external resistors to exceed the internally set

100:1 or 50:1 ratios. Under this condition, the noise

increases square root-wise.

Output Offsets

The equivalent input offsets of the LTC1061 are shown in

Figure 23. The DC offset at the filter bandpass output is

always equal to V

OS3

. The DC offsets at the remaining two

outputs (Notch and LP) depend on the mode of operation

and external resistor ratios. Table 4 illustrates this.

It is important to know the value of the DC output offsets,

especially when the filter handles input signals with large

dynamic range. As a rule of thumb, the output DC offsets

increase when:

1. The Qs decrease

2. The ratio (f

CLK

/f

O

) increases beyond 100:1. This is

done by decreasing either the (R2/R4) or the R6/(R5

+ R6) resistor ratios.

Figure 21 shows the side A of the LTC1061 connected in

Mode 2 while sides B and C are in Mode 3a. This topology

can be used to synthesize elliptic bandpass, highpass and

notch filters. The elliptic highpass of Figure 17 is synthe-

sized again, Figure 22, but the clock is now locked onto the

Figure 22. 6th Order Elliptic Highpass Filter Operating with a

Clock-to-Cutoff Frequency Ratio of 75:1 and Using the Topology

of Figure 21

Figure 21. LTC1061 with Side A is Connected in Mode 2 While

Side B, C are in Mode 3a. Topology is Useful for Elliptic

Highpass, Notch and Bandpass Filters.