LT3481

13

3481fc

A fi nal precaution regarding ceramic capacitors concerns

the maximum input voltage rating of the LT3481. A ceramic

input capacitor combined with trace or cable inductance

forms a high quality (under damped) tank circuit. If the

LT3481 circuit is plugged into a live supply, the input volt-

age can ring to twice its nominal value, possibly exceeding

the LT3481’s rating. This situation is easily avoided (see

the Hot Plugging Safely section).

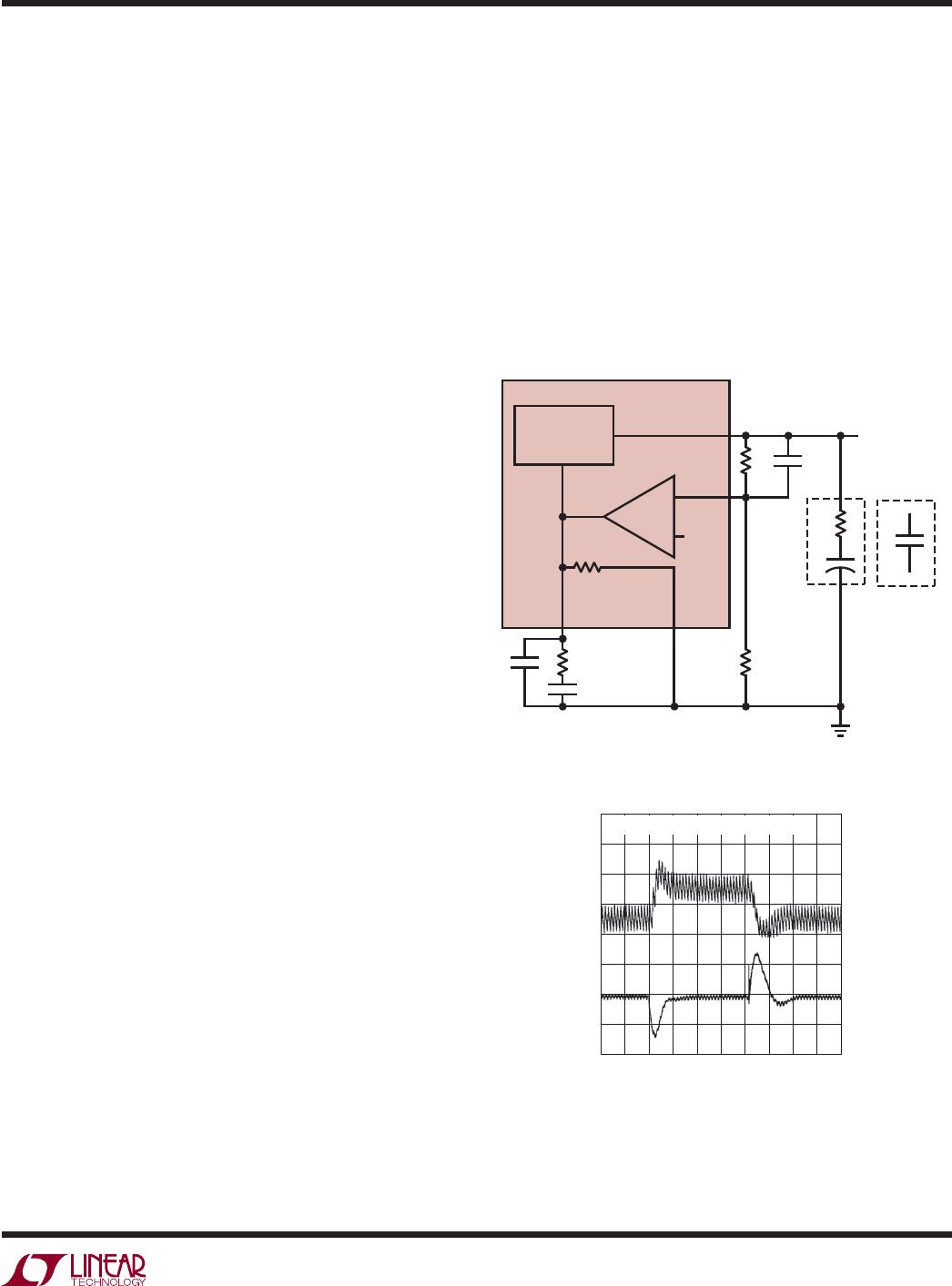

Frequency Compensation

The LT3481 uses current mode control to regulate the

output. This simplifi es loop compensation. In particular, the

LT3481 does not require the ESR of the output capacitor

for stability, so you are free to use ceramic capacitors to

achieve low output ripple and small circuit size. Frequency

compensation is provided by the components tied to the

V

C

pin, as shown in Figure 2. Generally a capacitor (C

C

)

and a resistor (R

C

) in series to ground are used. In addi-

tion, there may be lower value capacitor in parallel. This

capacitor (C

F

) is not part of the loop compensation but

is used to fi lter noise at the switching frequency, and is

required only if a phase-lead capacitor is used or if the

output capacitor has high ESR.

Loop compensation determines the stability and transient

performance. Designing the compensation network is

a bit complicated and the best values depend on the

application and in particular the type of output capacitor.

A practical approach is to start with one of the circuits in

this data sheet that is similar to your application and tune

the compensation network to optimize the performance.

Stability should then be checked across all operating

conditions, including load current, input voltage and

temperature. The LT1375 data sheet contains a more

thorough discussion of loop compensation and describes

how to test the stability using a transient load. Figure 2

shows an equivalent circuit for the LT3481 control loop.

The error amplifi er is a transconductance amplifi er with

fi nite output impedance. The power section, consisting

of the modulator, power switch and inductor, is modeled

as a transconductance amplifi er generating an output

current proportional to the voltage at the V

C

pin. Note that

the output capacitor integrates this current, and that the

capacitor on the V

C

pin (C

C

) integrates the error amplifi er

output current, resulting in two poles in the loop. In most

cases a zero is required and comes from either the output

capacitor ESR or from a resistor R

C

in series with C

C

.

This simple model works well as long as the value of the

inductor is not too high and the loop crossover frequency

is much lower than the switching frequency. A phase lead

capacitor (C

PL

) across the feedback divider may improve

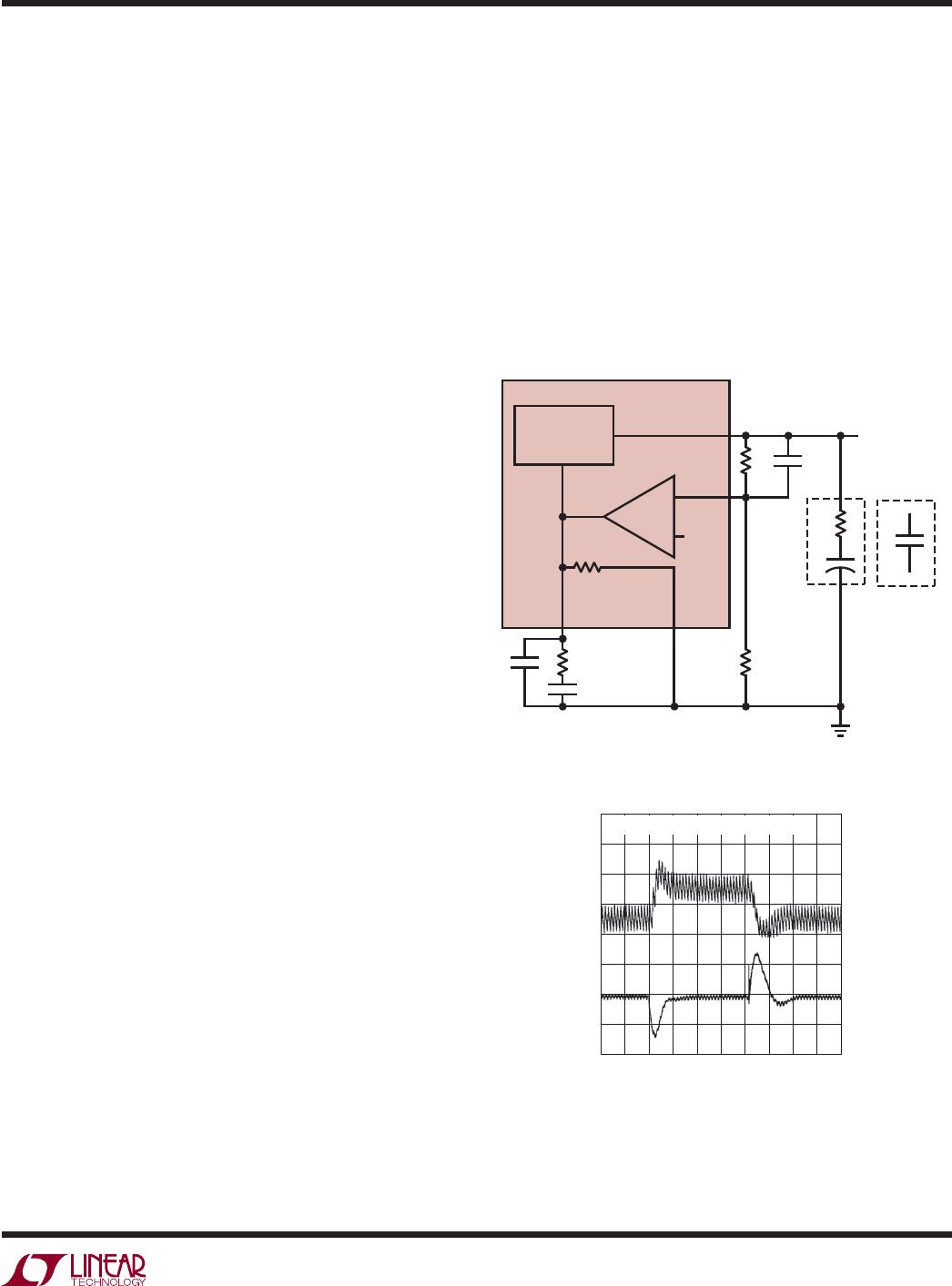

the transient response. Figure 3 shows the transient

response when the load current is stepped from 500mA

to 1500mA and back to 500mA.

–

+

1.265V

SW

V

C

GND

3Meg

LT3481

3481 F02

R1

OUTPUT

ESR

C

F

C

C

R

C

ERROR

AMPLIFIER

FB

R2

C1

C1

CURRENT MODE

POWER STAGE

g

m

= 3.5mho

g

m

=

330μmho

+

POLYMER

OR

TANTALUM

CERAMIC

C

PL

Figure 3. Transient Load Response of the LT3481 Front Page

Application as the Load Current is Stepped from 500mA to

1500mA. V

OUT

= 3.3V

Figure 2. Model for Loop Response

3481 F03

I

L

1A/DIV

V

OUT

100mV/DIV

10μs/DIV

V

OUT

= 12V; FRONT PAGE APPLICATION

APPLICATIONS INFORMATION