Acknowledged by Slave

A slave device, when addressed, is usually obliged to

generate an acknowledge after the receipt of each byte.

The master must generate the clock pulse for each

acknowledge bit. A slave that acknowledges must pull

down the SDA line during the acknowledge clock pulse

so that it remains stable low during the high period of this

clock pulse. Setup and hold times t

SU:DAT

and t

HD:DAT

must be taken into account.

Acknowledged by Master

To continue reading from a slave, the master is obliged

to generate an acknowledge after the receipt of each

byte. The master must generate the clock pulse for each

acknowledge bit. A master that acknowledges must pull

down the SDA line during the acknowledge clock pulse

so that it remains stable low during the high period of this

clock pulse. Setup and hold times t

SU:DAT

before the ris-

ing edge of SCL and t

HD:DAT

after the falling edge of SCL

must be taken into account.

Not Acknowledged by Slave

A slave device may be unable to receive or transmit data,

for example, because it is busy performing a real-time func-

tion such as MAC computation or EEPROM write cycle or

is in sleep mode. In this case, the slave does not acknowl-

edge its slave address and leaves the SDA line high. A

slave that is ready to communicate acknowledges at least

its slave address. However, some time later, the slave

might refuse to accept data, possibly because of an invalid

command code or unexpected data. In this case, the slave

device does not acknowledge any of the bytes that it

refuses and leaves SDA high. In either case, after a slave

has failed to acknowledge, the master first should generate

a repeated START condition or a STOP condition followed

by a START condition to begin a new data transfer.

Not Acknowledged by Master

At some time when receiving data, the master must signal

an end of data to the slave. To achieve this, the master

does not acknowledge the last byte that it has received

from the slave. In response, the slave releases SDA,

allowing the master to generate the STOP condition.

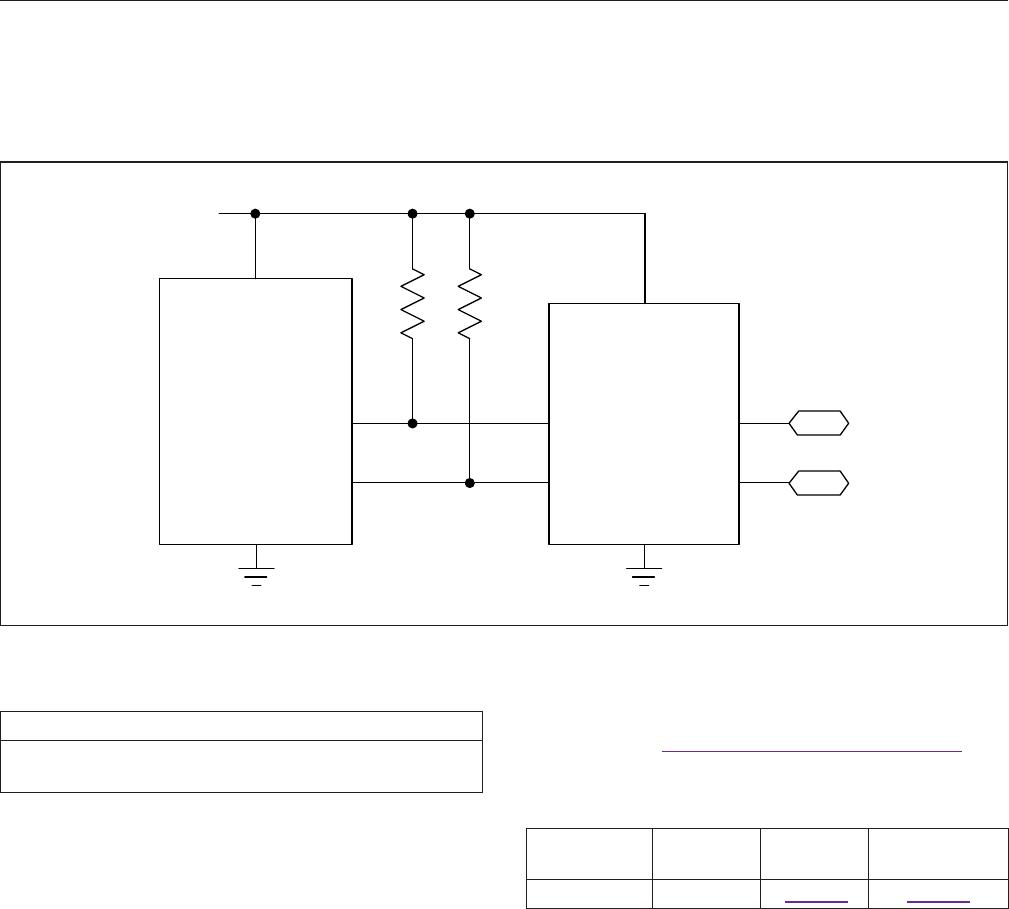

Read and Write

To write to the DS2476, the master must access the

device in write access mode, i.e., the slave address must

be sent with the direction bit set to 0. The next byte to be

sent in write access mode is command byte. To read from

the DS2476, the master must access the device in read

access mode, i.e., the slave address must be sent with

the direction bit set to 1. The read address is determined

either from a preceding write access or implied from a

function command.

DS2476 DeepCover Secure Coprocessor

www.maximintegrated.com

Maxim Integrated

│

7

ABRIDGED DATA SHEET