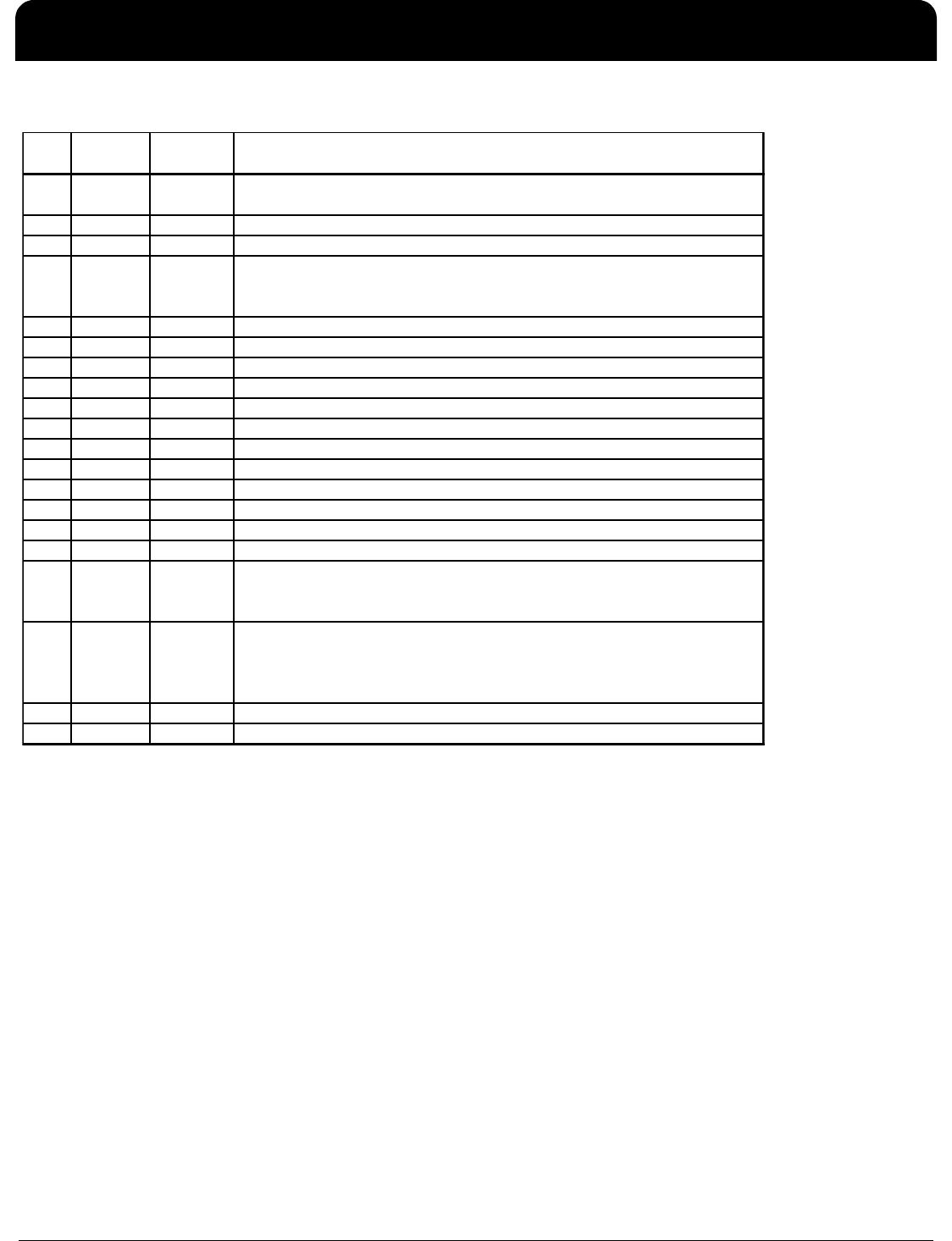

PIN #

PIN

NAME

PIN TYPE DESCRIPTION

1 PLL_BW IN

3.3V input for selecting PLL Band Width

0 = low, 1= high

2 SRC_IN IN 0.7 V Differential SRC TRUE input

3 SRC_IN# IN 0.7 V Differential SRC COMPLEMENTARY input

4 vOE0# IN

Active low input for enabling DIF pair 0. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

5 VDD PWR Power supply, nominal 3.3V

6 GND PWR Ground pin.

7 DIF_0 OUT 0.7V differential true clock output

8 DIF_0# OUT 0.7V differential Complementary clock output

9 VDD PWR Power supply, nominal 3.3V

10 SMBDAT I/O Data pin of SMBUS circuitry, 5V tolerant

11 SMBCLK IN Clock pin of SMBUS circuitry, 5V tolerant

12 VDD PWR Power supply, nominal 3.3V

13 DIF_1# OUT 0.7V differential Complementary clock output

14 DIF_1 OUT 0.7V differential true clock output

15 GND PWR Ground pin.

16 VDD PWR Power supply, nominal 3.3V

17 vOE1# IN

Active low input for enabling DIF pair 1. This pin has an internal pull-down.

1 =disable outputs, 0 = enable outputs

18 IREF OUT

This pin establishes the reference for the differential current-mode output

pairs. It requires a fixed precision resistor to ground. 475ohm is the standard

value for 100ohm differential impedance. Other impedances require

different values. See data sheet.

19 GNDA PWR Ground pin for the PLL core.

20 VDDA PWR 3.3V power for the PLL core.

Pins preceeded by ' v ' have internal 120K ohm pull down resistors