9DB233

TWO OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3

IDT®

TWO OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3 6

9DB233 OCTOBER 20, 2016

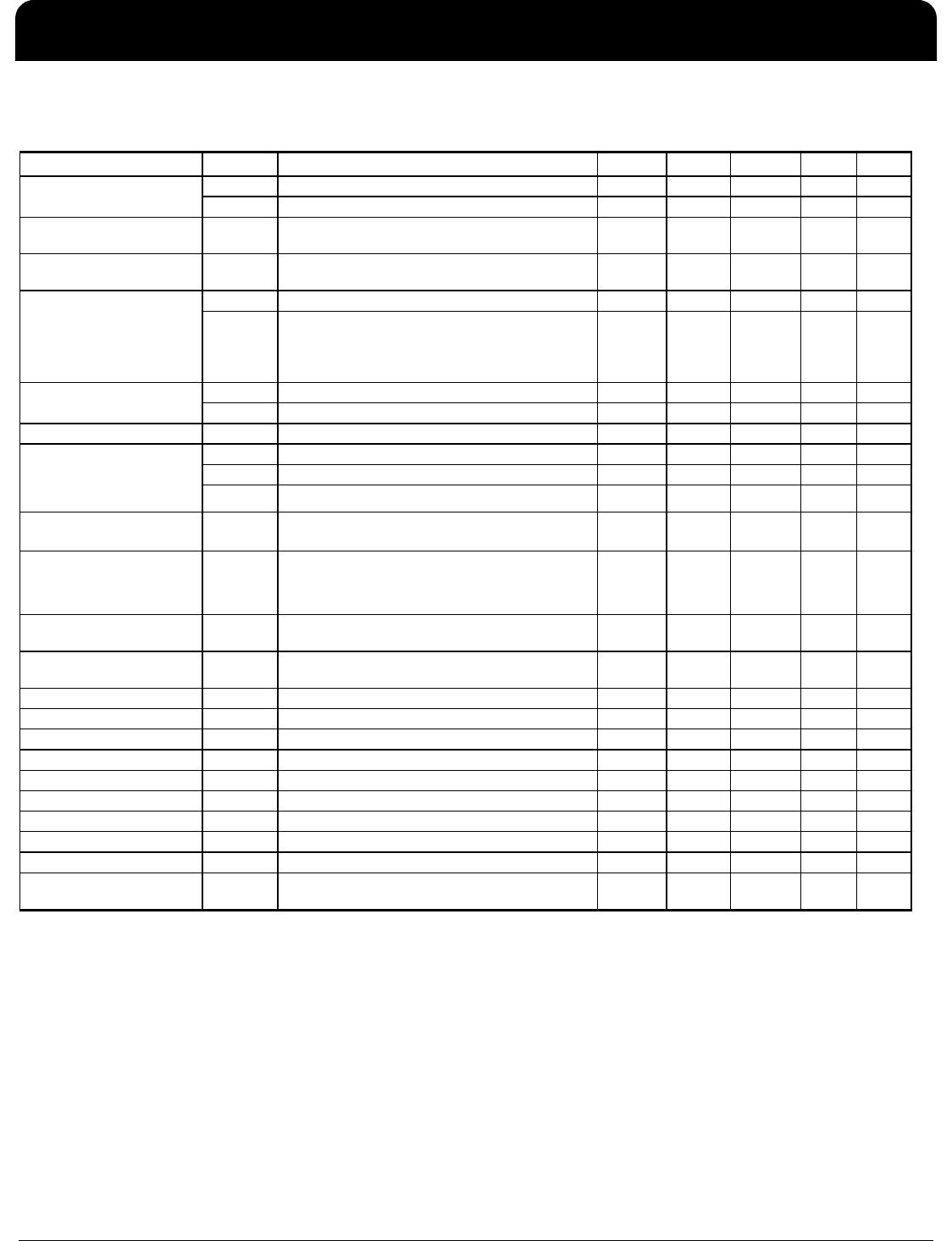

Electrical Characteristics–DIF 0.7V Current Mode Differential Outputs

Electrical Characteristics–Output Duty Cycle, Jitter, Skew and PLL Characteristics

T

A

= T

COM

or T

IND;

Supply Voltage VDD = 3.3 V +/-5%

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Slew rate Trf Scope avera

in

on 0.6 2 4

1, 2, 3

Slew rate matching

∆

Trf Slew rate matching, Scope averaging on 4.2 20

%

1, 2, 4

Voltage High VHigh 660 791 850 1

Voltage Low VLow -150 13 150 1

Max Voltage Vmax 801 1150 1

Min Voltage Vmin -300 5 1

Vswin

Vswin

Scope avera

in

off 300 1557 mV 1, 2

Crossing Voltage (abs) Vcross_abs Scope averaging off 250 367 550 mV 1, 5

Crossing Voltage (var)

∆

-Vcross Scope averaging off 46 140 mV 1, 6

2

Measured from differential waveform

6

The total variation of all Vcross measurements in any particular system. Note that this is a subset of V_cross_min/max (V_cross

absolute

allowed. The intent is to limit Vcross induced modulation b

settin

V_cross_delta to be smaller than V_cross absolute.

mV

Statistical measurement on single-ended signal

using oscilloscope math function. (Scope

averaging on)

Measurement on single ended signal using

absolute value. (Scope averaging off)

mV

1

Guaranteed by design and characterization, not 100% tested in production. IREF = VDD/(3xR

R

). For R

R

= 475

Ω

(1%), I

REF

= 2.32mA.

I

OH

= 6 x I

REF

and V

OH

= 0.7V @ Z

O

=50

Ω

(100

Ω

differential impedance).

3

Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around

differential 0V.

4

Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on

the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the

oscilloscope is to use for the edge rate calculations.

5

Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising

edge (i.e. Clock rising and Clock# falling).

TA = T

COM

or T

IND;

Supply Voltage VDD = 3.3 V +/-5%

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

-3dB point in Hi

h BW Mode 2 2.2 4 MHz 1

-3dB point in Low BW Mode 0.4 0.5 1 MHz 1

PLL Jitter Peaking t

JPEAK

Peak Pass band Gain 0.6 1.5 dB 1

Duty Cycle t

D

Measured differentially, PLL Mode 45 48 55 % 1

Duty Cycle Distortion t

DCD

Measured differentially, Bypass Mode @100MHz -2 0.4 2 % 1,4

t

dBYP

= 50% 2500 3660 4500 ps 1

t

dPLL

= 50% -50 136 350 ps 1

Skew, Output to Output t

sk3

= 50% 16 50 ps 1

PLL mode 29 50 ps 1,3

Additive Jitter in Bypass Mode 0.2 50 ps 1,3

1

Guaranteed by design and characterization, not 100% tested in production.

2

I

RE

DD

R

R

RE

OH

RE

OH

O

=50

Ω

.

3

Measured from differential waveform

4

Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

Skew, Input to Output

Jitter, Cycle to cycle t

jcyc-cyc

PLL Bandwidth BW