AD22057

–7–

REV. A

APPLICATION HINTS

Frequency Compensation

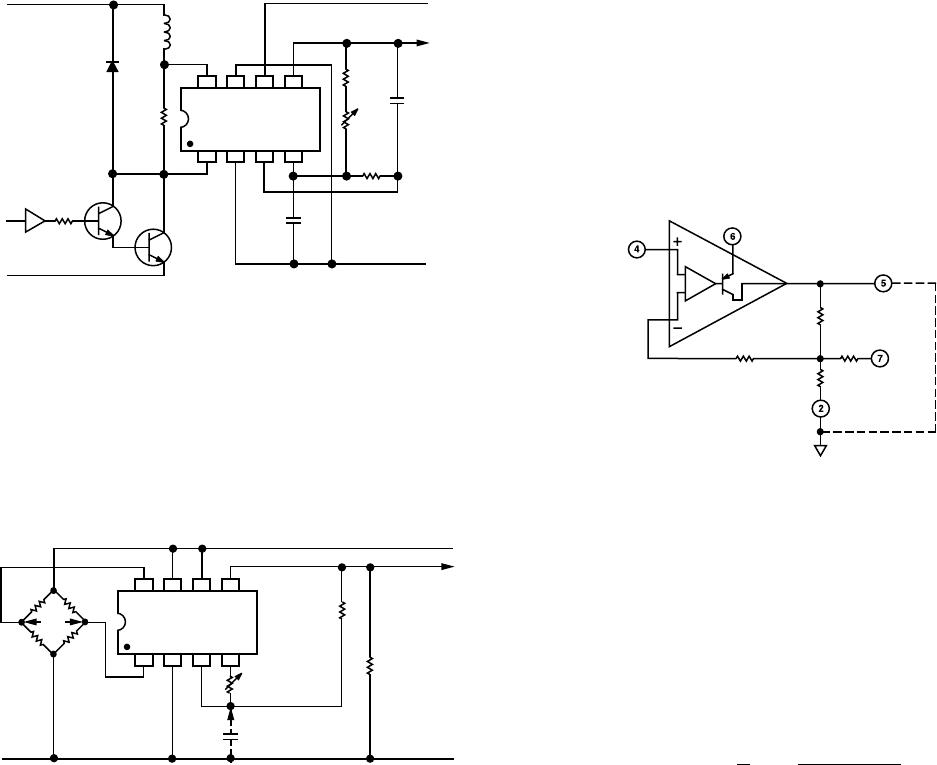

As are all closed-loop op amp circuits, the AD22057 is sensitive

to capacitive loading at its output. However, the AD22057 is

sensitive at higher output voltages due to nonlinear effects in

the rail-to-rail design of the buffer amplifier (A2). In this

amplifier the output stage gain increases with increasing output

voltage. This behavior does not affect dc parameters such as

gain accuracy or linearity; however, it can compromise ac sta-

bility. When operating from a power supply of 5 V or less (and,

therefore, V

OUT

< 5 V), the AD22057 can drive capacitive

loads up to 25 pF with no external components. When operat-

ing at higher supply voltages (which are associated with higher

output voltages) and/or driving larger capacitive loads, an exter-

nal compensation network should be used. Figure 14 shows an

R-C “snubber” circuit loading the output of the AD22057.

This combination, in conjunction with the internal 20 kΩ resis-

tance, forms a lag network. This network attenuates the open-

loop gain of the amplifier at higher frequencies. The ratio of

R

LAG

to the load seen by the AD22057 determines the high

frequency attenuation seen by the op amp. If R

LAG

is made

1/20th of the total load resistance (≈20 kΩ储R

L

), then 26 dB of

attenuation is obtained at higher frequencies. The capacitor

(C

LAG

) is used to control the frequency of the compensation

network. It should be set to form a 5 µs time constant with the

resistor (R

LAG

). Table I shows the recommended values of

R

LAG

and C

LAG

for various values of external load resistor R

L

.

Ten percent tolerance on these components is acceptable.

Alternatively, the signal may be taken from the midpoint of

R

LAG

–C

LAG

. This output is particularly useful when driving

CMOS analog-to-digital converters. For more information see

the section Driving Charged Redistributed A/D Converters.

Note that when implementing this network large signal re-

sponse is compromised. This occurs because there is no active

pull-down and the lag capacitor must discharge through the

internal feedback resistor (20 kΩ) giving a fairly long-time

constant. For example if C

LAG

= 0.01 µF, the large signal

negative slew characteristic is a decaying exponential with a

time constant of ≈200 µs.

Table I. Compensation Components vs. External Load

Resistor

R

L

R

LAG

C

LAG

>100 kΩ 470 Ω 0.01 µF

> 50 kΩ 390 Ω 0.01 µF

> 20 kΩ 270 Ω 0.047 µF

> 10 kΩ 200 Ω 0.047 µF

> 5 kΩ 100 Ω 0.1 µF

> 2 kΩ 47 Ω 0.22 µF

Driving Charge Redistribution A/D Converters

When driving CMOS ADCs, such as those embedded in popu-

lar microcontrollers, the charge injection (∆Q) can cause a

significant deflection in the AD22057 output voltage. Though

generally of short duration, this deflection may persist until

after the sample period of the ADC has expired. It is due to the

relatively high open-loop output impedance of the AD22057.

The effect can be significantly reduced by including the same

R-C network recommended for improving stability (see Fre-

quency Compensation section). The large capacitor in the lag

network helps to absorb the additional charge, effectively lower-

ing the high frequency output impedance of the AD22057. For

these applications the output signal should be taken from the

midpoint of the R

LAG

–C

LAG

combination as shown in Figure 15.

Since the perturbations from the analog-to-digital converter are

small, the output of the AD22057 will appear to be a low

impedance. The transient response will, therefore, have a

time constant governed by the product of the two lag compo-

nents, C

LAG

× R

LAG

. For the values shown in Figure 15, this

time constant is programmed at approximately 10 µs. There-

fore, if samples are taken at several tens of microseconds or more,

there will be negligible “stacking up” of the charge injections.

10kV

+V

S

10kV

LOAD

AD22057

A2

R

LAG

C

LAG

R

L

C

L

Figure 14. Using an R-C Network for Compensation

0.01mF

1kV

10kV

+V

S

10kV

AD22057

A2

mPROCESSOR

A/D

IN

Figure 15. Recommended Circuit for Driving CMOS A/D

Converters

UNDERSTANDING THE AD22057

Figure 16 shows the main elements of the AD22057. The signal

inputs at Pins 1 and 8 are first applied to dual resistive attenua-

tors R1 through R4, whose purpose is to reduce the common-

mode voltage at the input to the preamplifier. The attenuated

signal is then applied to a feedback amplifier based on the very

low drift op amp, A1. The differential voltage across the inputs

is accurately amplified in the presence of common-mode volt-

ages of many times the supply voltage. The overall common-

mode response is minimized by precise laser trimming of R3

and R4, giving the AD22057 a common-mode rejection ratio

(CMRR) of at least 80 dB (10,000:1).

The common-mode range of A1 extends from slightly below

ground to 1 V below +V

S

(at the minimum temperature of

–40°C). Since an attenuation ratio of about 6 is used, the input

common-mode range is –1 V to +24 V using a +5 V supply.

Small filter capacitors C1 and C2 are included to minimize the

effects of spurious RF signals at the inputs, which might cause

dc errors due to the rectification effects at the input to A1. At

high frequencies, even a small imbalance in these components

would seriously degrade the CMRR, so a special high frequency

trim is also carried out during manufacture.