13

IDT70V659/58/57S

High-Speed 3.3V 128/64/32K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

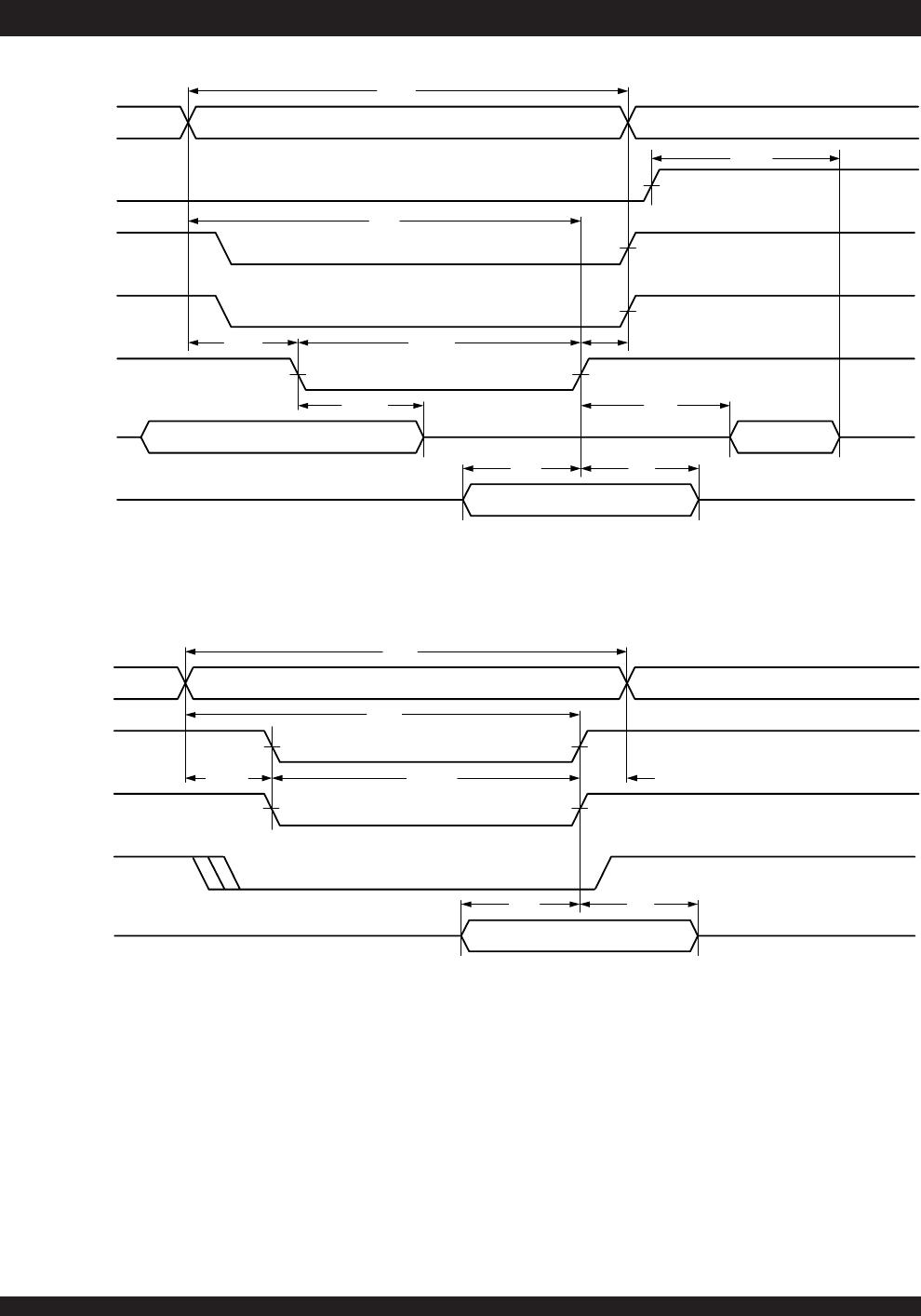

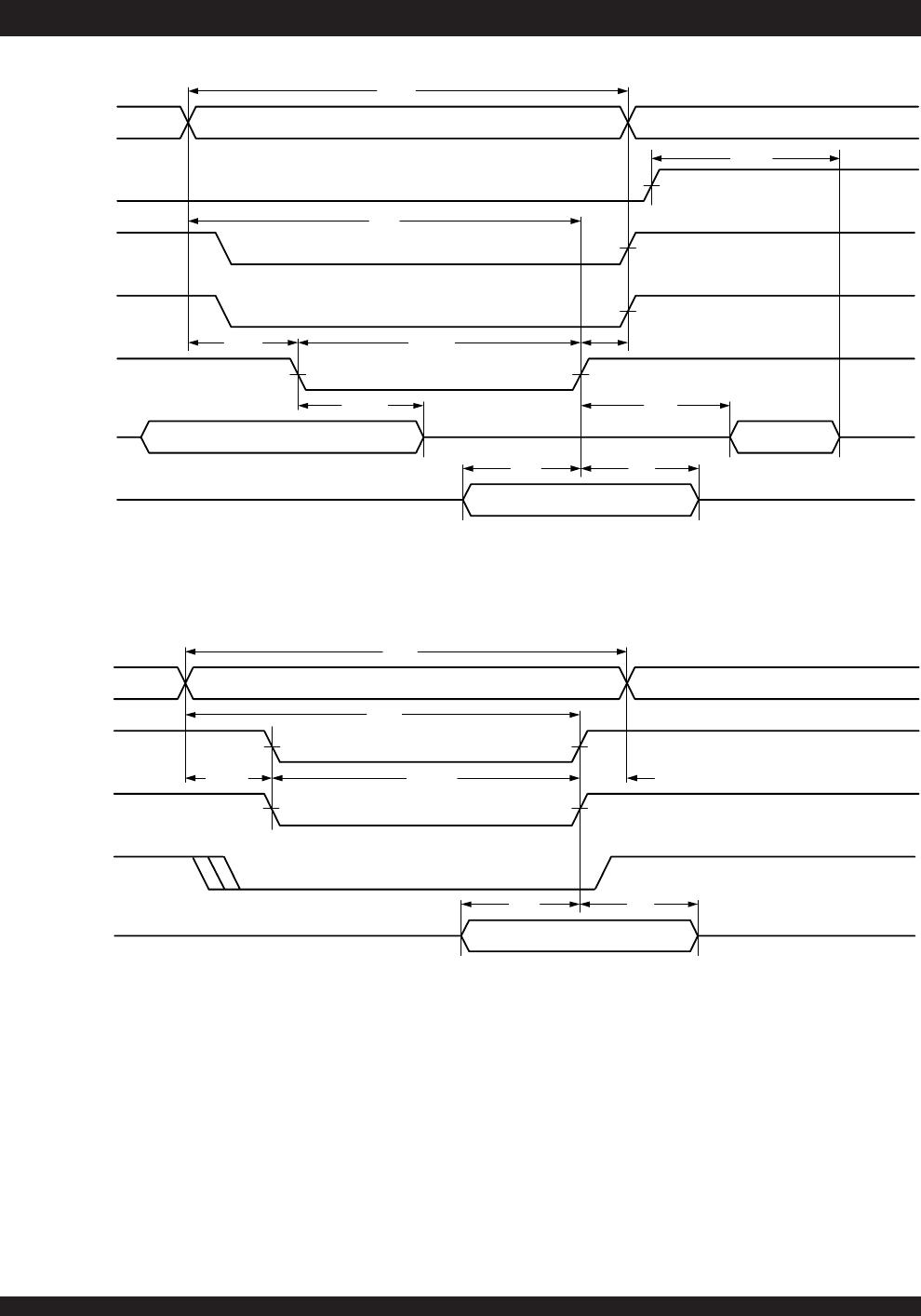

Timing Waveform of Write Cycle No. 1, R/W Controlled Timing

(1,5,8)

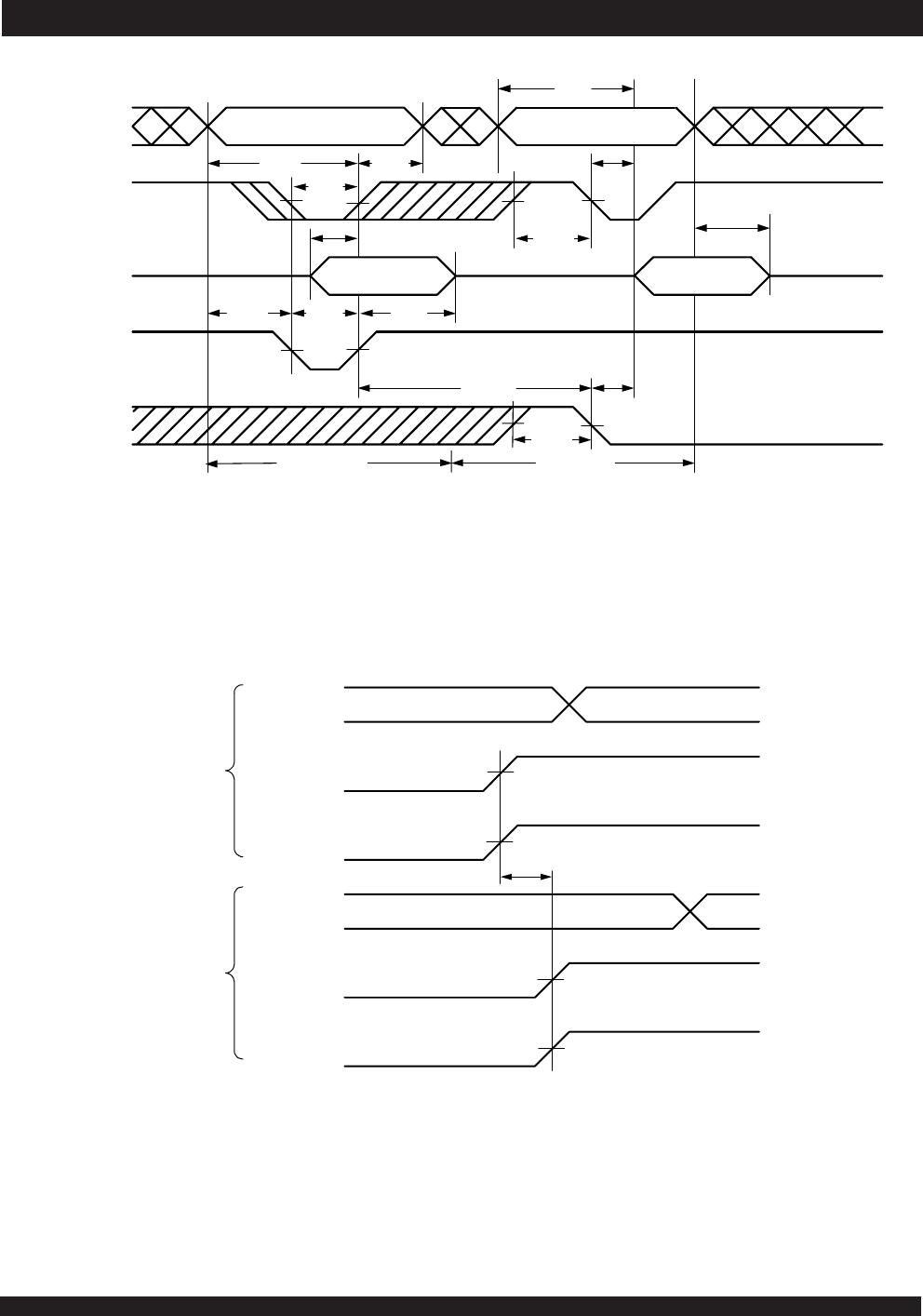

Timing Waveform of Write Cycle No. 2, CE Controlled Timing

(1,5)

NOTES:

1. R/W or CE or BEn = V

IH during all address transitions.

2. A write occurs during the overlap (t

EW or tWP) of a CE = VIL and a R/W = VIL for memory array writing cycle.

3. t

WR is measured from the earlier of CE or R/W (or SEM or R/W) going HIGH to the end of write cycle.

4. During this period, the I/O pins are in the output state and input signals must not be applied.

5. If the CE or SEM = V

IL transition occurs simultaneously with or after the R/W = VIL transition, the outputs remain in the High-impedance state.

6. Timing depends on which enable signal is asserted last, CE or R/W.

7. This parameter is guaranteed by device characterization, but is not production tested. Transition is measured 0mV from steady state with the Output Test Load

(Figure 2).

8. If OE = V

IL during R/W controlled write cycle, the write pulse width must be the larger of tWP or (tWZ + tDW) to allow the I/O drivers to turn off and data to be

placed on the bus for the required t

DW. If OE = VIH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the

specified t

WP.

9. To access RAM, CE = V

IL and SEM = VIH. To access semaphore, CE = VIH and SEM = VIL. tEW must be met for either condition.

R/W

t

WC

t

HZ

t

AW

t

WR

t

AS

t

WP

DATA

OUT

(2)

t

WZ

t

DW

t

DH

t

OW

OE

ADDRESS

DATA

IN

(6)

(4) (4)

(7)

BEn

4869 drw 08

(9)

CE or SEM

(9)

(7)

(3)

4869 drw 09

t

WC

t

AS

t

WR

t

DW

t

DH

ADDRESS

DATA

IN

R/W

t

AW

t

EW

BEn

(3)

(2)

(6)

CE or SEM

(9)

(9)