ADM696/ADM697

REV. 0

–7–

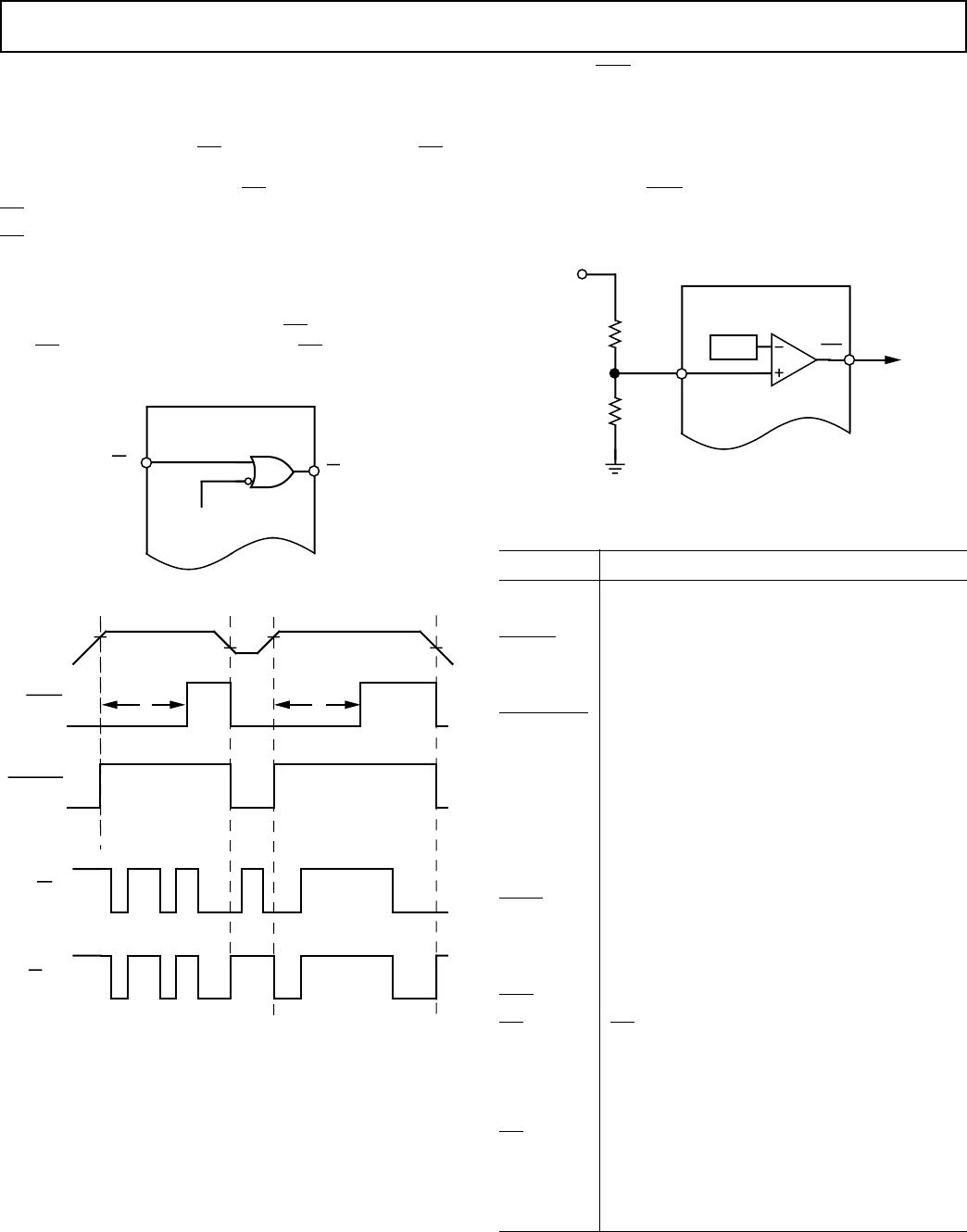

Fail Output (PFO) goes low when the voltage at PFI is less than

1.3 V. Typically PFI is driven by an external voltage divider

which senses either the unregulated dc input to the system’s 5 V

regulator or the regulated 5 V output. The voltage divider ratio

can be chosen such that the voltage at PFI falls below 1.3 V

several milliseconds before the +5 V power supply falls below

the reset threshold.

PFO is normally used to interrupt the

microprocessor so that data can be stored in RAM and the shut-

down procedure executed before power is lost.

ADM69x

POWER

FAIL

INPUT

R2

INPUT

POWER

1.3V

PFO

POWER

FAIL

OUTPUT

R1

Figure 7. Power Fail Comparator

Table II. Input and Output Status In Battery Backup Mode

Signal Status

V

OUT

(ADM696) V

OUT

is connected to V

BATT

via an

internal PMOS switch.

RESET Logic low.

RESET Logic high. The open circuit output voltage is

equal to V

OUT

.

LOW LINE Logic low.

BATT ON (ADM696) Logic high. The open circuit voltage

is equal to V

OUT

.

WDI WDI is ignored. It is internally disconnected

from the internal pullup resistor and does not

source or sink current as long as its input voltage

is between GND and V

OUT

. The input voltage

does not affect supply current.

WDO Logic high. The open circuit voltage is equal to

V

OUT

.

PFI The Power Fail Comparator is turned off and

has no effect on the Power Fail Output.

PFO Logic low.

CE

IN

CE

IN

is ignored. It is internally disconnected

from its internal pullup and does not source or

sink current as long as its input voltage is be-

tween GND and V

OUT

. The input voltage does

not affect supply current.

CE

OUT

Logic high. The open circuit voltage is equal to

V

OUT

.

OSC IN OSC IN is ignored.

OSC SEL OSC SEL is ignored.

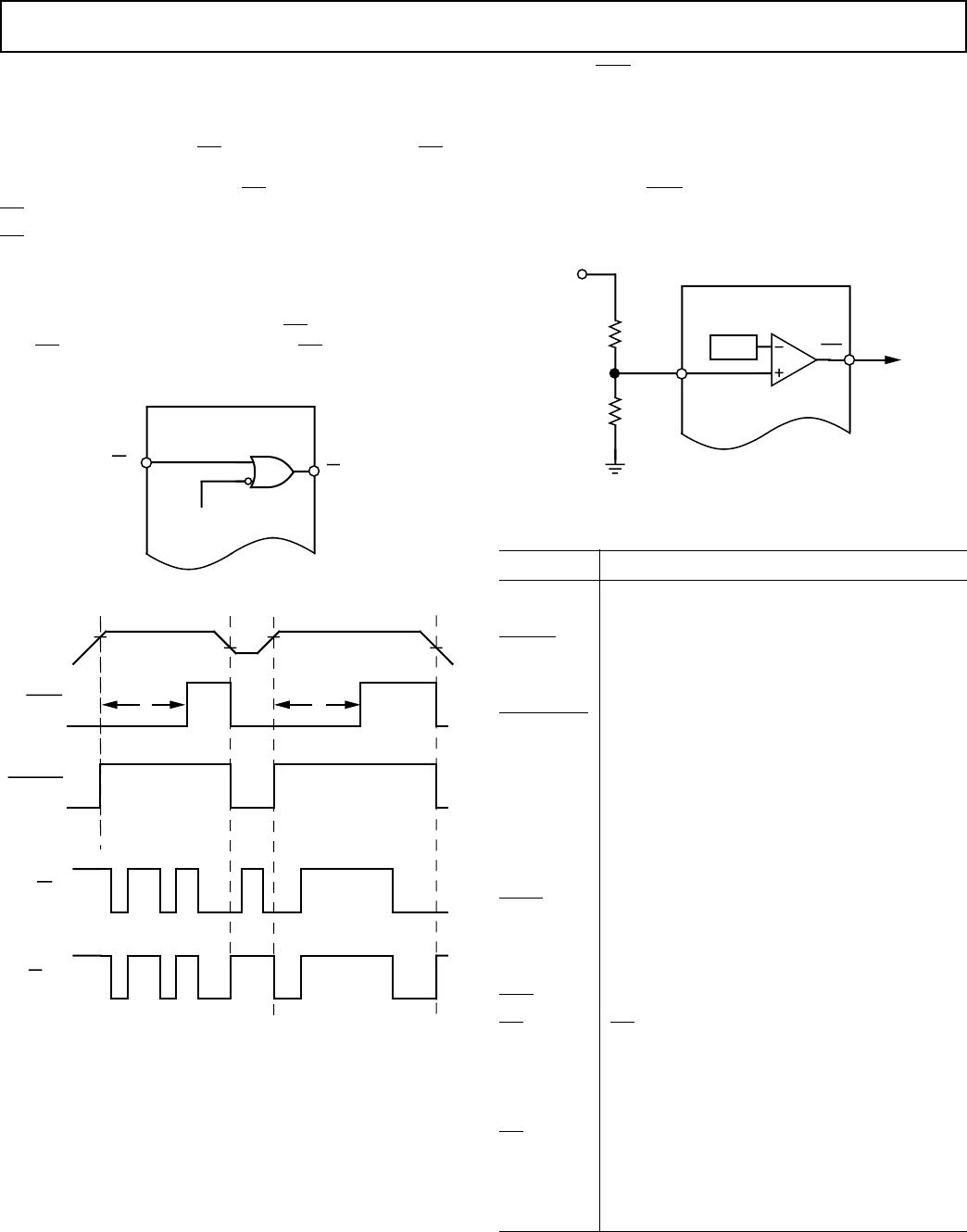

CE Gating and RAM Write Protection (ADM697)

The ADM697 contains memory protection circuitry which

ensures the integrity of data in memory by preventing write

operations when LL

IN

is below the threshold voltage. When

LL

IN

is greater than 1.3 V, CE

OUT

is a buffered replica of CE

IN

,

with a 5 ns propagation delay. When LL

IN

falls below the 1.3 V

threshold, an internal gate forces

CE

OUT

high, independent of

CE

IN

.

CE

OUT

typically drives the CE, CS, or Write input of battery

backed up CMOS RAM. This ensures the integrity of the data

in memory by preventing write operations when V

CC

is at an in-

valid level.

If the 5 ns typical propagation delay of

CE

OUT

is excessive, con-

nect

CE

IN

to GND and use the resulting CE

OUT

to control a

high speed external logic gate.

ADM697

CE

OUT

CE

IN

LL

IN

LOW = 0

LL

IN

OK = 1

Figure 5. Chip Enable Gating

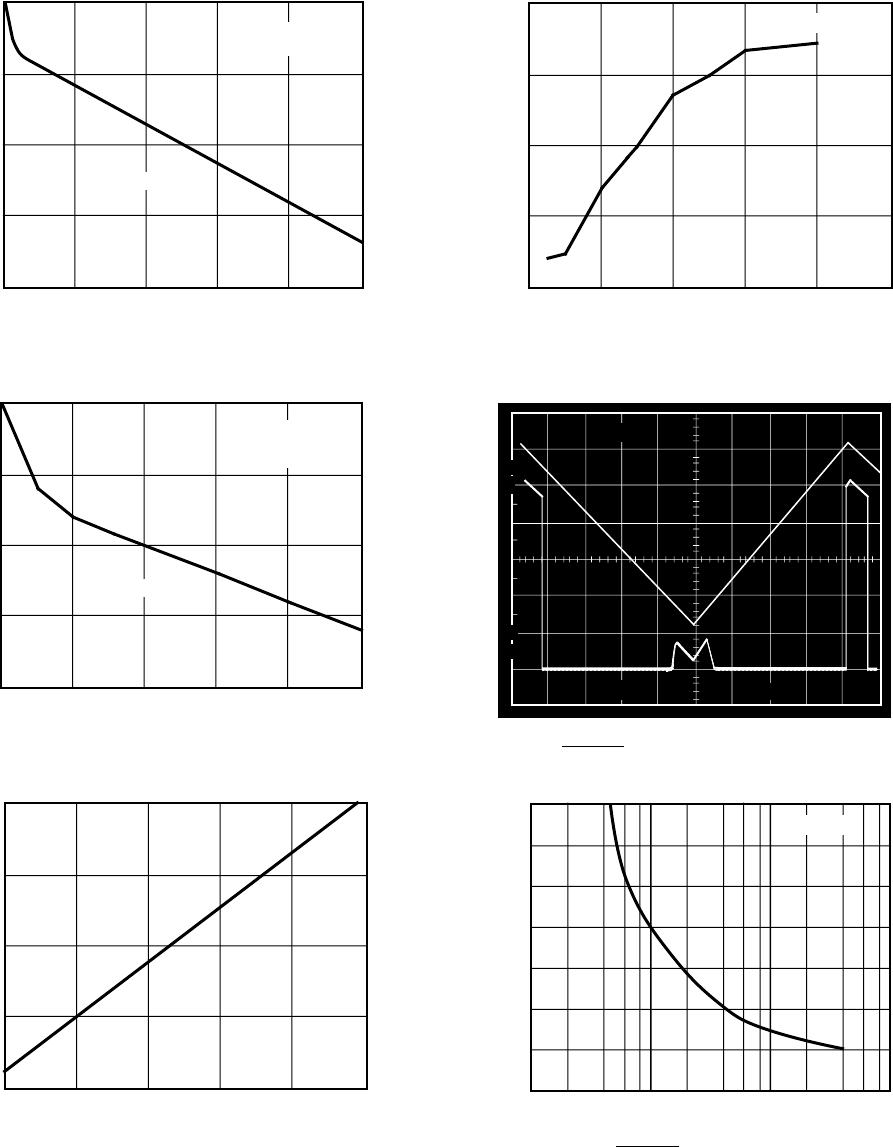

t

1

t

1

= RESET TIME

V1 = RESET VOLTAGE THRESHOLD LOW

V2 = RESET VOLTAGE THRESHOLD HIGH

HYSTERESIS = V2–V1

V2 V2

V1 V1

t

1

LL

IN

LOW LINE

RESET

CE

IN

CE

OUT

Figure 6. Chip Enable Timing

Power Fail Warning Comparator

An additional comparator is provided for early warning of fail-

ure in the microprocessor’s power supply. The Power Fail Input

(PFI) is compared to an internal +1.3 V reference. The Power