LT4275

8

4275f

applicaTions inForMaTion

The AUX pin allows for setting the auxiliary supply turn on

(V

AUXON

) and turn off (V

AUXOFF

) voltage thresholds. The

auxiliary supply hysteresis voltage (V

AUXHYS

) is set by

sinking current (I

AUXH

) only when the AUX pin voltage is

less than V

AUXT

. Use the following equations to set V

AUXON

and V

AUXOFF

via R1 and R2 in Figure 4.

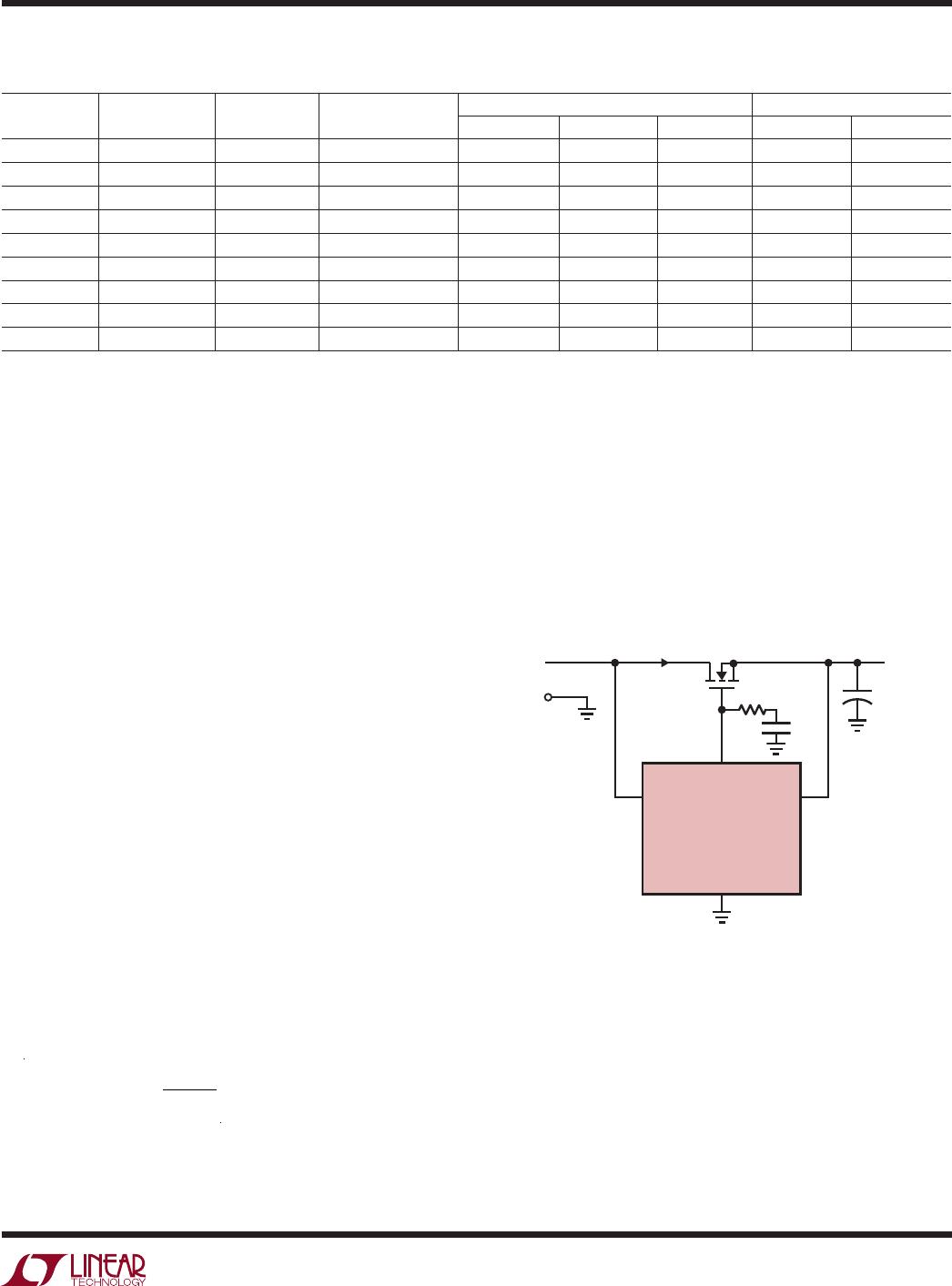

Figure 4. AUX Threshold and Hysteresis Calculation

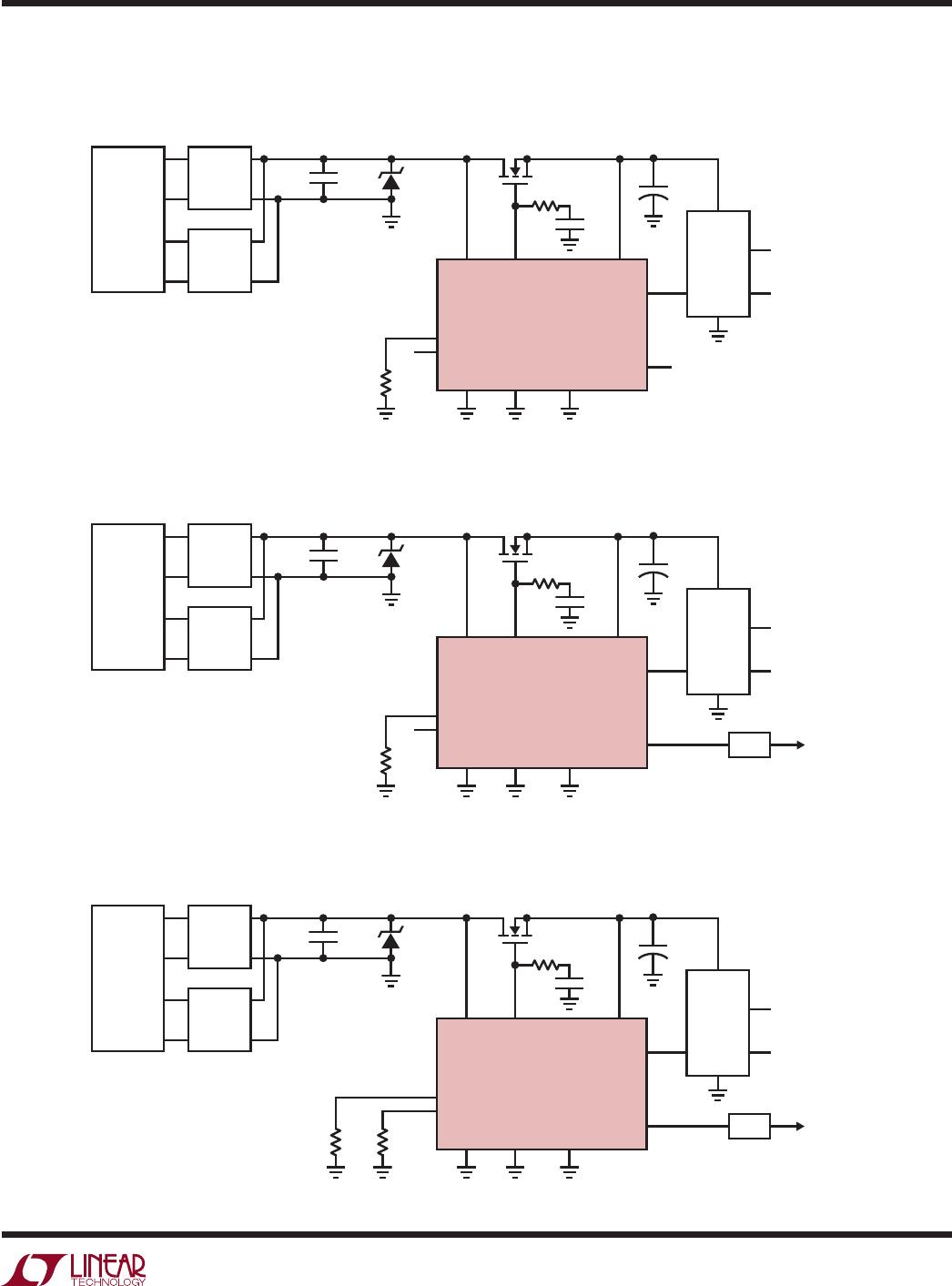

Transient Voltage Suppressor

The LT4275 specifies an absolute maximum voltage of

100V and is designed to tolerate brief overvoltage events.

However, the pins that interface to the outside world can

routinely see excessive peak voltages. To protect the

LT4275, install a unidirectional transient voltage suppres-

sor (TVS) such as an SMAJ58A between the port voltage

and GND. This TVS must be mounted near the LT4275.

For extremely high cable discharge and surge protection

contact Linear Technology Applications.

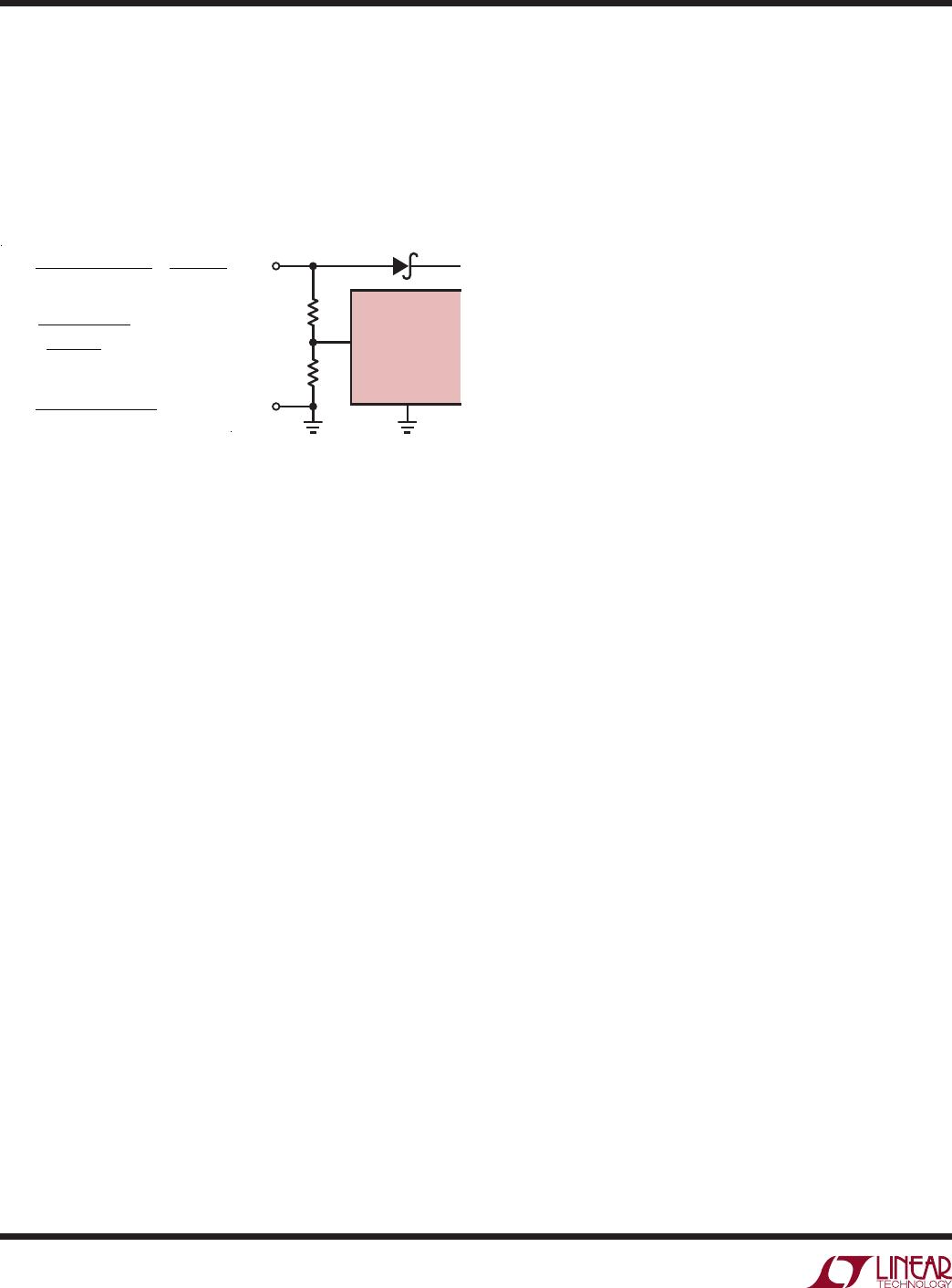

Classification Resistor (R

CLS

and R

CLS

++

)

The R

CLS

resistors set the classification load current cor-

responding to the PD power classification. Select the value

of R

CLS

from Table 1 and connect the resistor between the

RCLASS pin and GND, or float the RCLASS pin if class 0

is required. The resistor tolerance must be 1% or better to

avoid

degrading the overall accuracy of the classification

circuit. For LTPoE

++

use the LT4275A and select the value

of R

CLS

++

from Table 1 in addition to R

CLS

.

Power Good Interface

The LT4275 provides a power good signal (PWRGD) to

simplify the isolated power supply design. The power good

signal is used to delay isolated power supply startup until

the C

PORT

capacitor is fully charged.

Exposed Pad

The LT4275A/LT4275B/LT4275C DFN package has an

exposed pad that is internally electrically connected to

GND. The exposed pad may only be connected to GND

on the printed circuit board.

LAYOUT CONSIDERATIONS

Avoid excessive parasitic capacitance on the RCLASS

pin and place resistor R

CLS

close to the LT4275. For the

LT4275A, place R

CLS

++ nearby as well.

It is strictly required for maximum protection to place the

input capacitor (C

PD

) and transient voltage suppressor as

close to the LT4275 as possible.

LT4275A

GND

4275 F04

AUX

R1

V

AUX

+

–

R2

R1=

V

AUXON

− V

AUXOFF

I

AUXH

=

V

AUXHYS

I

AUXH

R2 =

R1

V

AUXOFF

V

AUXT

−1

R1≥

V

AUX(MAX)

− V

AUXT

1.4mA

THERMAL PROTECTION

The IEEE 802.3 specification requires a PD to withstand

any applied voltage from 0V to 57V indefinitely. During

classification, however, the power dissipation in the LT4275

may be as high as 1.5W. The LT4275 can easily tolerate

this power for the maximum IEEE timing but will overheat

if this condition persists abnormally.

The LT4275 includes a thermal protection feature which

protects itself from excessive heating. If the junction

temperature exceeds the overtemperature threshold, the

LT4275 pulls down the HSGATE and PWRGD pins and

disables classification.

EXTERNAL INTERFACE AND COMPONENT SELECTION

Input Diode Bridge

The input diode bridge introduces a voltage drop that affects

the voltage range for each mode of operation. The LT4275

is designed to tolerate these voltage drops. The voltages

shown in the Electrical Specifications are measured at the

LT4275 package pins.

Input Capacitor

A 0.1µF capacitor is needed from VPORT to GND to meet

an input impedance requirement in IEEE 802.3.