6.42

IDT70V05S/L

High-Speed 3.3V 8K x 8 Dual-Port Static RAM Industrial and Commercial Temperature Ranges

2

Description

The IDT70V05 is a high-speed 8K x 8 Dual-Port Static RAM. The

IDT70V05 is designed to be used as a stand-alone 64K-bit Dual-Port

SRAM or as a combination MASTER/SLAVE Dual-Port SRAM for 16-bit-

or-more word systems. Using the IDT MASTER/SLAVE Dual-Port SRAM

approach in 16-bit or wider memory system applications results in full-

speed, error-free operation without the need for additional discrete logic.

This device provides two independent ports with separate control,

address, and I/O pins that permit independent, asynchronous access for

reads or writes to any location in memory. An automatic power down

feature controlled by CE permits the on-chip circuitry of each port to enter

a very low standby power mode.

Fabricated using IDT’s CMOS high-performance technology, these

devices typically operate on only 400mW of power.

The IDT70V05 is packaged in a ceramic 68-pin PGA and PLCC

and a 64-pin thin quad flatpack (TQFP).

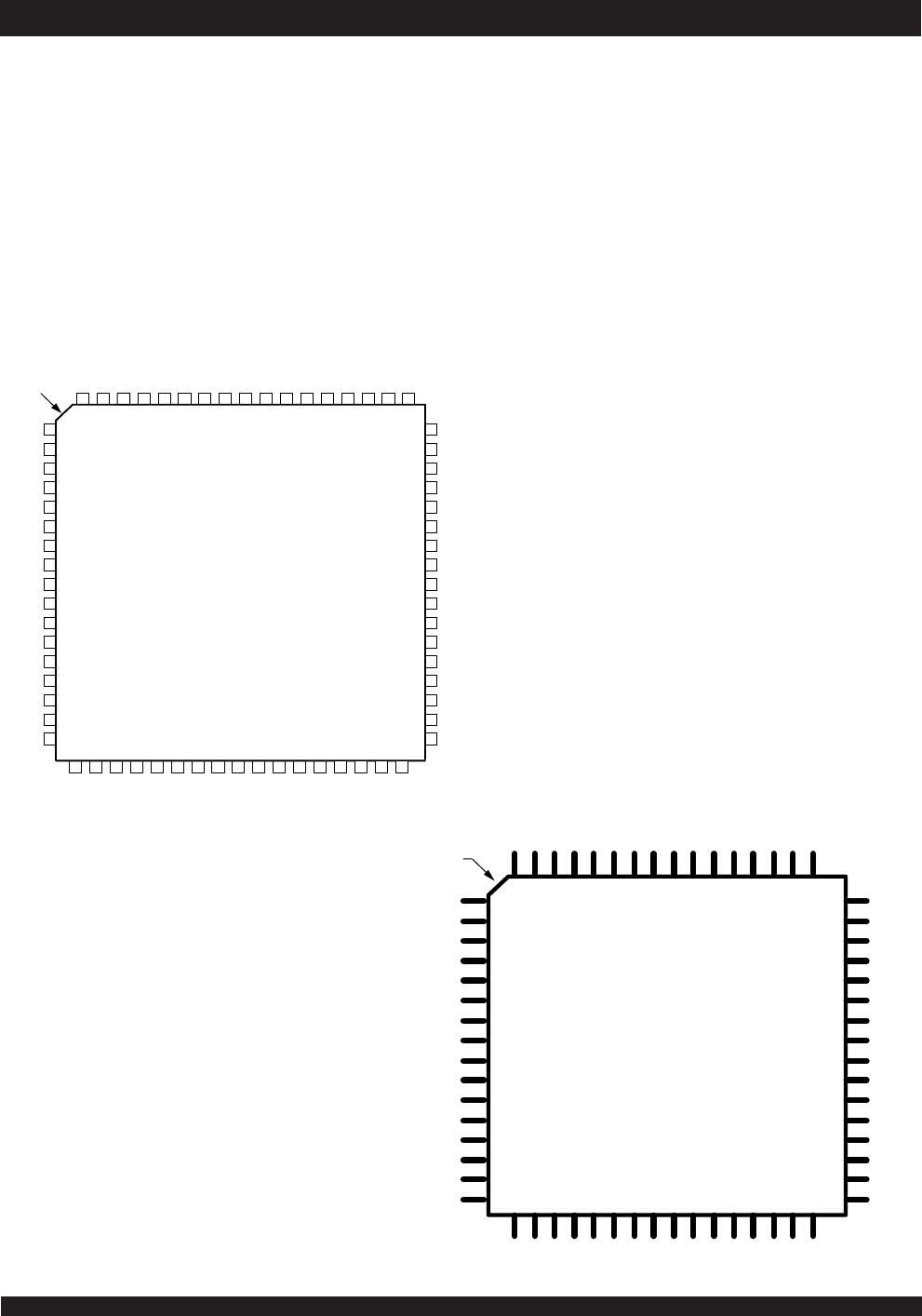

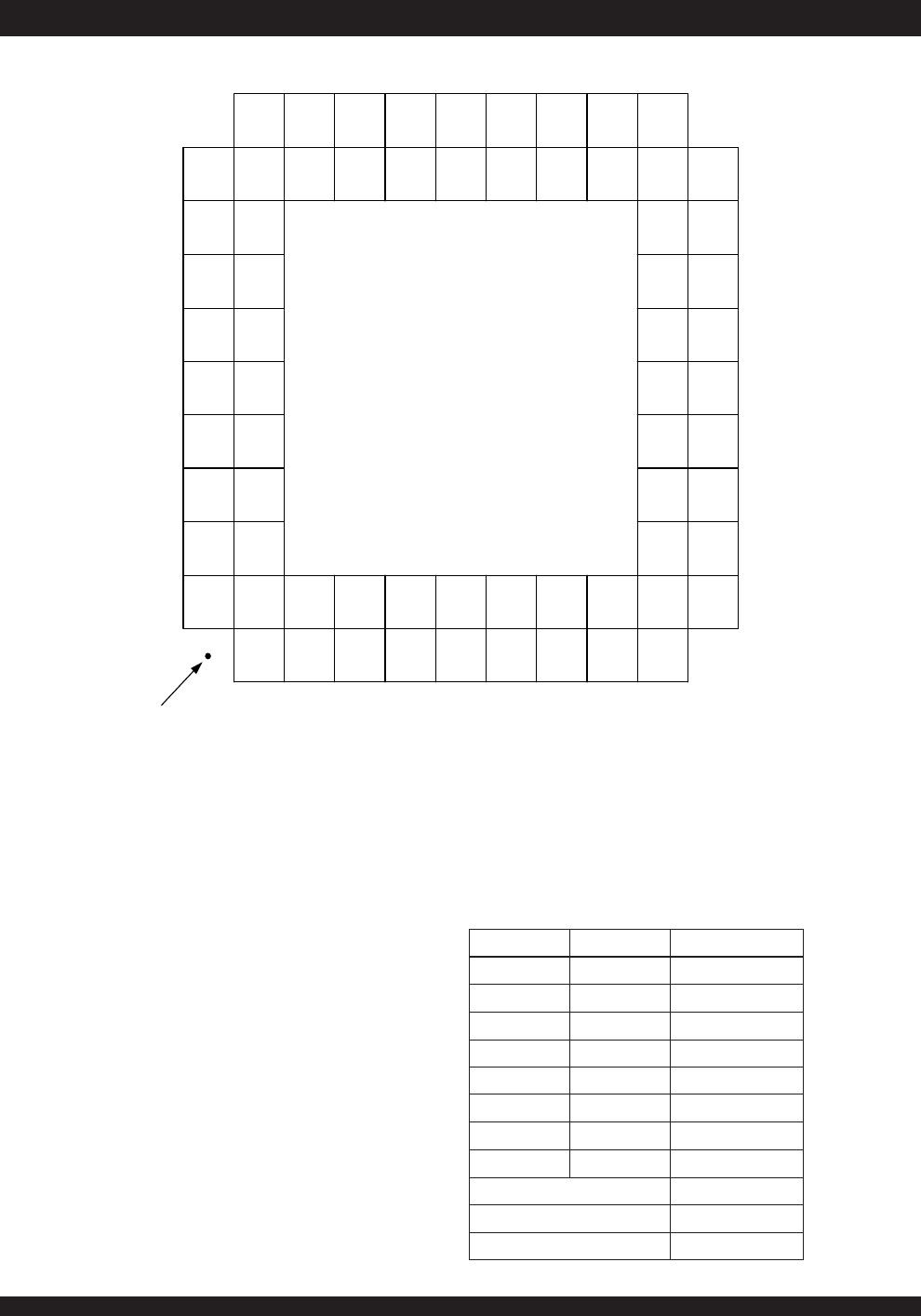

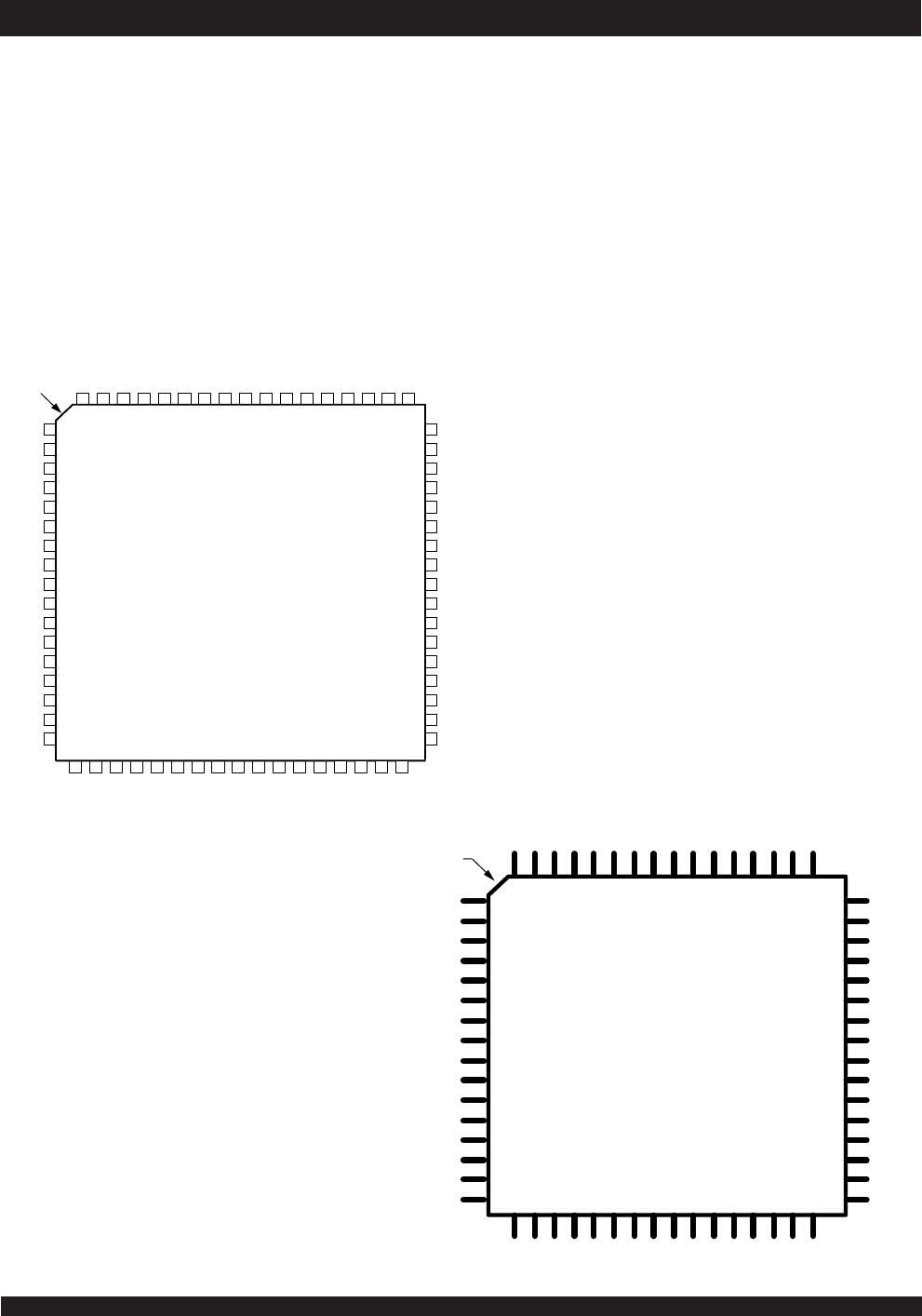

Pin Configurations

(1,2,3)

NOTES:

1. All V

CC pins must be connected to power supply.

2. All GND pins must be connected to ground supply.

3. J68-1 package body is approximately .95 in x .95 in x .17 in.

PN64 package body is approximately 14mm x 14mm x 1.4mm.

4. This package code is used to reference the package diagram.

5. This text does not indicate oriention of the actual part-marking

2941 drw 02

12

13

14

15

16

17

18

INDEX

19

20

21

22

987 6543 2168676665

27 28 29 30 31 32 33 34 35 36 37 38 39

V

D

D

V

DD

I/O

1R

I/O

2R

I/O

3R

I/O

4R

INT

L

V

SS

A

4L

A

3L

A

2L

A

1L

A

0L

A

3R

A

0R

A

1R

A

2R

I/O

2L

A

5L

R

/

W

L

11

10

M/S

23

24

25

26

40 41 42 43

58

57

56

55

54

53

52

51

50

49

48

59

60

47

46

45

44

64 63 62 61

I/O

3L

V

SS

I/O

0R

V

DD

A

4R

BUSY

L

V

SS

BUSY

R

INT

R

A

1

2

R

I

/

O

7

R

N

/

C

V

S

S

O

E

R

R

/

W

R

S

E

M

R

C

E

R

O

E

L

S

E

M

L

C

E

L

N

/

C

I

/

O

0

L

I

/

O

1

L

IDT70V05J

J68-1

(4)

68-Pin PLCC

Top View

(5)

I/O

4L

I/O

5L

I/O

6L

I/O

7L

I/O

5R

I/O

6R

N

/

C

A

1

2

L

A

1

1

R

N

/

C

A

1

0

R

A

9

R

A

8

R

A

7

R

A

6

R

A

5

R

A

1

1

L

A

1

0

L

A

9

L

A

8

L

A

7

L

A

6

L

N

/

C

N

/

C

,

12/03/01

INDEX

70V05PF

PN-64

(4)

64-Pin TQFP

Top View

(5)

8

9

10

11

12

13

14

15

16

1

2

3

4

5

6

7

46

45

44

43

42

41

40

39

38

37

36

35

34

47

48

33

1

7

1

8

1

9

2

0

3

2

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

4

9

5

0

5

1

5

2

6

3

6

2

6

1

6

0

5

9

5

8

5

7

5

6

5

5

5

4

5

3

6

4

I/O

2L

V

DD

V

SS

V

SS

A

4R

BUSY

L

BUSY

R

INT

R

INT

L

V

SS

M/S

O

E

L

A

5

L

I

/

O

1

L

R

/

W

L

C

E

L

S

E

M

L

V

D

D

N

/

C

N

/

C

O

E

R

C

E

R

R

/

W

R

S

E

M

R

A

1

2

R

G

N

D

I/O

3L

I/O

4L

I/O

5L

I/O

6L

I/O

7L

I/O

0R

I/O

1R

I/O

2R

V

DD

I/O

3R

I/O

4R

I/O

5R

I

/

O

6

R

I

/

O

7

R

A

1

1

R

A

1

0

R

A

9

R

A

8

R

A

7

R

A

6

R

A

5

R

A

3R

A

2R

A

1R

A

0R

A

0L

A

1L

A

2L

A

3L

A

4L

A

6

L

A

7

L

A

8

L

A

9

L

A

1

0

L

A

1

1

L

A

1

2

L

I

/

O

0

L

2941 drw 03

,

12/03/01