NB3N3010B

http://onsemi.com

5

APPLICATION INFORMATION

Figure 1 shows the simplified block diagram of the

NB3N3010B device.

The primary function of the NB3N3010B is to accept a

selectable 4 kHz or 8 kHz input reference clock, REF, and

then multiply it to 12.288 MHz output frequency.

Frequency Select − SO

Either of two expected input REF frequencies, 4 kHz or

8 kHz, will be multiplied by the FLL to achieve 12.288 MHz

at the low−skew CLKA and CLKB outputs by selecting the

S0 pin; see Table 6.

The pulse high time (T

HI

) of the input reference signal may

vary widely depending on the application. See AC

specifications for details.

Output Enable − ENABLEn

A Low active output enable input pin, ENABLEn, is

provided. When the ENABLEn input is High inactive, both

clock outputs are driven to a logic Low.

The NB3N3010B implements a delay, specified as

ENABLEn to Output Delay in the AC Specifications, from

the assertion of ENABLEn to the first rising edges on the

clock outputs. This delay insures that CLKA and CLKB

output pulses are within specification before the output

drivers are enabled. When ENABLEn transitions from Low

to High (de−asserts), the current cycle of the clock outputs

completes normally then the outputs will be held Low. The

ENABLEn signal is asynchronous to either the REF input or

CLK_x outputs.

Table 6. INPUT FREQUENCY SELECT AND OUTPUT ENABLE FUNCTIONS

ENABLEn* S0* f

REF

FLL Multiplier CLKA & CLKB Frequency

0 L 4 kHz 3072 12.288 MHz

0 H 8 kHz 1536 12.288 MHz

1 x x x Disabled Low

*Defaults High when left open.

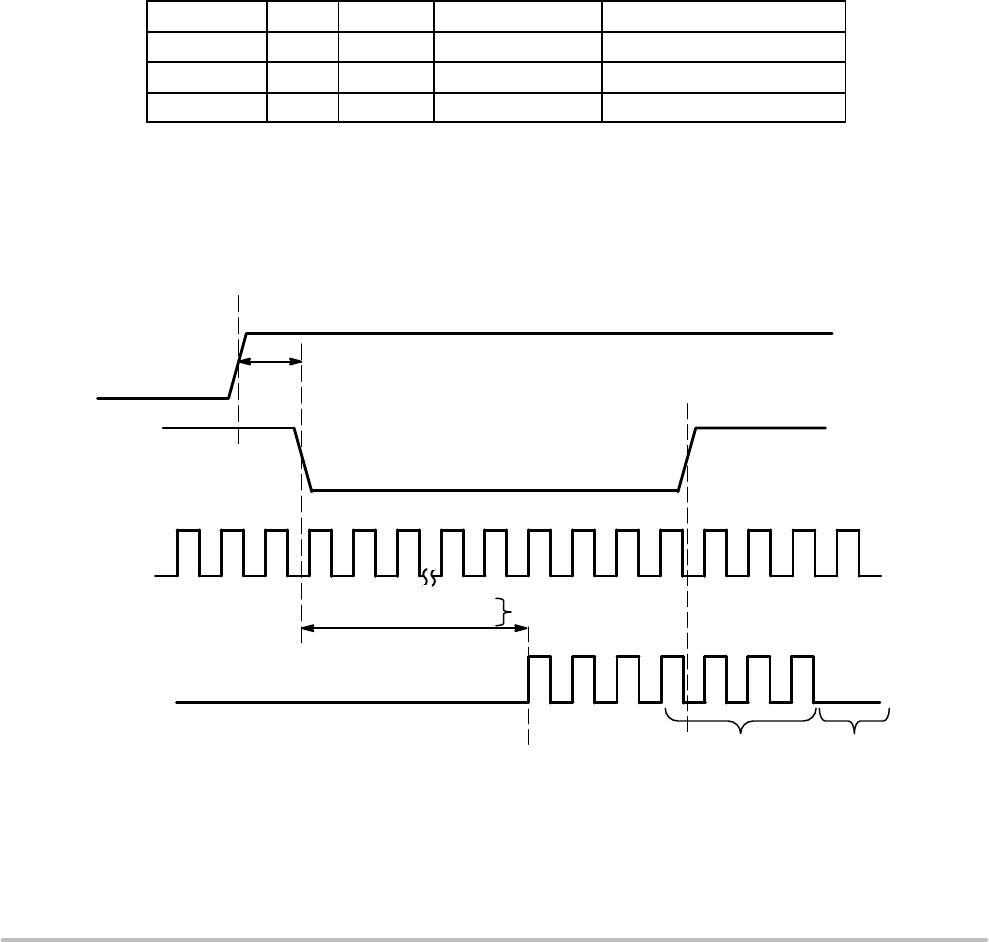

Typical Power On Sequence

1. Power On

2. Reference Clock present; must be switching before ENABLEn goes High.

3. Output Enable, ENABLEn, High−to−Low

Figure 3. ENABLEn Timing Diagram

V

DD

Valid to ENABLEn

~50 ms, typ

ENABLEn to Output

400 Clock Cycles @ 8 kHz

200 Clock Cycles @ 4 kHz

V

DD

Valid

V

DD

ENABLEn

REF

CLKA/B

Completed Clock

Outputs

Then Low

4 kHz or

8 kHz

12.288 MHz

Outputs Enabled