LTC1164-5

9

11645fc

Figure 3. Buffer for Filter Output

PI FU CTIO S

UUU

Butterworth/Bessel (Pin 10)

The DC level at Pin 10 determines the ratio of the clock

frequency to the cutoff frequency of the filter. Pin 10 at V

+

gives a 50:1 ratio and a Butterworth response (pins 1 to 13

are shorted for 50:1 only). Pin 10 at V

–

gives a 100:1

Butterworth response. Pin 10 at ground gives a Bessel

response and a ratio of 140:1. For single supply operation

the ratio is 50:1 when Pin 10 is at V

+

(Pins 1 to 13 shorted),

100:1 when Pin 10 is at ground, and 140:1 when at 1/2

supply. When Pin 10 is not tied to ground, it should be

bypassed to analog ground with a 0.1µF capacitor. If the

DC level at Pin 10 is switched mechanically or electrically

at slew rates greater than 1V/µs while the device is

operating, a 10k resistor should be connected between

Pin 10 and the DC source.

Filter Input (Pin 2)

The input pin is connected internally through a 100k

resistor tied to the inverting input of an op amp.

Filter Output (Pins 9, 6)

Pin 9 is the specified output of the filter; it can typically

source or sink 1mA. Driving coaxial cables or resistive

loads less than 20k will degrade the total harmonic distor-

tion of the filter. When evaluating the device’s distortion an

output buffer is required. A noninverting buffer, Figure 3,

can be used provided that its input common mode range

is well within the filter’s output swing. Pin 6 is an interme-

diate filter output providing an unspecified 6th order

lowpass filter. Pin 6 should not be loaded.

External Connection (Pins 7, 14 and 1, 13)

Pins 7 and 14 should be connected together. In a printed

circuit board the connection should be done under the IC

package through a short trace surrounded by the analog

ground plane. When the clock to cutoff frequency ratio is

set at 50:1, Pin 1 should be shorted to Pin 13; if not, the

passband will exhibit 1dB of gain peaking and it will deviate

from a Butterworth response. Pin 1 is the inverting input

of an internal op amp and it should preferably be 0.2 inches

away from any other circuit trace.

NC (Pin 8)

Pin 8 is not connected to any internal circuit point on the

device and should be preferably tied to analog ground.

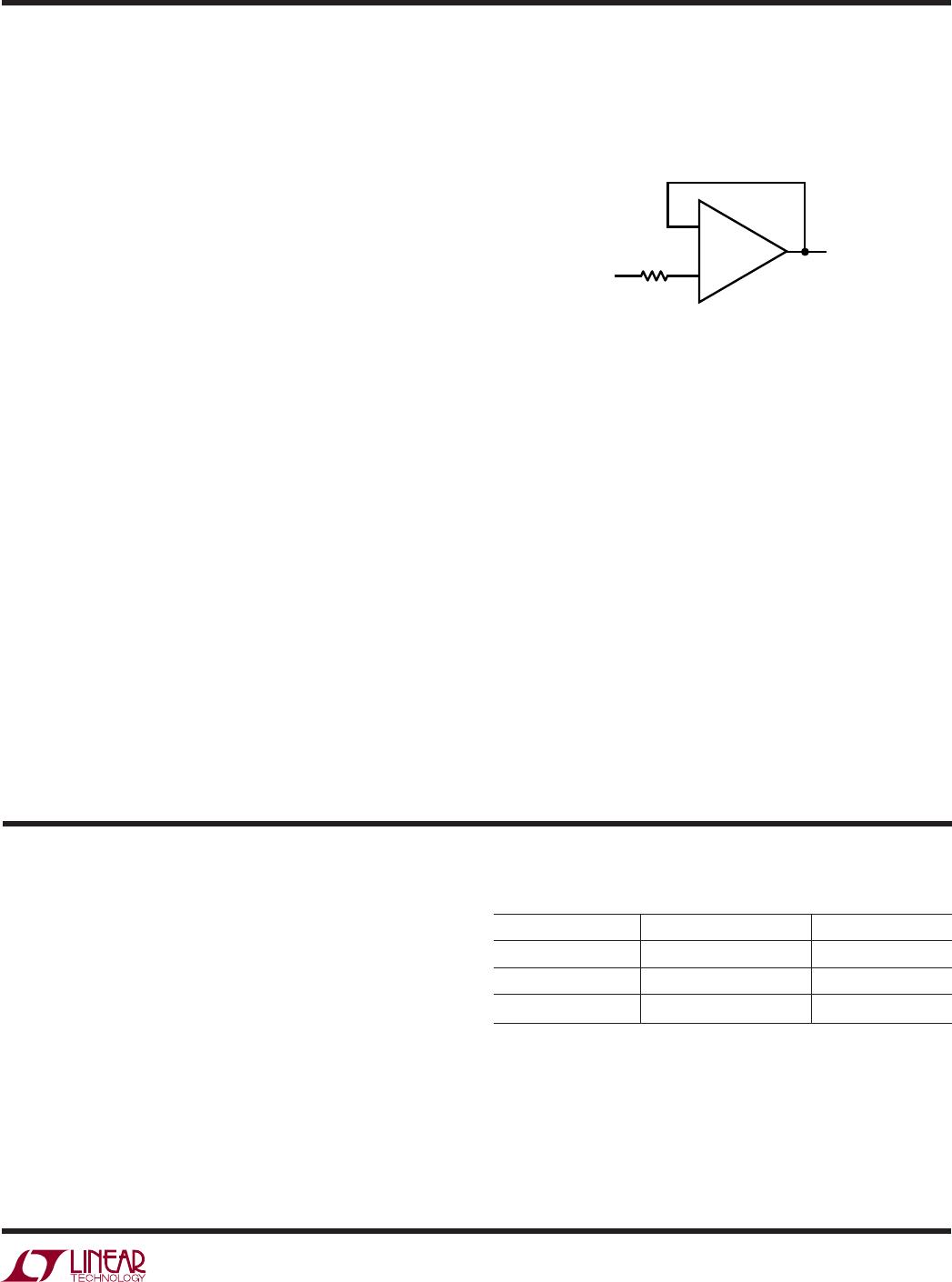

Table 2. Output Clock Feedthrough

V

S

50:1 100:1

±2.5V 60µV

RMS

60µV

RMS

±5V 100µV

RMS

200µV

RMS

±7.5V 150µV

RMS

500µV

RMS

Note: The clock feedthrough at ±2.5V supplies is imbedded in the

wideband noise of the filter. The clock waveform is a square wave.

APPLICATIO S I FOR ATIO

WUU

U

Clock Feedthrough

Clock feedthrough is defined as, the RMS value of the

clock frequency and its harmonics that are present at the

filter’s output pin (Pin 9). The clock feedthrough is tested

with the input pin (Pin 2) grounded and, it depends on PC

board layout and on the value of the power supplies. With

proper layout techniques the values of the clock feedthrough

are shown in Table 2.