IDT8N4DV75 Data Sheet LVDS DUAL-FREQUENCY PROGRAMMABLE VCXO

IDT8N4DV85CCD

REVISION B NOVEMBER 20, 2013 7 ©2013 Integrated Device Technology, Inc.

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is

mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium

has been reached under these conditions.

NOTE 1. V

C

= 0V to V

CC.

Oscillator gain is programmed by IDT. Gain = (25 * N) ÷ V

CC

and is in the range of n = 1 to n = 63.

NOTE 2. Nominal oscillator gain: Refer to the programming guide for optimal pull range and control voltage tuning

NOTE 3. For best phase noise performance, use the lowest K

V

that meets the requirements of the application.

NOTE 4. BSL = Best Straight Line Fit: Variation of the output frequency vs. control voltage V

C

in percent. V

C

ranges from 10% to 90% V

CC

.

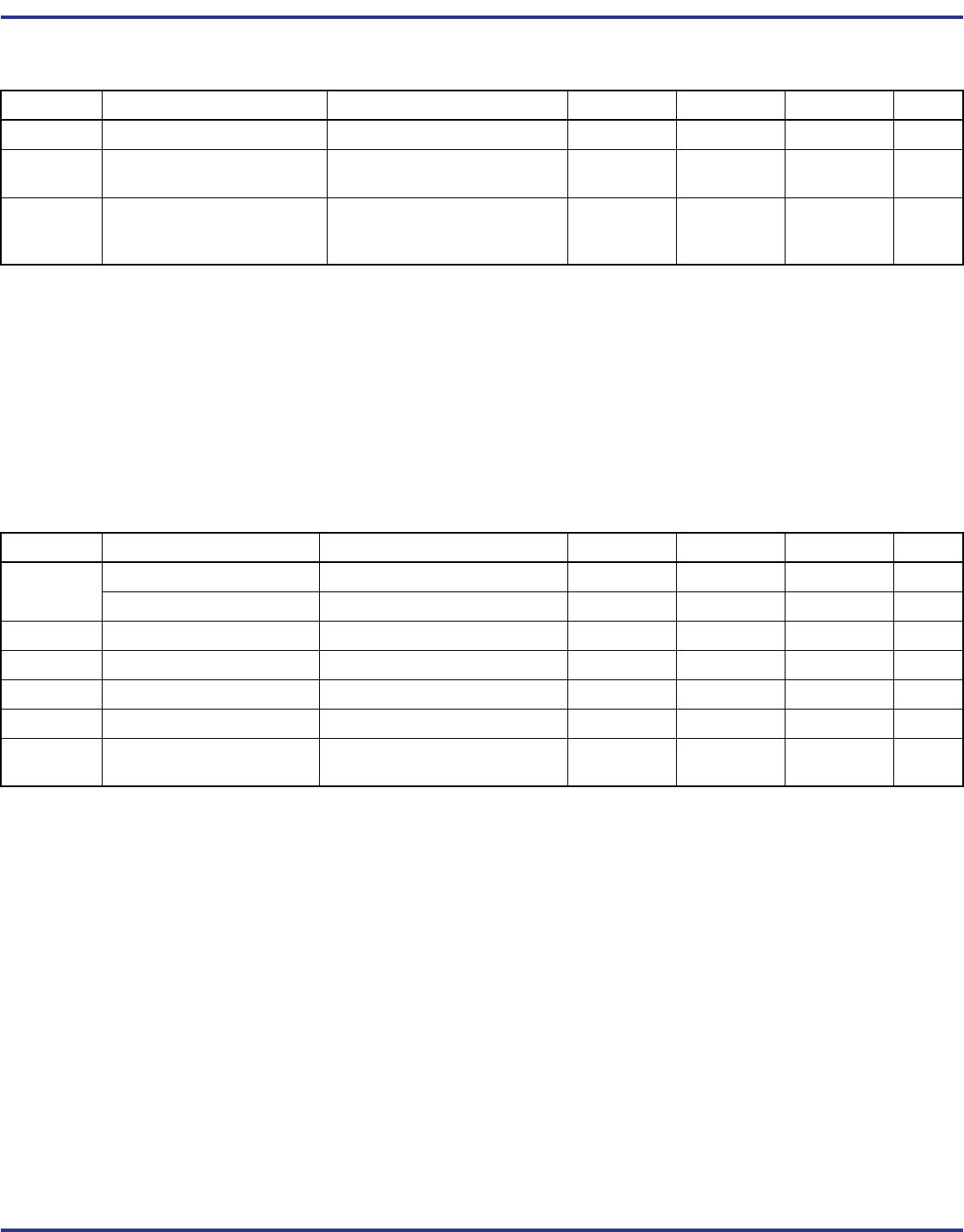

odc Output Duty Cycle 45 55 %

t

OSC

Device startup time after

power-up

15 ms

t

SET

Output frequency settling time

after FSEL0 and FSEL1 values

are changed

1 ms

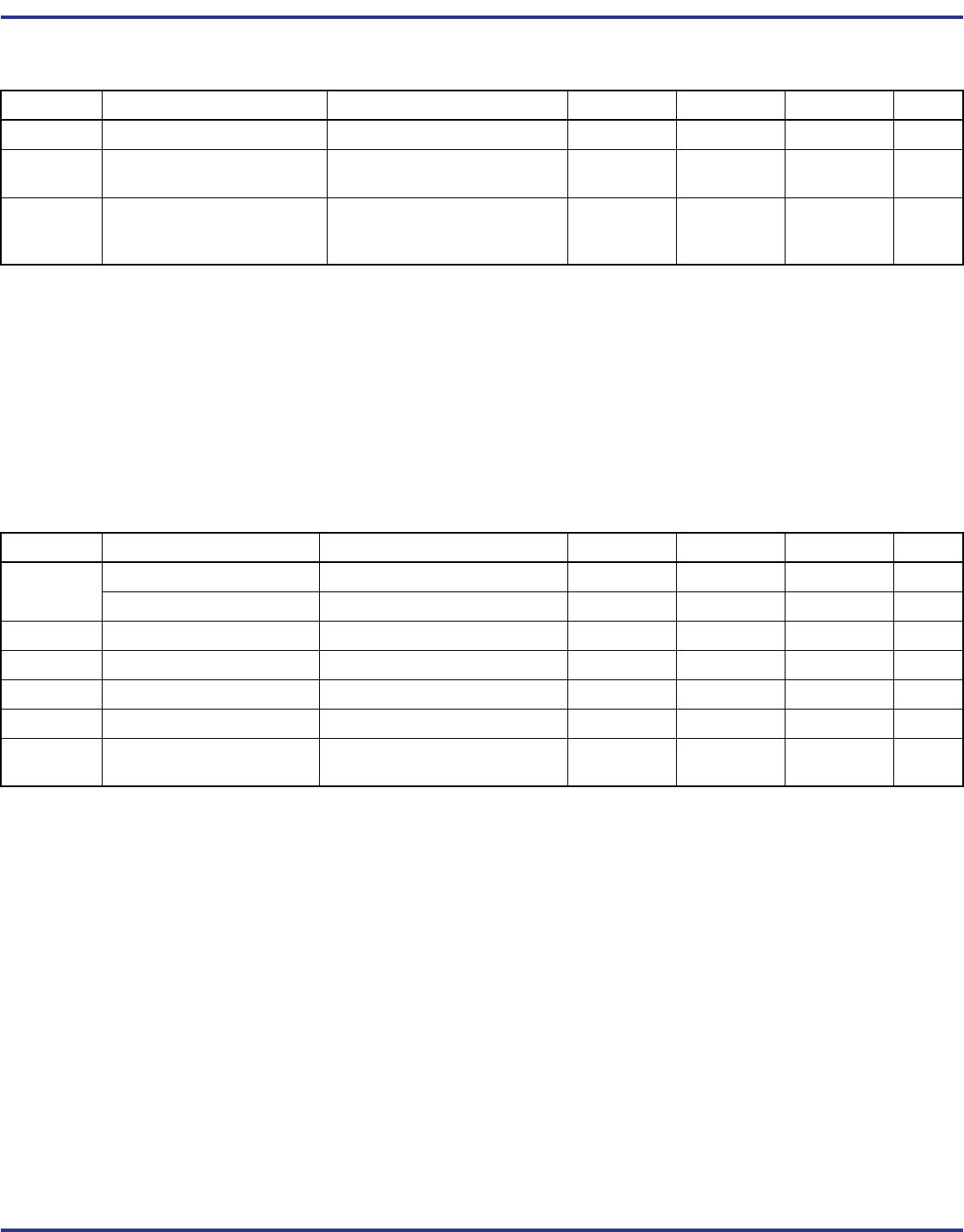

Table 5B. VCXO Control Voltage Input (V

C

) Characteristics, V

CC

=

3.3V ± 5% or V

CC

=

2.5V ± 5%, T

A

= -40°C to 85°C

Test Conditions Minimum Typical Maximum Units

K

V

Oscillator Gain; NOTE 1, 2, 3 V

CC

= 3.3V 7.57 477.27 ppm/V

Oscillator Gain NOTE 1, 2, 3 V

CC

= 2.5V 10 630 ppm/V

L

VC

Control Voltage Linearity BSL Variation -1 ±0.1 +1 %

BW Modulation Bandwidth 100 kHz

Z

VC

VC Input Impedance 500 k

VC

NOM

Nominal Control Voltage V

CC

/2 V

V

C

Control Voltage Tuning

Range; NOTE 4

0 V

CC

V

NOTE 1.This parameter is defined in accordance with JEDEC standard 65.

NOTE 2. Refer to the phase noise plot.

NOTE 3. Refer to the FemtoClock NG Ceramic 5 x 7 Modules Programming Guide for additional information on PLL feedback modes and the

optimum configuration for phase noise.

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is

mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium

has been reached under these conditions.

NOTE: Characterized with V

C

= V

CC

/2.

NOTE: XTAL parameters (initial accuracy, temperature stability, aging and total stability) are guaranteed by manufacturing.

Symbol Parameter

Table 5A. AC Characteristics, V

CC

=

3.3V ± 5% or V

CC

=

2.5V ± 5%, T

A

= -40°C to 85°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units