3-CHANNEL HIGH-PERFORMANCE TCXO/LVCMOS CLOCK BUFFER FAMILY 4 FEBRUARY 28, 2018

5PB12xx DATASHEET

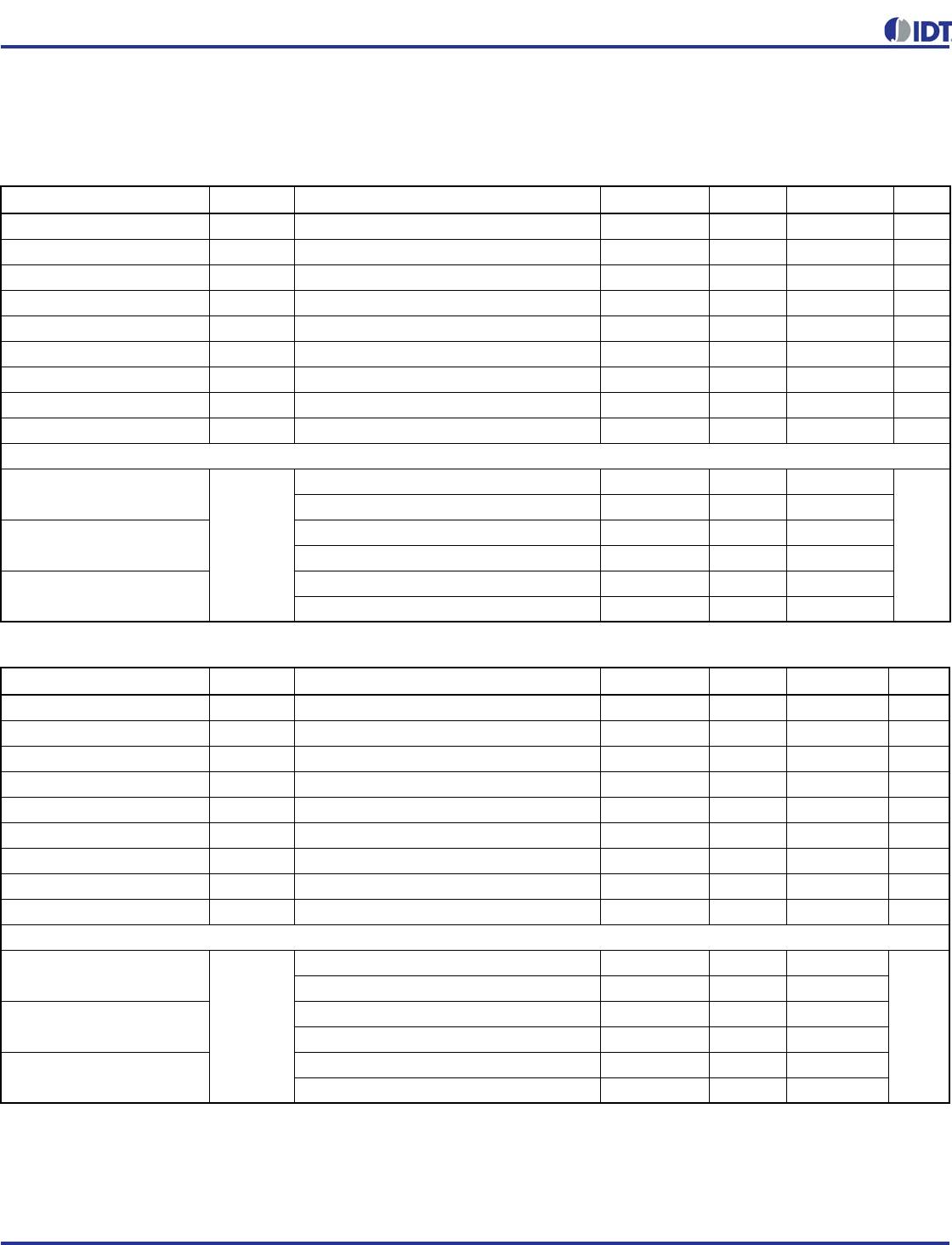

DC Electrical Characteristics

(VDD = 1.8V, 2.5V, 3.3V)

VDD = 1.8V ±5%, for 5PB1203 / 1204 / 1206, ambient temperature -40° to +105°C, unless stated otherwise.

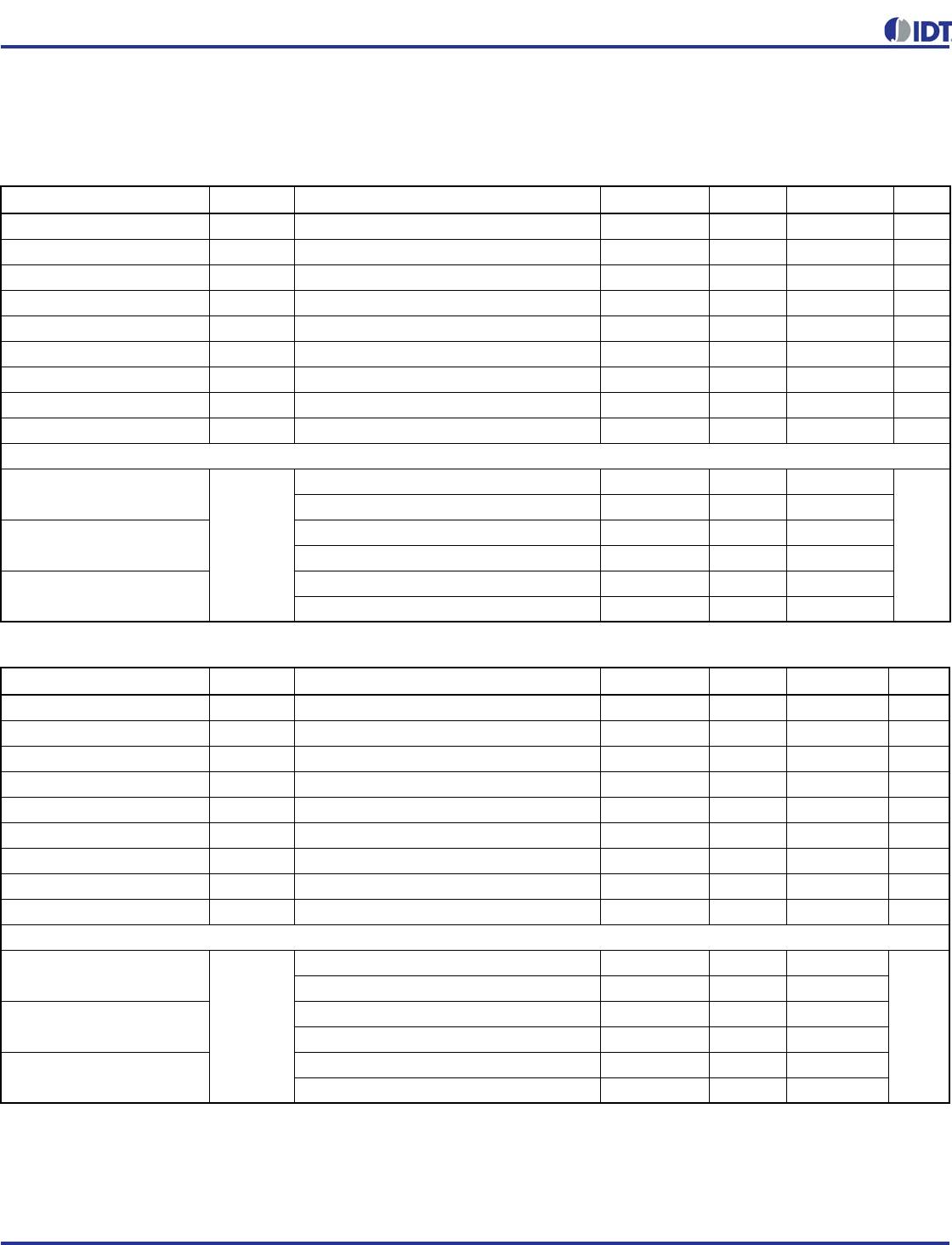

VDD = 2.5V ±5%, for 5PB1213 / 1214 / 1216, ambient temperature -40° to +105°C, unless stated otherwise.

Parameter Symbol Conditions Min. Typ. Max. Units

Operating Voltage VDD 1.71 1.89 V

Input High Voltage, CLKIN V

IH

LVCMOS input. Note 1 VDD/2 + 200 VDD mV

Input Low Voltage, CLKIN V

IL

LVCMOS input. Note 1 VDD/2 - 200 mV

Input High Voltage, OE V

IH

0.7xVDD VDD V

Input Low Voltage, OE V

IL

0.3xVDD V

Output High Voltage V

OH

I

OH

= -4mA 0.8xVDD V

Output Low Voltage V

OL

I

OL

= 4mA 0.2xVDD V

Nominal Output Impedance Z

O

17

Input Capacitance C

IN

5pF

Operating Supply Current

5PB1203

IDD

CLKIN = 26MHz, all outputs enabled 5.10

mA

CLKIN = Low or High, all outputs disabled 0.02 0.03

5PB1204

CLKIN = 26MHz, all outputs enabled 9.30

CLKIN = Low or High, all outputs disabled 2.51 4

5PB1206

CLKIN = 26MHz, all outputs enabled 11.90

CLKIN = Low or High, all outputs disabled 2.5 4

Parameter Symbol Conditions Min. Typ. Max. Units

Operating Voltage VDD 2.375 2.625 V

Input High Voltage, CLKIN V

IH

LVCMOS input. Note 1 VDD/2 + 200 VDD mV

Input Low Voltage, CLKIN V

IL

LVCMOS input. Note 1 VDD/2 - 200 mV

Input High Voltage, OE V

IH

0.7xVDD VDD V

Input Low Voltage, OE V

IL

0.3xVDD V

Output High Voltage V

OH

I

OH

= -4mA 0.8xVDD V

Output Low Voltage V

OL

I

OL

= 4mA 0.2xVDD V

Nominal Output Impedance Z

O

17

Input Capacitance C

IN

ICLK, OE pin 5 pF

Operating Supply Current

5PB1213

IDD

CLKIN = 26MHz, all outputs enabled 6.68

mA

CLKIN = Low or High, all outputs disabled 0.05 0.5

5PB1214

CLKIN = 26MHz, all outputs enabled 10.2

CLKIN = Low or High, all outputs disabled 3.47 5

5PB1216

CLKIN = 26MHz, all outputs enabled 16.5

CLKIN = Low or High, all outputs disabled 3.50 5