LTC2904/LTC2905

11

29045fd

In any supervisory application, supply noise riding on

the monitored DC voltage can cause spurious resets,

particularly when the monitored voltage is near the reset

threshold. A less desirable but common solution to this

problem is to introduce hysteresis around the nominal

threshold. Notice however, this hysteresis introduces an

error term in the threshold accuracy. Therefore, a ±2.5%

accurate monitor with ±1.0% hysteresis is equivalent to

a ±3.5% monitor with no hysteresis.

The LTC2904/LTC2905 takes a different approach to solve

this problem of supply noise causing spurious reset. The

fi rst line of defense against this spurious reset is a fi rst

order low pass fi lter at the output of the comparator. Thus,

the comparator output goes through a form of integration

before triggering the output logic. Therefore, any kind of

transient at the input of the comparator needs to be of

suffi cient magnitude and duration before it can trigger a

change in the output logic.

The second line of defense is the programmed delay time

tRST (200ms for LTC2904 and using an external capacitor

for LTC2905). This delay will eliminate the effect of any

supply noise whose frequency is above 1/t

RST

on the RST

and RST output.

When either V1 or V2 drops below its programmed thresh-

old, the RST pin asserts low (RST weakly pulls high). Then

when the supply recovers above the programmed thresh-

old, the reset-pulse-generator timer starts counting.

If the supply remains above the programmed threshold

when the timer fi nishes counting, the RST pin weakly

pulls high (RST asserts low). However, if the supply falls

below the programmed threshold any time during the

period when the timer is still counting, the timer resets

and it starts fresh when the supply next rises above the

programmed threshold.

Note that this second line of defense is only effective

for a rising supply and does not affect the sensitivity of

the system to a falling supply. Therefore, the fi rst line of

defense that works for both cases of rising and falling is

necessary. These two approaches prevent spurious reset

caused by supply noise without sacrifi cing the threshold

accuracy.

APPLICATIONS INFORMATION

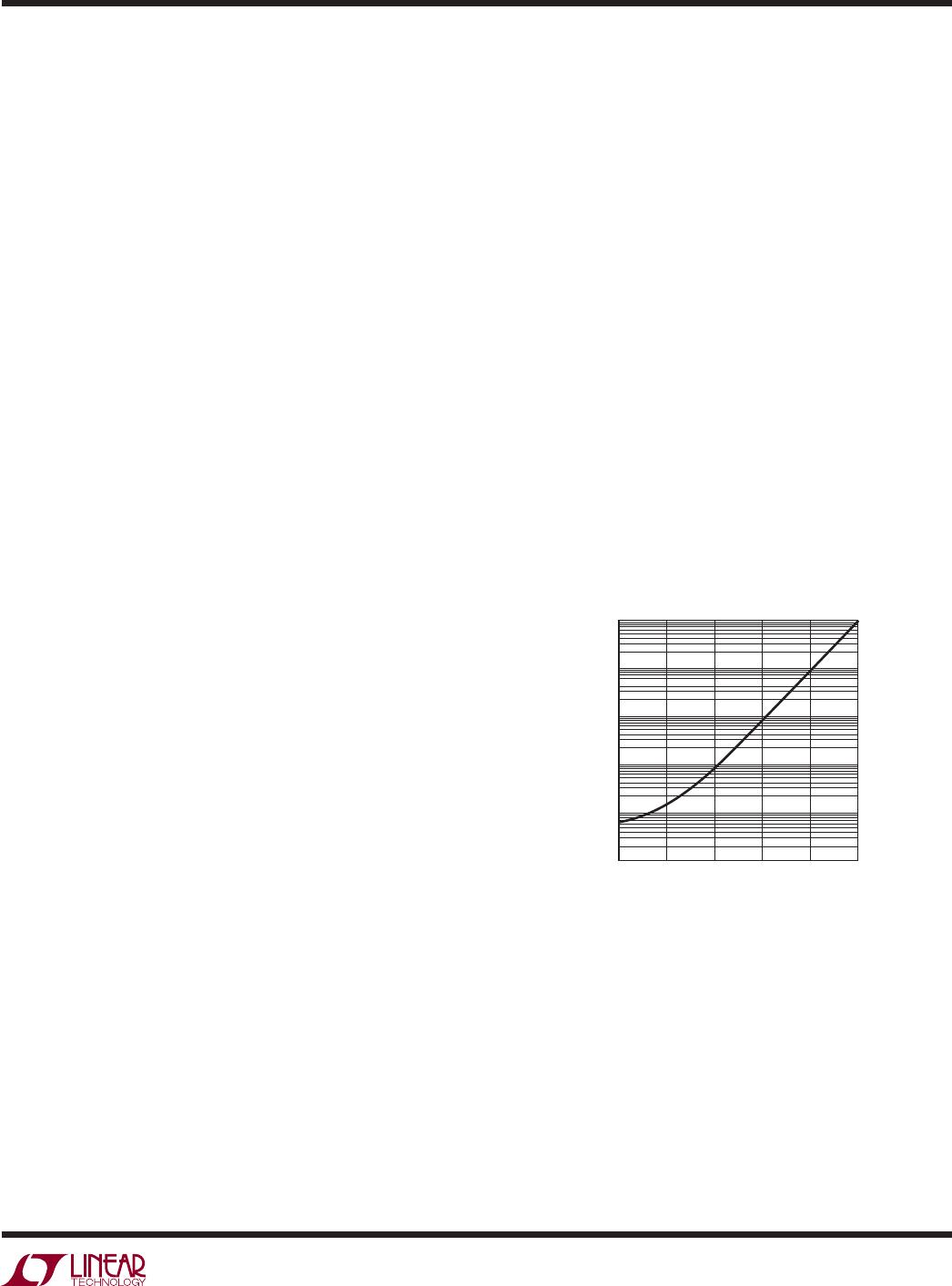

Selecting the Reset Timing Capacitor

The reset timeout period for LTC2905 is adjustable in order

to accommodate a variety of microprocessor applications.

Connecting a capacitor, C

TMR

, between the TMR pin and

ground sets the reset timeout period, t

RST

. The following

formula determines the value of capacitor needed for a

particular reset timeout period:

C

TMR

= t

RST

• 110 • 10

–9

[F/s]

For example, using a standard capacitor value of 22nF

would give a 22000/110 = 200ms delay.

Figure 1 shows the desired delay time as a function of the

value of the timer capacitor that should be used:

Leaving the TMR pin open with no external capacitor gen-

erates a reset timeout of approximately 200μs. For long

reset timeout, the only limitation is the availability of large

value capacitor with low leakage. The TMR capacitor will

never charge if the leakage current exceeds the minimum

TMR charging current of 2.1μA (typical).

Figure 1. Reset Timeout Period vs Capacitance

C

TMR

(FARAD)

10p 100p 1n 10n 100n 1μ

RESET TIME OUT PERIOD, t

RST

(ms)

29045 F01

10000

1000

100

10

1

0.1