11

IPM Dead Time and Propagation Delay Speci cations

The ACPL-P456/W456 includes a Propagation Delay

Di erence speci cation intended to help designers

minimize “dead time” in their power inverter designs.

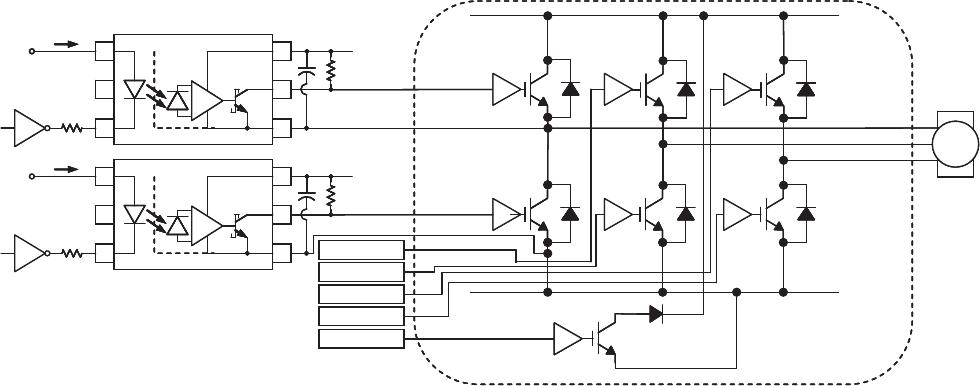

Dead time is the time period during which both the high

and low side power transistors (Q1 and Q2 in Figure 21)

are o . Any overlap in Q1 and Q2 conduction will result

in large currents owing through the power devices

between the high and low voltage motor rails.

To minimize dead time the designer must consider

the propagation delay characteristics of the optocou-

pler as well as the characteristics of the IPM IGBT gate

drive circuit. Considering only the delay characteristics

of the optocoupler (the characteristics of the IPM IGBT

gate drive circuit can be analyzed in the same way) it is

important to know the minimum and maximum turn on

(t

PHL

) and turn-o (t

PLH

) propagation delay speci cations,

preferably over the desired operating temperature range.

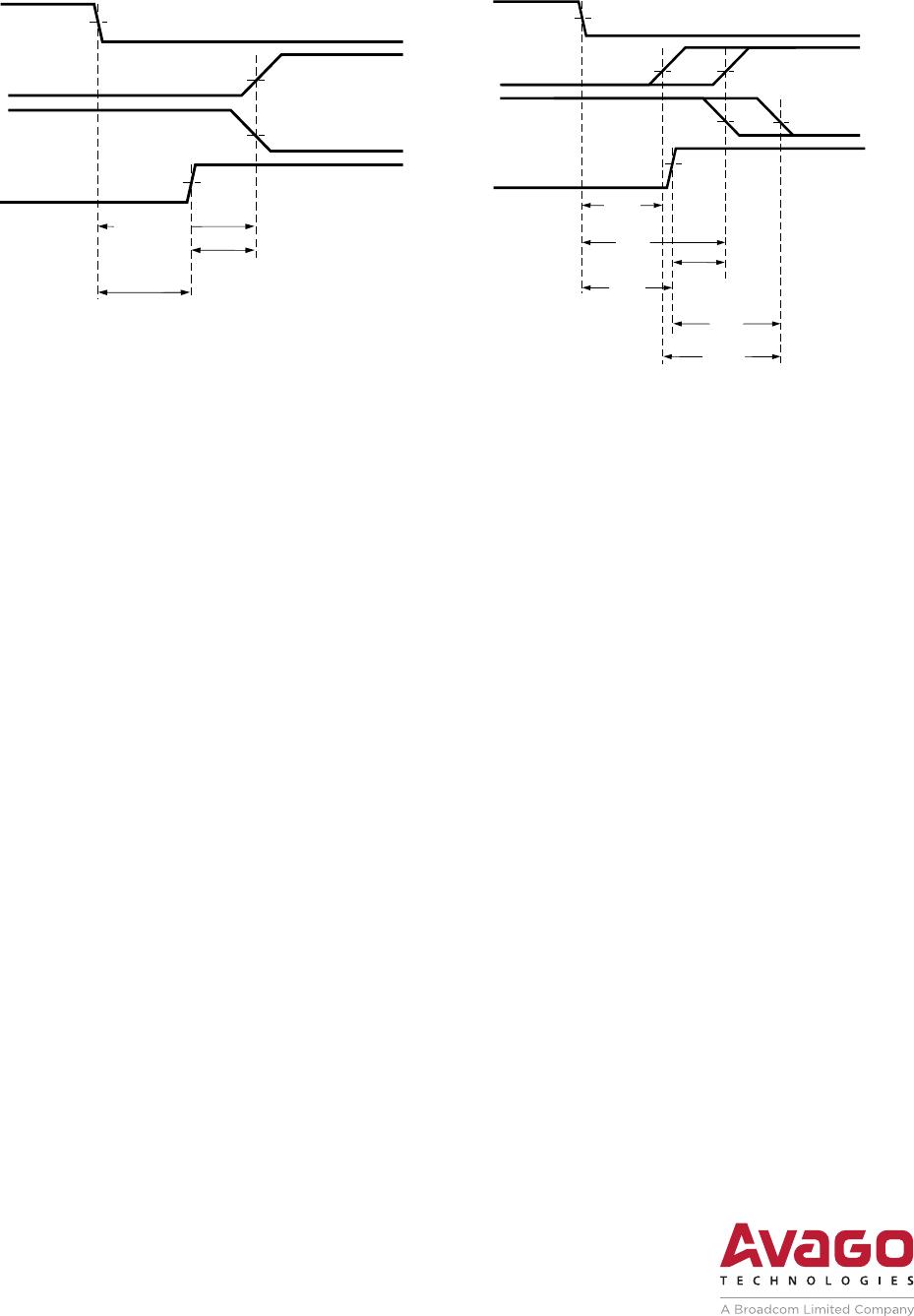

The limiting case of zero dead time occurs when the input

to Q1 turns o at the same time that the input to Q2 turns

on. This case determines the minimum delay between

LED1 turn-o and LED2 turn-on, which is related to the

worst case optocoupler propagation delay waveforms,

as shown in Figure 22. A minimum dead time of zero is

achieved in Figure 22 when the signal to turn on LED2

is delayed by (t

PLH

max - t

PHL

min) from the LED1 turn

Figure 21. Typical Application Circuit.

o . Note that the propagation delays used to calculate

PDD are taken at equal temperatures since the optocou-

plers under consideration are typically mounted in close

proximity to each other. (Speci cally, previous equation

are not the same as the t

PLH

max and t

PHL

min, over the

full operating temperature range, speci ed in the data

sheet.) This delay is the maximum value for the propaga-

tion delay di erence speci cation which is speci ed at

450 ns for the ACPL-P456/W456 over an operating tem-

perature range of -40°C to 100°C.

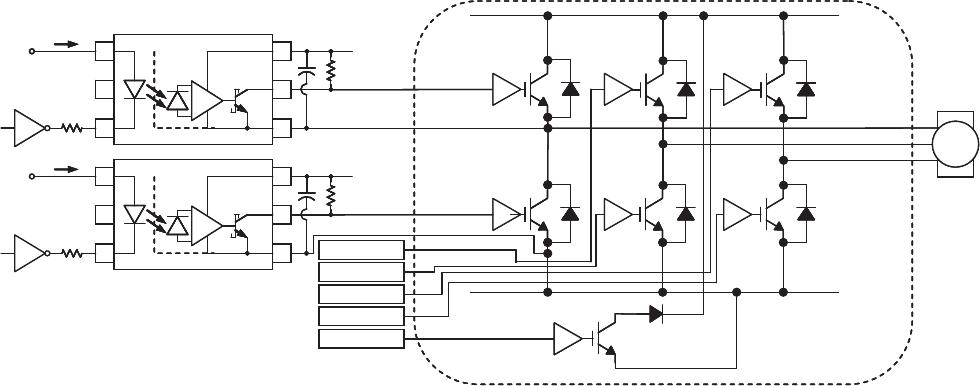

Delaying the LED signal by the maximum propagation

delay di erence ensures that the minimum dead time is

zero, but it does not tell a designer what the maximum

dead time will be. The maximum dead time occurs in

the highly unlikely case where one optocoupler with

the fastest t

PLH

and another with the slowest t

PHL

are in

the same inverter leg. The maximum dead time in this

case becomes the sum of the spread in the t

PLH

and t

PHL

propagation delays as shown in Figure 23. The maximum

dead time is also equivalent to the di erence between

the maximum and minimum propagation delay di er-

ence speci cations. The maximum dead time (due to the

optocouplers) for the ACPL-P456/W456 are 600 ns (= 450

ns - (-150 ns)) over an operating temperature range of -

40°C to 100°C.

M

IPM

+HV

-HV

310 Ω

+5 V

CMOS

0.1 μF

V

CC1

20 kΩ

V

OUT1

61

52

43

SHIELD

I

LED1

310 Ω

+5 V

CMOS

0.1 μF

V

CC2

20 kΩ

V

OUT2

61

52

43

SHIELD

I

LED2

ACPL-P/W456

ACPL-P/W456

ACPL-P/W456

ACPL-P/W456

ACPL-P/W456

MM

-

+5 V

1

2

3

I

LED1

+5 V

3